Изобретение относится к проводной связи и может быть использовано в аппаратуре оконечного оборудования линейного тракта систем связи. Известен кодер совместных кодов высокой плотности, содержащий первый регистр сдвига, два счетных триггера и два элемента совпадения, при этом выход третьего разряда первого регис тра подключен ко входу первого счетного триггера и к объединенным входам элементов совпадения, к двум другим входам которых подключены выходы второго счетного Триггера fQ Однако известное устройство обладает ограниченным быстродействием и низкой помехоустойчивоствю из-за наличия в схеме критических связей и большого числа асинхронных элементов. , Цель изобретения - повышение бысто действия и помехоустойчивости. Поставленная цель достигается тем что в кодер совместимых кодов высокой плотности, содержащий первый регистр сдвига два счетных триггера и два элемента совпадения, причем выход третьего разряда .первого регистра подключен ко входу первого счетного триггера и к объединенным входам элементов совпадения, к двум другимвходам которых подключены выходы второго счетного триггера, введены второй и третий регистры сдвига, при этом управляющий вход второго регистра сдвига объединены с первым входом первого регистра сдвига, ко входу третьего разряда которого и входу третьего разряда третьего регистра сдвига подключен -ВЫХОД первого счетного триггера, а выходы второго регистра сдвига подключены соответственно к информационному входу второго регистра сдвига и управляющим входом первого и третьего регистров сдвига, а выход третьего разряда третьего регистра сдвига подключен ко входу второго счетного триггера.

384

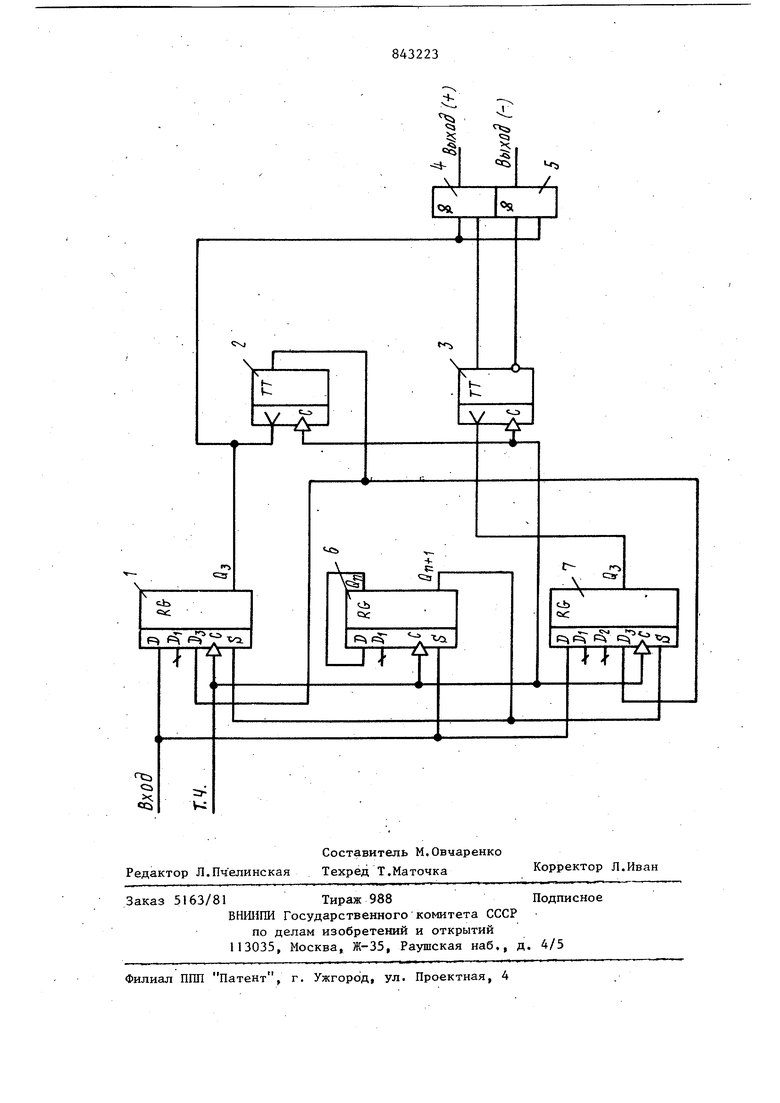

На чертеже представлена схема кодера совместных кодов высокой плотности.

Устройство содержит первый регистр I сдвига, два счетных триггера 2 и 3 два элемента 4 и 5 совпадения, второй 6 и третий 7 регистры сдвига. Выходы элементов 4 и 5 совпадения являются выходами устройства - выходами условно положительных и условно отрицательных импульсов.

Предлагаемое устройство работает следующим образом.

В исходном состоянии во втором регистре 6 в нулевом разряде эаписана единица. Входной информационный сигнал записывается в первом регистре I, третьем регистре 7 и тактовой частото продвигается вправо. Нули.в информационном сигнале, поступая на управляющий вход второго регистра 6, сдвигают единицу из нулевого разряда в первый, второй и т.д. разряды. При поступлении на вход запрещенного числа нулей (в данной схеме запрещены числом нулей подряд три) на выходе второго регистра появляется единица, которая воздействует на управляющие входы первого и третьего регистров

1и 7, переводя их в записи с параллельных входов. Единица на управляющем входе второго регистра 6 также переводит его в режим записи с параллельных входов, т.е. переводит его в исходное состояние. При появлении еди ницы на выходе второго регистра 6 следующим тактом происходит ее запись

в нулевой разряд и цикл повторяется. Для реализации кода СКВП-2 во втором регистре 6 обратная связь берется с выхода второго разряда с тему чтобы к четвертому информационному нулю единица снова бьша в нулевом разряде для повторения цикла.

При переводе регистров 1 и 7 в режим записи с параллельных входов в них записываются единицы по входам первого и второго (только в третьем регистре 7) разрядов и по.входу третьего разряда, если счетный триггер

2находится в состоянии единицы, считывается состояние счетчика.

Таким образом, на выходах первого регистра 1 и третьего регистра 7 появляются сфазированные информационные последовательности с введенными кодовыми вставками, в последовательност третьего регистра 7 при этом введена дополнительная единица.

Счетный триггер 3 меняет свое сое тояние от каждой единицы на выходе третьего регистра 7, переключая. , каждую следующую единицу с первого регистра 1 на выход плюс или выход минус. Дополнительная единица возвращает счетный триггер в предыдущее состояние, тем самым следующая единица повторяет полярность предыдущей.

При основаниях кода, отличных от двух, добавляются разряды во второй регистр 6 и меняется связь с его выхода на вход. Необходимо отметить, что на вход первого разряда первого регистра 1 и входы первого и второго разрядов третьего регистра 7 подаются потенциалы логической единицы.

Таким образом, предлагаемое устройство обладает работоспособностью i высокой помехоустойчивостью до частоты 165 МГц.

Формула изобретения

Кодер coBMecTiibix кодов высокой плотности., содержащий первый регистр сдвга, два счетных триггера и два элемента совпадения, при этом выход третьего разряда первого регистра сдвига подключен ко входу первого счетного триггера и к объединенным входам элементов совпадения, к двум другим входам которых подключены выходы второго счетного триггера, отличающийся тем, что, с целью повышения быстродействия и помехоустойчивости, введены второй п третий регистры сдвига, при этом управляющий вход второго регистра сдвига и информационный вход третьего регистра сдвига объединены с первым входом первого регистра сдвига, ко входу третьего разряда которого и входу третьего разряда третьего регистра сдвига подключен выход первого счетного триггера, а выходы второго регистра сдвига подключены соответственно к информационному входу второго регистра сдвига и управляющим входам первого и третьего регистров сдвига, а выход третьего разряда третьего регистра сдвига подключен ко входу второго счетного триггера.

Источники информации, принятые во внимание при экспертизе

1, Compatibie High Density. Bipoiar Code, - IEEE Transaction Communication Technology. 1970, vol. 18, June № 3 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1988 |

|

SU1580568A1 |

| Телемеханическая система | 1987 |

|

SU1424044A1 |

| Система для передачи и приема информации | 1988 |

|

SU1583953A1 |

| Устройство для передачи и приема информации | 1988 |

|

SU1541651A1 |

| Устройство для коррекции шкалы времени | 1991 |

|

SU1781669A1 |

| Устройство для передачи цифровых сигналов с режимом сжатия | 1985 |

|

SU1277162A1 |

| СПОСОБ И УСТРОЙСТВО РАСПОЗНАВАНИЯ КЛАССОВ СИГНАЛОВ | 1998 |

|

RU2133501C1 |

| Пороговый декодер сверточного кода | 1982 |

|

SU1078654A1 |

| Преобразователь кода | 1989 |

|

SU1709534A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1990 |

|

SU1732380A1 |

Авторы

Даты

1981-06-30—Публикация

1979-04-18—Подача