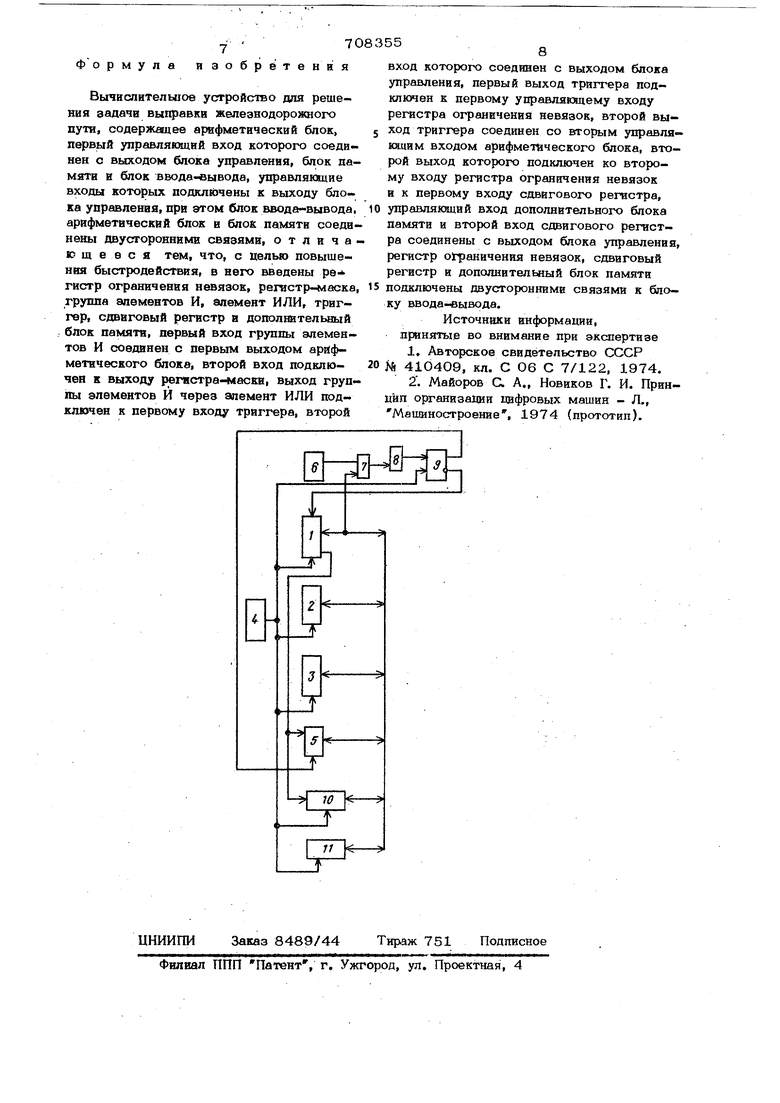

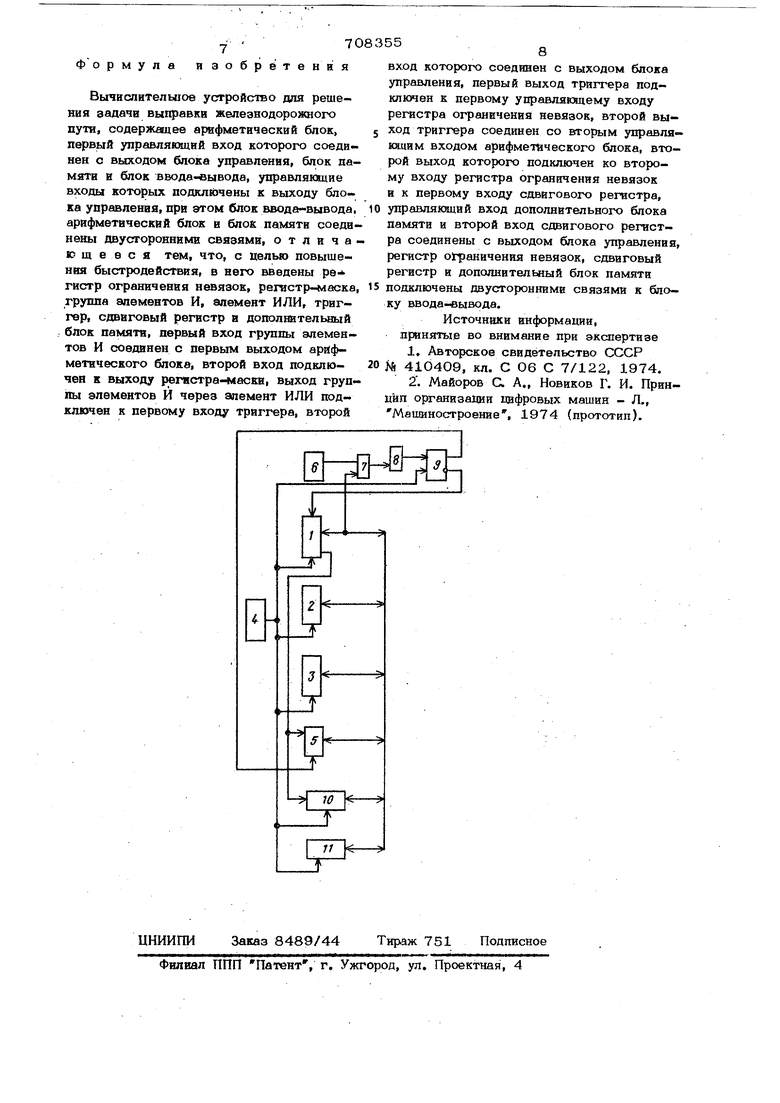

Каждая составляющая вектора X проверяется на допустимость по ограничениям сверху в снизу, т.е. проверяется справед ливость неравенства: . )-, где - Р ,Pi - ограничения на сдвиг K-j Абсолютные значения вычиспенныл суммируются. Накопленная сумма модуле сдвигов А 11 (А (хранится в специальн ячейке блока памяти 2 и используется в дальнейшем при расчете нового вектора невязок 2 который выполняется, если хотя бы одна составляющая Х вектора сдвигов X не удовлетворяет своим ограничениям. Новые невязки вычисляются по формуле;. Л.-.К-1...Л-1 (2J 2. t -1 1 агк ,« И - градиентный множитель, значе ние которого определяется сле дящим выражением: частные производные ректора X по (-ым приращениям вектора Z, которые вычисляются по формулам; L,jBigrHX,,-. 1О bj постоянные коэффициенты матрицы, обратной исходно значения этих коэффициентов могут каждый раз вы чисяяться по подпрограмме, либо храниться в ячей ках ОЗУ. Частные производные (градиенты) вычисляются дважды на каждой HHTepaioik Первый раз - для получения суммы квадратов этих градиентов и градиентов мно- жения Н по формуле (3). Второй раз эти частные производные вычисляются с целью рпределния приращений невязок и новых значений невязок; (S) z -- дzt- v -ll Эти новые значения невязок проверяются на допустимость по ограничениям на невязки, т.е. проверяются условия; Боли какая-либо невязка Z., превышает свое ограничение, она приравнивается 7 5 этому ограничению. Полученные новые значения невязок используются при вычисении нового вектора сдвигов X. на (V+l)-oft интерации. Процесс 1.линимиза1ши вектора X длится до тех пор, пока не будет найдено первое решение, удовлетворяющее заданной системе неравенств. Прототипу присущ следующий недостаток: большие затраты времени на решение задачи нелинейного программирования с двусторонним ограничениями на зависимые и независимые переменные, вызванные необходимостью многократно (на каждой итерагми) проверять каждую вычисленную переменную, ее допустимость по ограничениям сверху и снизу. Целью предлагаемого изобретения является повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство дополнительно введены регистр ограничения невязок, регистр-маска, группа элементов И, элемент ИЛИ, триггер, сдвиговый регистр и дополнительный блок памяти, первый вход груш1ы элементов И соединен с первым выходом арифметического блока, второй вход подключен к выходу регистра-маски, выход группы элементов И через элемент ИЛИ подключен к первому входу триггера, второй вход которого соединен с выходом блока управления, первый выход триггера подключен к первому управлякяцему входу регистра ограничения невязок, второй вход триггера соединен со вторым управлякяцим входом арифметического блока, второй выход которого подключен ко второму входу регистра ограничения невязок и к первому входу сдвигового. регистра, управляющий вход дополнительного блока памяти и вто- рой вход сдвигового регистра соединены с; выходом блока управления, регистр ограничения невязок, сдвиговый регистр и дополнительный блок памяти подключены двусторонними связями к блоку ввода-вывода. На чертеже представлена схема устройства. Оаа содержит: арифметический блок 1, блок памяти 2, блок ввода-вывода 3, блок управления 4, регистр ограничения невязок 5, регистр-маску 6, группу элементов И 7, элемент ИЛИ 8, триггер 9, сдаиговый регистр 10, дополнительный блок памяти 11. Предлагаемое устройство работает следующим образом. В процессе ввода в регистры блока памяти 2 из блока ввода-вывода 3 ааносится информация об ограничениях на сдви ги в соответствующих точках деления пути и о свободных членах неравенства решаемой системы, вычисляемых во время ввода как функции стрел кривизны в точках деления пути. В регистр ограничения 5 заносится код, соответствующий абсолютной величине ограничения на невязки Z; системы линейных неравенств, В регистр-маску 6 заносится код, содержащий нули в младших разрядах; число таких разрядов обусловлено максимально допустимым значением невязок, определен ными условиями решаемой задачи, В остальные разряды регистра-маски 6 заносятся единицы. Выходы регистра-маски 6 заведены на вторые входы группы элементов И 7, первые входы которых соединены с соответствующими выходами арифметического блока 1. Таким образом, регистр-маска 6 маскирует нулями некоторое множество младших разрядов арифметического блока 1. Поэтому единица на выходе любого замаскированного разряда арифметического блока 1 не проходит через группу эле ментов И 7. Единицы с выхода любого из :старших разрядов, незамаскированных регистром-маской 6, прохоядт через группу элементов И7 на вход элемента ИЛИ 8. Таким образом, если в процессе вычисления невязки ее значение превышает установленное ограничение, то, по крайней мере, в одном из незамаскированных старших разрядов арифметического блока 1 появится единица, которая пройдет на вход элемента И Ли 8. На выходе этой схемы появится управляющий сигнал, который переключает триггер 9 в единичное состояние. При этом информация об абсолютном значении невязки поступит в блок памяти 2 из регистра ограничения невязки 5. Информация о знаке невязки 1.: по ступает на вход знакового разряда регистра 5 непосредственно с выхода знако вого разряда арифметического блока 1. Триггер 9 перед началом вычисления очередной невязки предварительяо устанавливается в состояние О управляющим сиг налом на соответствукяцем выходе блока управления 4. По завершении процесса ввода информации начинается вычисление вектора сдвигов X ).При этом начально значение вектора невязок Z° принимается равным нулю. В процессе вычисления сдвигов Х в соответствующей ячейке блока памяти 2 накапливается сумма модулей величины информация о знаках величин Х за- HoaiTCH в сдвиговый регистр знаков 10, Эта информахшя используется в дальнейшем при вычислении нового вектора невязок Z. Каждый вычислительный сдвиг X;j проверяется на допустимость по ограничениям сверху и снизу путем последовательного сравнения вычисленной величины Х с числами, расположенными в соответствующих регистрах блока памяти 2. При получении первого значения , не удовлетворяющаго заданным ограничениям, проверка последующих Х не производится, а по окончании вычисления всего вектора X и накопления суммы модулей Х начинается процесс вычисления нового вектора невязок как функции от знаков величины сдвигов, хранящихся в сдвнговом регистре 10. Введение сдвигового регистра 10 позволяет значительно ускорить процесс вычислений невязок, значения знаков сдвигов поступают с выхода сдвигового регистра 10 синхронно с выдачей из дополнительного блока памяти 11 коэффициентов формулы для вычисления. Невязки Z.J ВЫЧИСЛЯЮ ,н как функции от суммы коэффициентов U , абсолютные значения которых хранятся в дополнительном блоке памяти 11 и от суммы модулей сдвигов . Знаки коэффициентов U определяются знаками сдвигов Х{, хранящихся в сдвиговом регистре 10. Значения невязок 2. , лежащих в рамках выбранных ограничений, поступают в блок памяти 2 из арифметического блока 1. Если же значение какой-либо невязки пре- вьпиает ограничение, то в блок памяти 2 записывается код, зафиксированный в ре-« гистре ограничения невязок 5. Предлагаемая совокупность дополнительных аппаратных средств и связей между ними позволяет достичь значительного ускорения процедуры рещения системы лиHe iHX неравенств с двухсторонними ограничениями на зависимые и независимые переменные обобщенным градиентным методом. Это даст принципиальную возможность использовать предлагаемое устройство в качестве бортового вычислителя, , обеспечивающего качественное решение задачи выправки железнодорожного пути в реальном масштабе времени работы путерихтовочного комплекса.

Формула изобретения

Вычнспительиов устройство для решения задачи выправке железводорохшого пути, оодержадее арифметический блок, первый управляквцнй вход которого соединен с выходом блока управления, блок памяти и блок ввода««ывода, управляющие входы которых подключены к выходу блока управления, при этом блок ввода-вывода, арифметический блок и блок памяти соединены двусторонними связями, отличающееся тем, что, с целью повышения быстродействия, в него введены ре- гистр ограничения невязок, регистр-чм1аска, группа элементов И, элемент ИЛИ, триггер, сдвиговый регистр и дополнительный блок памяти, первый вход группы элементов И соединен с первым выходом ар1 фметического блока, второй вход подключен к выходу {югнстра-маски, выход группы элементов И через элемент ИЛИ подключен к первому входу триггера, второй

вход которого соединен с выходом блока управления, первый выход триггера подключен к первому управлякяцему входу регистра ограничения невязок, второй вы-

ход триггера соединен со вторым управля- кадим входом арифметического блока, второй выход которого подключен ко второму входу регистра ограничения невязок и к первому входу сдвигового регистра,

улравляклций вход дополнительного блока памяти и второй вход сдвигового регистра соединены с выходом блока управления, регистр ограничения невязок, сдвиговый регистр и дополнительный блок памяти

одключены двусторонними связями к блоку ввода-вывода.

Источники информации, принятые во внимание при экспертизе 1, Авторское свидетельство СССР

410409, кл. С 06 С 7/122, 1974.

2. Майоров С. А., Новиков Г. И. Принип организации цифровых машин - Л., Машиностроение, 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство для решения задачи выправки железнодорожного пути | 1978 |

|

SU886004A1 |

| Вычислительное устройство для решениязАдАчи ВыпРАВКи жЕлЕзНОдОРОжНОгО пуТи | 1977 |

|

SU802967A2 |

| Многоканальное устройство дляРЕшЕНия СиСТЕМ лиНЕйНыХ АлгЕбРАичЕС-КиХ уРАВНЕНий | 1978 |

|

SU807318A1 |

| Устройство для решения линейных систем алгебраических уравнений | 1985 |

|

SU1325464A1 |

| Устройство для решения систем алгебраических уравнений | 1986 |

|

SU1324036A1 |

| Устройство для решения интегральных уравнений Фредгольма второго рода | 1988 |

|

SU1617438A1 |

| Устройство для решения интегральных уравнений Фредгольма второго порядка | 1985 |

|

SU1295413A1 |

| Устройство для решения интегральных уравнений Фредгольма | 1982 |

|

SU1108444A1 |

| Арифметическое устройство | 1978 |

|

SU746508A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ КОДОВ РИДА-СОЛОМОНА | 2010 |

|

RU2441318C1 |

Авторы

Даты

1980-01-05—Публикация

1977-07-21—Подача