Изобретение относится к вычислительной технике и предназначено для решения интегральных уравнений Фред- гольма второго рода.

Цель изобретения - расширение класа решаемых задач за C4et увеличения допустимого диапазона изготовления численного параметра уравнения.

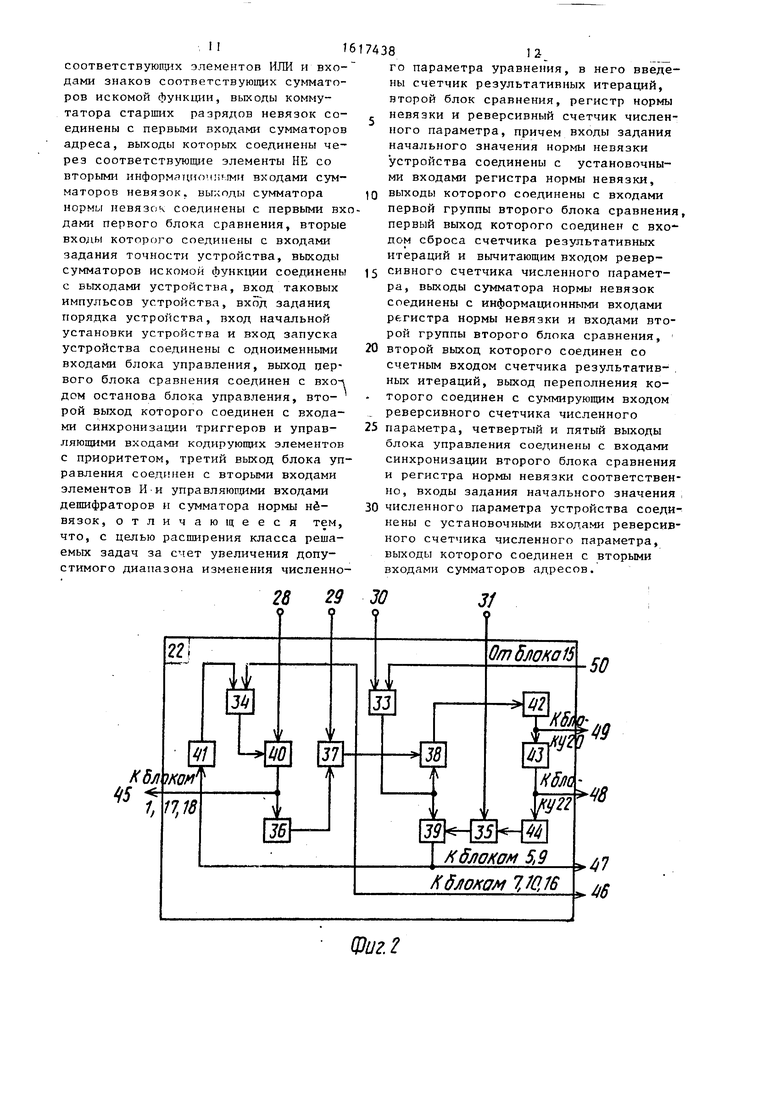

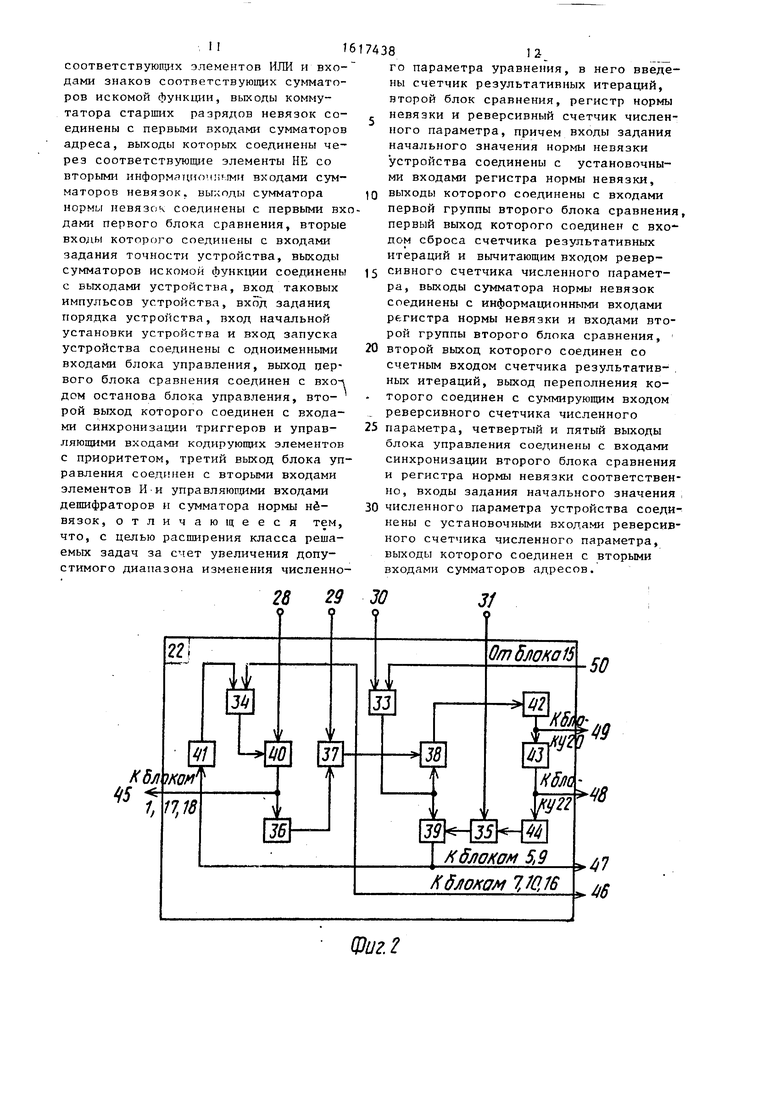

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг. 2 схема.блока управления.

Предлагаемое устройство содержит п генераторов 1 функций, п блоков 2 сдвига, п групп элементов ИЛИ 3, п сумматоров 4 невя зок, п кодирующих элементов 5 с приоритетом, п регистров 6 старших разрядов невязок, п дешифраторов 7, п сумматоров 8 исковой функции, п триггеров 9, п элементов И 10, п элементов ,НЕ 11, п сумматоров 12 адреса, п элементов ИЛИ 13, реверсивный счетчик 14 численного параметра, первый блок 15 сравнения, сумматор 16 нормы невязок коммутатор J7 знаков невязок,коммутат

18старших разрядов невязок, счетчик

19результативных итераций, второй блок 20 сравнения, регистра 21 нормы невязок, блок 22 управления, вход 23 задания численного параметра устройства, вход 24 задания точности устройства, п входов 25 задания на-

0

5

с

0

5

0

чального значения искомой функции устройства, п входов 26 задания начальных значений невязок устройства, вход 27 задания начального значения нормы невязок устройства, вход 28 тактовых импульсов устройства, вход

29задания порядка устройства, вход

30начальной.установки устройства, вход 31 запуска устройства и п выходов 32 устройства.

Блок 22 управления содержит первый 33 и второй 34 триггеры, элемент ИЛИ 35, счетчик 36, узел 37 сравнения, первый 38, второй 39 и третий 40 элементы И, первый 41, второй 42, третий 43 и четвертый 44 элементы задержки, первый 45, второй 46, третий 47, четвертый 48 и пятый 49 вы- ходы блока управления, первый 50 вход блока управления, второй, третий, четвертый и пятый входы блока 22 уп-; равления являются соответственно входом 28 тактовых импульсов, входом 29 задания порядка, входом 30 начальной установки и входом 31 запуска устройства.

В предлагаемом устройстве реализуется модифицированный метод последовательных приближений. Приращение функции на k-й итерации вычисляется по следующей формуле:

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения интегральных уравнений Фредгольма | 1982 |

|

SU1108444A1 |

| Устройство для решения интегральных уравнений Фредгольма второго порядка | 1985 |

|

SU1295413A1 |

| Многоканальное устройство для реше-Ния иНТЕгРАльНыХ уРАВНЕНий | 1979 |

|

SU840921A1 |

| Устройство для решения интеграль-НыХ уРАВНЕНий | 1979 |

|

SU817726A1 |

| Устройство для решения систем линйныхАлгЕбРАичЕСКиХ уРАВНЕНий | 1978 |

|

SU824217A1 |

| Устройство для решения систем ли-НЕйНыХ уРАВНЕНий | 1978 |

|

SU813446A1 |

| Устройство для решения систем линейных дифференциальных уравнений | 1985 |

|

SU1252792A1 |

| Резервированное устройство для решения интегральных уравнений | 1981 |

|

SU1092511A1 |

| Вычислительное устройство для решения задачи выправки железнодорожного пути | 1978 |

|

SU886004A1 |

| Устройство для решения системлиНЕйНыХ уРАВНЕНий | 1979 |

|

SU830396A1 |

Изобретение относится к вычислительной технике и предназначено для решения уравнений Фредгольма второго рода. Цель изобретения - расширение класса решаемых задач за счет увеличения допустимого диапазона изменения численного параметра уравнения. Устройство содержит генераторы 1 функций, блоки 2 сдвига, группы 3 элементов ИЛИ, сумматоры 4 невязок, кодирующие элементы 5 с приоритетом, регистры 6 старших разрядов, дешифраторы 7, сумматоры 8 искомой функции, триггеры 9, элементы И 10, элементы НЕ 11, сумматоры 12 адреса, элементы ИЛИ 13, реверсивный счетчик 14 численного параметра, первый блок 15 сравнения, сумматор 16 нормы невязок, коммутатор 17 знаков невязок, коммутатор 18 старших разрядов невязок, счетчик 19 "результативных" интераций, второй блок 20 сравнения. 2 ил.

iY(Xj) (llK-(U., (X;) Sign e,(X;);

р,, если ±/е,(Х;)/.; ±/...СХ;)/; . ,

(kt. (х Ч . 2:/fic(x;),.,(X;)/;

;(

|и„ q , если (U (И i., / к-г k-t

(1.и (х;) qen ie42oH/ K-,(;)/}

где

k

q

1;

. ,n .

основание системы счислния, принятой в устройстве;

С).,(Х;) значение невязки на (и-1)-й итерации.

6,(Х;) 6,.,(Х;)- АУ,(Х;) - (X ;S;)-UY..(S.), - J J

где K(X Sj) - ядро интегрального урнения - известная фунция}L - численный параметр

уравнения j

h - шаг интегрирования. На- первой итерации, как и в прототипе, приращение искомой функции в 1-й точке равно по величине старшему разряду (обозначим его адрес чере Ij) невязки, полученной на предыдущей итерации в той же точке, а знак приращения определяется знаком этой невязки. Затем алгоритм вычислит-ель- ного процесса изменяется. На каждой итерации вычисляется норма незязок - сумма модулей невязок, которая сравнивается с нормой невязок, полученной на предыдущей итерации. В зависимости от результата сравнения величина приращения искомой Лункгши на следующей итерации либо тоже равна величине старшего разряда невязки (выполненная итерация считается результативной, она приблизила значение искомой функции к конечному результату - решению интегрального уравнения) , либо старший разряд невязки уменьшен на один разряд (значение искомой функции на текущей итерации оказалось дальше от решения, чем на предьщущей, или не приблизилось к нему - итерация нерезультативная). Ели t последовательных итераций оказались результативными, то для ускорения вычислительного процесса старш разряд невязки на следующей итерации увеличивается «а один разряд (оптимальное значение t для разных классов задач находится в пределах 4-8 и задается разрядностью счетчика 19 результативных итераций).

В любом случае приращение функции всегда остается величиной, кратной основа {ию q системы счисления, при

10

нятой в устройстве, поэтому при вы-, числении невязки вместо операции ум- ножения значений ядра на приращение функции выполняется операция сдвига значений ядра на соответствующее число разрядов. Учитывая, что шаг интегрирования h выбирается таким образом, чтобы произведение Lh q гдет- целое положительное число, причем (р разрядность представления чисел в устройстве). Вместо операции умножения выражения, стоящего под знаком суммы в формуле невязки, на Lh-,производится сдвиг его на m разрядов вправо - в сторону уменьшения.

Итерационный процесс заканчивается, если выпополняется условие

21/е,(Х;)

15

20

где г - заданная точность решение

интегрального уравнения.

Предлагаемое устройство работает

следующим образом.

Перед началом работы начальное приближение функции V(,(X,) О по входам 25 заносится в сумматоры 8 искомой функции, а соответствующее

ему значение невязок (Х;)

f(X;) (f(X;) - правая часть интегрального уравнения - известная фур1кция) по входам 26 - в сумматоры 4 невязок. В зависимости от класса

решаемых задач счетчик 19 результативных итераций принимается двух-, трех и т.д. -разрядным. Таким образом задается величина t. На вход 23 задания численного параметра устройства пода ется значение т, определяемое из соотношения Lh q-, на вход 24 задания точности устройства - значение заданной точности г, на вход 28 тактовых импульсов устройст- ва - тактовые импульсы, на вход 29 : задания порядка устройства - значение порядка п. На вход 27 задания начальной нормы невязок устройства

подается значение Е (Х;)/ .

i.

Затем на вход 30 начальной уста- новки устройства подается сигнал Начальная установка, а на вход 31 запуска устройства - сигнал Запуск, после чего начинается работа устройства.

При выполнении очередной k-й итерации по сигналу блока 22 управления кодирующие элементы 5 с приорите

том выделяют адреса старших разрядов li соответствующих невязок, вычисленных на (k-l)-ft итерации, которые i заносятся для хранения в регистры 6 старших разрядов невязок, а с них поступают на группу входов коммутатора 18 старших разрядов невязок, триггеры 9 выделяют знаки тех же невязок, которые поступают на группу входов коммутатора 17 знаков невязок и на информационные входы элементов И 10. Затем блор 22 управления вьщает последовательно п сигналов на входы генераторов 1 функции и управляющие входы коммутаторов 17 и 18 знаков невязок и старших разрядов невязок. При этом адреса старших разрядов Ij всех невязок последовательно поступают на первые входы сумматоров 12 сдвига, на вторые входы которых поступает величина, хранящаяся в реверсивном счетчике 14. На первой итерации - это значение т, на последующих - уточненное в соответствии с алгоритмом значение tn m |li|. Полученная в сумматорах 12 сумма т + Ij подается на управляющие входы блоков 2 сдвига. Генераторы 1 функции выдают

последовательно по словам, параллель- JQ который останавливает работу устрой- но по разрядам значения ядер K(X, S ), ства. При Е | г сигнал с выхода

которые через блоки 2 сдвига, где про исходит сдвиг K(X, Sj) на Ij разрядов вправо, и группу элементов ИЛИ 3 поступают на первые информационные входы сумматоров 4 невязок, где они складываются или вычитаются в зависимости от знака невязок 6 (i., (Xj ) , которые последовательно поступают с

блока 15 сравнения не поступает. Вычисленная норма Е невязок поступает также в блок 20 сравнения норм невязок, куда подается норма невязок, полученных на предыдущей итерации, хранящаяся в регистре 21 нормы невязок. По сигналу с блока 22 управления в блоке 20 сравнения вычисляется разность (, . Если она окажется отрицательной, то итерация считается результативной. Сигнал с выхода блока 20 поступает в счетчик 19 результативных итераций. При поступлении t последовательных сигналов происходит переполнение счетчика 19f сигнал с его выхода поступает на реверсивный счетчик 14, где хранится величина т,. При этом вычитается еди

выхода коммутатора 17 знаков невязо с через элементы ИЛИ 13 и элементы НЕ (знак меняется на противоположный) на вторые информационные входы сумматоров 4 невязок. Так1Ш образом в сумматорах 4 невязок вычисляются ве- личины

п (X;Sj) AYjSj),

которые складываются с величинами не вязок f.,(X;), хранящимися в тех же сумматорах. После этого блок 22 управления выдает сигнал на де: В 1фра- торы 7, элементы И 10 и сумматор 16 нормы невязок. С выхода дешифраторов 7 величины старших разрядов невязок б(.,(Х;) поступают в сумматоры 8 искомой функции, туда же поступают зна ки невязок, т.е. в сумматоры 8 по

даются приращения функции UY(X; ). В сумматорах 8 приращения фнукции складываются со значениями функции, полученными на предыдущей итерации. Таким образом реализуется основная формула итерационного процесса:

Y(x;) Y (х;) + AY,(X;).

0 Величины приращений функции с выхода дешифраторов 6 поступают также через группу элементов ИЛИ 3 на сум-; маторы 4 невязок, знаки этих приращений с выхода блоков И 10 тоже по5 ступают на сумматоры 4 невязок через элементы ИЛИ 13 и элементы НЕ 11. Этим достигается получение на выходах сумматоров 4 невязок значений невязок SK;(XJ), которые поступают

0 на сумматор 16 нормы невязки, где происходит вычисление нормы невязоц Е 1 ,()| . Эта величина сравi iнивается в блоке 15 сравнения с ве5 личиной г, которая характеризует

точность решения интегрального уравнения. Если , процесс счета заканчивается. С выхода блока 15 сигнал поступает в блок 22 управления.

Q который останавливает работу устрой- ства. При Е | г сигнал с выхода

0

блока 15 сравнения не поступает. Вычисленная норма Е невязок поступает также в блок 20 сравнения норм невязок, куда подается норма невязок, полученных на предыдущей итерации, хранящаяся в регистре 21 нормы невязок. По сигналу с блока 22 управления в блоке 20 сравнения вычисляется разность (, . Если она окажется отрицательной, то итерация считается результативной. Сигнал с выхода блока 20 поступает в счетчик 19 результативных итераций. При поступлении t последовательных сигналов происходит переполнение счетчика 19f сигнал с его выхода поступает на реверсивный счетчик 14, где хранится величина т,. При этом вычитается едиК

0

5

ница из т,, что влечет за собой увеличение прираш.ения функции на один разряд на следующей итерации. Если разность Е , - Е, оказывается поло- жителъной или равной нулю, то сигнал с другого выходя блока 20 поступает в счетчик 19 результативных итераций - происходит сброс его в ноль, и на реверсивный счетчик 14. При этом добавляется единица к его содержимому.

916

что приводит к уменьшению TOK и приращению функции на один разряд на следующей итерации. После этого по сигналу блока 22 управления в регистр 21 нормы невязок заносится очередное значение Е;, и на этом заканчивается очередная итерация. После выполнения k-й итерации в сумматорах 8 искомой функции содержатся значения функции Y|.,(X{), которые подаются на выходы 32 устройства, а в сумматорах 4 невязок - значения соответствующих невязок K(XJ). Последующие итерации выполняются аналогично.

В блоке 22 управления сигнал Начальная -установка по входу 30 устанавливает первый триггер 33 в состо- яйие, открывающее первый 38 и второй 39 элемент И, подготавливая схему к работе. Сигнал Запуск (начало первой итерации) по входу 31 через элемент ИЛИ 35 и второй элемент И 39 поступает по выходу 47 на управляющие входы кодирующих элементов 5 с приоритетом и триггеров 9. Через первый элемент 41 задержки задержанный сигнал поступает на второй триггер 34 который открывает третий элемент И 40 При этом тактовые импульсы с входа 28 устройства через,третий элемент И 40 поступают по выходу 45 на входы генераторов 1 функций и управляющие входы коммутаторов знаков 17 невязок и старших разрядов 18 невязок до тех пор, пока узел 37 сравнения, который сравнивает величину порядка, поступающую с входа 29 задания порядка устройства, с количеством поступивших на счетчик 36 импульсов, не вьща- ет сигнал на второй триггер 34, который закрывает третий элемент И 40, прекращая подачу импульсов. Сигнал с узла 37 сравнения по выходу 46 поступает на управляющие входы дешифраторов 7, элементов И 10, сумматора 16 нормы невязки. Задержанный сигнал через открытый первый элемент И 38 и второй элемент 42 задержки по выходу 49 поступает на управляющий вход блока 20 сравнения. Через третий элемент 43 задержки задержанный сигнал по выходу 48 поступает на управляющий вход регистра 21 нормы невязки. Через четвертый элемент 44 задержки сигнал поступает на элемент ИЛИ 35, начиная следующую итерацию и т.д. После достижения заданной точности :рещения интегрального уравне43810

ния блок 24 сравнения пьщает сигнал, поступающий через вход 49 на первый триггер 33, который запирает первый 38 и второй 39 элементы И, останавливая работу блока управления и всего устройства.

Формула изобретения

Устройство для решения интеграль- ных уравнений Фредгольма второго рода, содержащее п генераторов функций (п - число точек, в которых оп- ределяется искомая функция), п блоков

5 сддига, п сумматоров невязок, п триггеров, коммутатор знака невязок, блок управления, п групп элементов ИЛИ, п кодирующих элементов с приоритетом, п регистров старших разрядов невязок, п дешифраторов, п сумматоров искомой функции, п сумматоров адреса, п элементов И, п элементов ИЛИ, первый блок сравнения, сумматор нормы невязок, п элементов НЕ,

5 коммутатор старших разрядов невязок, причем первый выход блока управления соединен с управляю11р1ми входами коммутатора знаков невязок и сумматора невязок, а также с входами всех ге0 нераторов функций, выходы которых соединены с информационными входами соответствующих блоков сдвига, выходы каждого из которых соединены с первыми входами элементов ИЛИ соответствующей группы, выходы которых соединены с первыми информационными входами соответствующих сумматоров невязок, информационные выходы которых соединены с информационными входами

Q сумматора нормы невязок и соответствующих . кодирующих элементов с приоритетом, выходы которых соединены с входами соответствукицих регистров старших разрядов невязок, выходы ко, торых соединены с информационными входами коммутатора старших разрядов невязок и соответствующих дешифраторов, выходы которых соединен с вторыми входами элементов ИЛИ соответстп вующей группы и информационными входами соответствующих сумматоров искомой функции, выходы знаков сумматоров невязок соединены с информационными входами соответствующих тригге- ров, выходы которых соединены с информационными входами коммутатора знаков невязок и первыми входами соответствующих элементов И, выходы которых соединены с первыми входами

5

5

II 1

соответствующих элементов ИЛИ и входами знаков соответствующих сумматоров искомой функции, выходы коммутатора старших разрядов невязок соединены с первыми входами сумматоров адреса, выходы которых соединены через соответствующие элементы НЕ со вторыми информациоинмми входами сумматоров невязок, выходы сумматора нормы иевязок соединены с первыми вх дами первого блока сравнения, вторые входы которого соединены с входами задания точности устройства, выходы сумматоров искомой функции соединены с Бькодами устройства, вход таковых импульсов устройства, вход задания порядка устройства, вход начальной установки устройства и вход запуска устройства соединены с одноименными входами блока управления, выход первого блока сравнения соединен с вхо дом останова блока управления, второй выход которого соединен с входами синхронизации триггеров и управляющими входами кодирующих элементов с приоритетом, третий выход блока управления соед1 нен с вторыми входами элементов И-и управляюп ими входами дешифраторов и сумматора нормы невязок, отличающееся тем,

что, с целью расширения класса реща- емых задач за счет увеличения допустимого диапазона изменения численноП

28 29 30

743812,

го параметра уравнения, в него введены счетчик результативных итераций, второй блок сравнения, регистр нормы , невязки и реверсивный счетчик численного параметра, причем входы задания начального значения нормы невязки устройства соединены с установочными входами регистра нормы невязки,

)0 выходы которого соединены с входами первой группы второго блока сравнения, первый выход которого соединен с входом сброса счетчика результативных итераций и вычитающим входом ревер5 сивного счетчика численного параметра, выходы сумматора нормы невязок соединены с информационными входами регистра нормы невязки и входами второй группы второго блока сравнения,

20 второй вькод которого соединен со счетным входом счетчика результативных итераций, выход переполнения ко- торого соединен с суммирующим входом

реверсивного счетчика численного

5 параметра, четвертый и пятый выходы блока управления соединены с входами синхронизации второго блока сравнения и регистра нормы невязки соответственно, входы задания начального значения

0 численного параметра устройства соединены с установочными входами реверсивного счетчика численного параметра, выходы которого соединен с вторыми входами сумматоров адресов.

31

| Устройство для решения интегральных уравнений | 1978 |

|

SU687452A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-12-30—Публикация

1988-12-05—Подача