Изфбретение относится к цифровой вычислительной технике и может применяться в составе арифметических устройств цифровых вычислительных машин. « Известны арифметические устройства, предназначенные для решения, задач с большим числом тригонометрических функций, содержащие сдвиговые регистры, сумматоры-вычитатели и , мутирующие блоки 1. Недостатком устройств является отсутствие в их наборе операции вычисления произведения двух двоичных чисел за одну операцию. ; Наиболее близким по технической сущности к предлагаемому является арифметическое устройство, реализующее алгоритм Волдера YUi-V,;-X,. Х,., Х,, Y. , д) и позволяющее вычислять (Yj со5Я Х5нпЛ), X K X COSЛ-Y S nЛ), - ,9 QPctg-, гд ,цл oC К 3, ус а ус пр Xj,У;, 9 - .значения координа и угла на 1-й итеиаиии I . - функция, пбказывгийщая направление вращения и равная для соотношений (2) . E; -5Hgn0V оотношений (3) (-Y;) угловая постоянная, равная ,afctg2 V коэффициент общего удлинения вектора, равный произведению коэффициентов удлинения на каждой итерации . К.П . i2 i t У 7 Л - начальные данные; i - номер итерации 1 2, г и решении соотношений (2) и (3) ойство работает по cuiropHTMy(1), и вычислении (значения х ойстве организуется итерационный ессW ,. .i , 2.,-2..,:2:,.2-, где Xp X (05 i 1 /X / 1) ; i - номер итерации, i 1, 2, 3, ,..I n; - оператор, придающий такое изменение X, чтобы при n значение Kf( - l,Zn- ,Z и равный i. -i, Zj- значение.обратной величины на i-и итёрацйй (2.о 1 при X О и Z о 1 при X 0). Арифметическое устройство содержит три сдвиговых регистра, два коммутиру ющих блока, три сумматора-вычитателя и элемент И, причем разрядные выходы первого и второго сдвиговых регистров соединены с соответствующими входаШ соответственно первого и второto коммутирующих блоков, управляквдие входы которых поДключенй к пёрвЬму уп равляющему входу устройства, выходы .младших раэрядов каждого из сдвиговых регистров подключены к первым входам соответствующих сумматоррв-вычитателей, BiiKOjcsf кЬт6{5Ш: ивляются выходами устройства, и подключены к входам старших разрядов соответствующих сдви говых регистров и ко второму, третьему и четвертому управляющим входам устройства, второй вход пёрвого ЬУМматора-вычитателя соединен с выходом элемента И, первый вход под ключен к, выходу второго коммутирующего блока, а второй вход - к запрещающему входу устройства, управляющие входы первого и третьего сумматороввычитателей соединены с пятым управляющим входом устройства, второй вход третьего сумйатора-вычитателя подключен к первому разрешамщему ВХОДУ устройства f2J . ; . . Однако структура такого устройства не приспособлена для вычисления произведения двух двричных чисел за одну Операцию. . . : , - ..„,;„.--,-, изобретения является расширение функциональных возможностей арифыгё и:чёского устройства за счет . йычйспеййя произведения двух двоич;ных чисел за одну операцию , .Поставленная цель достигается тем что в арифметическое устройство, соде|)жащёе три сдвйговых perncfipaV два коммутирхющих блока, три сумматора1вычитателй и элемент И, разрядные вьЛходы первого и второго Ьдвиговьрс регистров соединены с соответст вующими входами соответственно первого и второго коммутируёилх блоков, управляющие входы которых подключены к первому управляющему устройст ва, выводы Мпадййх разрядов каждого из сдви1чэвых регистров подключены к. первым входам соответствующих суилато 5ов-вычислйтелей, выходы которых являются выходгсми устройства и подключены, к входам старших разрядов со

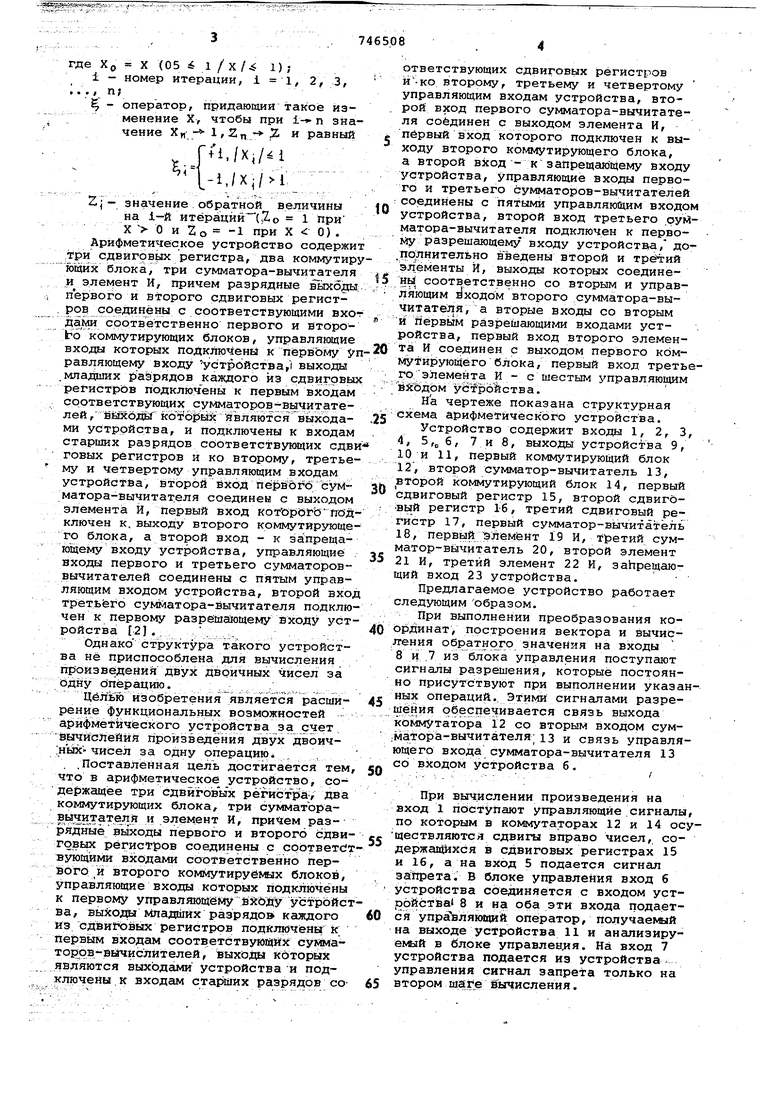

746508 ответствующих сдвиговых регистров и-ко второму, третьему и четвертому управляющим входам устройства, второй вход первого сумматора-вычитателя соединен с выходом элемента И, пбрвый вход которого подключен к выходу второго коммутирующего блока, а второй вход - к запрещающему входу Стройства, управляющие входы первого и третьего сумматоров-вычитателей соединены с пятыми управляющим входом устройства, второй вход третьего ,румматора-вычитателя подключен к первому разрешающему входу устройстВга, доп:сшнитеяьно введены второй и третий элёменты И, выходы которых соединены соответственно со вторым и управляющим Уходом второго сумматора-вычитатедя, а вторые входы со вторым и первым разрешающиг ш входами устройства, первый вход второго элемента И соединен с выходом первого кбм лутирующёго блока, первый вход третьего элемента И - с шестым управляющим SSfefloM yc ipbl&cTBa. На чертеже показана структурная схема арифме йчёск6го устройства. Устройство содержит входы 1, 2, 3, 4, 5,„ б, 7 и 8, выходы устройства 9, 10 и 11, первый коммутирующий блок 12, второй сумматор-вычитатель 13, второй ког о тирующий блок 14, первый сдвиговый регистр 15, второй сдвиговый регистр 16, третий сдвиговый регистр 17, первый сумматор-вычитатель 18, первый ЗЯемёнт 19 И, третий сумматор-вычитатель 20, второй элемент 21 И, третий элемент 22 И, заНрещающий вход 23 устройства. Предлагаемое устройство работает следующимобразом. При выполнении преобразования координат, построения вектора и вычисл-ения обратного значения на входы 8 и .7 из блока управления поступают сигналы разрешения, которые постоянно присутствуют при выполнении указанных операций.. Этими сигналами разрешения обеспечивается связь выхода кок1мутатора 12 со вторым входом сум.мэЗРОра-вычитателя; 13 и связь управляющего входа сумматора-вычитателя 13 со входом устройства 6. При знгч.ислении произведения на вход 1 поступают управляющие.сигналы, по которым в коммутаторах 12 и 14 осуществляготсд сдвигы вправо чисел, содержа14йхся в сдвиговых регистрах 15 и 16, а на вход 5 подается сигнал зайрета. В блоке управления вход б Устройства соединяется с входом устройства 8 и на оба эти входа подается упраЪляюйий оператор, получаемый на выходе устройства 11 и анализируемый в блоке управлен.ия. На вход 7 устройства полается из устройства управления сигнал запрета только на втором шаге вычисления. В исходном состоянии множимое А содержится в сдвиговом регистре 15, множитель В - в сдвиговом регистре 17 а сдвиговый регистр 16 находится в нулевом состояний. В процессе вычисления в сдвиговом регистре 16 происходит накопление сдвинутых множимах и в конце вычисления содержится окончательный результат. При пбдаче на вход 5 сигнала Зап рет , на второй вход сумматораЧвычйтателя 18 с выхода элемента И 19 поступает сигнал, равный нулю. Благодаря этому множимое Л, поданноена вход 2, в процессе вычисления сохраняется в сдвиговом регистре 15 неизменным при установках сумматора-вычитателя 18 как на сложение, так и на вычитание. Управляющий оператор устанавливает сумматор-вычитатель 13 на противоположное действие по сравнению с сумматорами-вычитателями 18 и 20. Вычисление произведения Z А В выполняется за (п + 1) шагов, где И - число разрядов в сдвиговых регист рах арифметического устройства. На первом шаге проверяется знак ; умножителя В. Из устройства управления на управляющие входы 6 и 8 поступает сигнал запрет.а. Этот сигнал закрывает элемент. 21 И и 22 И и устанавливает сумматор-вы1йтатель 20 на сложение. На второй вход су№ атора-вычитателя 13 поступает О, сдвиговый регистр 16 при выполнении первого шага продолжает сохранять нулевое состояние, значение сигнала на входе 7 устройства при выполнении первого шага безразлично. На вход 7 устройства из блока памяти поступает константа 2, которая суммируется сумматором- вычитателём .20 с множителем В, находящимся в сдви jTOBOM регистре 17. На выходе 11 сумматора-вычитателя 20 образуется сумм Bi В + 2°, которая вновь засылается в сдвиговый регистр 17. В :завйсимости от BI О или Bj О в устройст ве управления определяется значение управляющего оператора , для второго шага. ро, j i, Ьо, гоНа втором шаге выполняется коррек ция множителя А в зависимости от зна чения 1 СО, 1 ., Из блока управления на вход 7 поступает сигнал запрета, устанавливающий сумматор-вычитатель 13 на вычитание а на входы 6 и 8 по тупает управляющий оператор Е, 1При О (В 0), элемент 21 И закрыт, множимое А на второй вход Ьумматора-вычитателя 13 не поступает й сдвиг оВыЙ регистр 16 продолжает сохранять нулевое состояние. При 1 (В 0), элемент 21 И открыт, множимое без сдвига поступает на вто ой вход сумматора-вычитателя 13 и ычитается из нуля, содержащегося до этого в сдвиговом регистреi16. Полученный дополнительный код множимого Адоп вновь поступает в сдвигойый регистр 16, определяя содержимое Ьдвигового регистра 16 после выполнения 2-го шага как О - g, 1 А E,Aдof,. Управляющее воздействие , подана ное на вход 6, выполняет соответствующую установку сумматора-вычитателя 20 сложение вычитание На вход 7 из блока памяти ,Т1Оступает число и на выходе 11 /cynMator Ьа-вычитателя 20 образуется число В2 BI -s gnBi-2, которое вновь поступает в сдвиговый регистр 17. Знак этого числа при появлении его на выходе 11 анализируется в блоке управления и определяет управляющий оператор кпя третьего шага. Начиная с третьего шага в коммутирующем блоке 12 происходят сдвиги мне-; жимого А вправо на каждом шаге на один разряд, в сдвиговом регистре 16 накапливается произведение, а на вход 7 из блока управления подается сигнал 1азрешения. В резуль1ате выполнения 3-го шага в сдвиговом регистре 17 имеет место сумма J Для определения управляющего воздействия следующего (четвертого) шага из блока памяти на вход 7 поступает число 2, на выходе сумматора-вычислителя 20 образуется число В Eg -singBa-a-, которое снова записывается в двйговнй регистр 17. После выполнения (п + 1) шагов, где п равно числу разрядов в сдвиговых регистрах арифметического устройства, в сдвиговом регистре 16 содержится произведение Z А-В при изменении сомножителей и результата в пределах , ,-4i В конце опёрац1 И результат Z может быть выведен по линии 11. Эффективность изобретения |заключ1ается в расширении функциональных возможностей арифметического устройства за счет вычисления произведения двух двоичных чисел за одну операцию, достигаемом за счет незначительного увеличения затрат оборудования.Формула изобретения Арифметическое устройство, содержащее три сдвиговых регистра, два коммутирующих блока, три сумматора-вычитателя и элемент И, причем разрядные вйходы первого и второго сдвиговых регистров соединены с соответствующими входами соответственно первого и второго коммутирующих блоков, упра ляющие входы которых подключены к пе вому управляющему входу устройства, вйхъды младших раврядов каждого из сдвиговых регистров п&дключены,к пер ВйЖ входам соответствующих сумматоров вычитателей, выходы которых являются выходами устройства, и подключены к. входам старших разрядов соответству ющих сдвиговых регистров и ко второму/ третьему и четвертому управляющим входам устройства, второй вход йё|Увого Ьумматора-вычйтателя соединен с выходом элемента И,-первый вхо «оторото подключен к выходу второго коммутирующего блока, а второй, вход к запрещающему входу устройства,vyn; равляющйе входы пёрйого и третьего сумматоров-вычитателей соединены с пятым управляющим входом устройства, второй вход третьего сумматора-вычитателя подключен к первому разрешающему входу устройства, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет вычисления произведений двух двоичных чисел за одну операцию, в него введены второй и третий (эпементы и, выхода которых соединены соответственно со вторым и управляющим входом второго сумматоравычитателя, а вторые входы - со вто рым и первым разрешающими входами устройства, первый вход второго ;3йе мента И соединен с выходом первого коммутирующего блока, первый вход третьего элемента И - с шестым управляющим входом устройства. ,- - -. Источники информации, принятые во внимание при экспертизе 1.Y.E.Voider The CORDIC trigonometric computing technique . IRE Transactions on Electronic Computers, VEC-8, 1959, №3. 2,Авторское свидетельство СССР 547765, кл. G Об F 7/38, 1977.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 2016 |

|

RU2625528C1 |

| Устройство для умножения на коэффициенты | 1988 |

|

SU1562904A1 |

| Устройство для умножения | 1976 |

|

SU651341A1 |

| Арифметическое устройство | 1975 |

|

SU547765A1 |

| Устройство для умножения чисел | 1990 |

|

SU1714595A1 |

| Устройство для преобразованияКООРдиНАТ | 1979 |

|

SU836636A1 |

| Арифметическое устройство | 1973 |

|

SU445042A1 |

| Устройство для умножения на коэффициенты | 1987 |

|

SU1458872A1 |

| Конвейерное вычислительное устройство | 1987 |

|

SU1432512A1 |

| Устройство для умножения | 1989 |

|

SU1667061A1 |

Авторы

Даты

1980-07-05—Публикация

1978-04-25—Подача