(54) ДАТЧИК ТАКТОВ

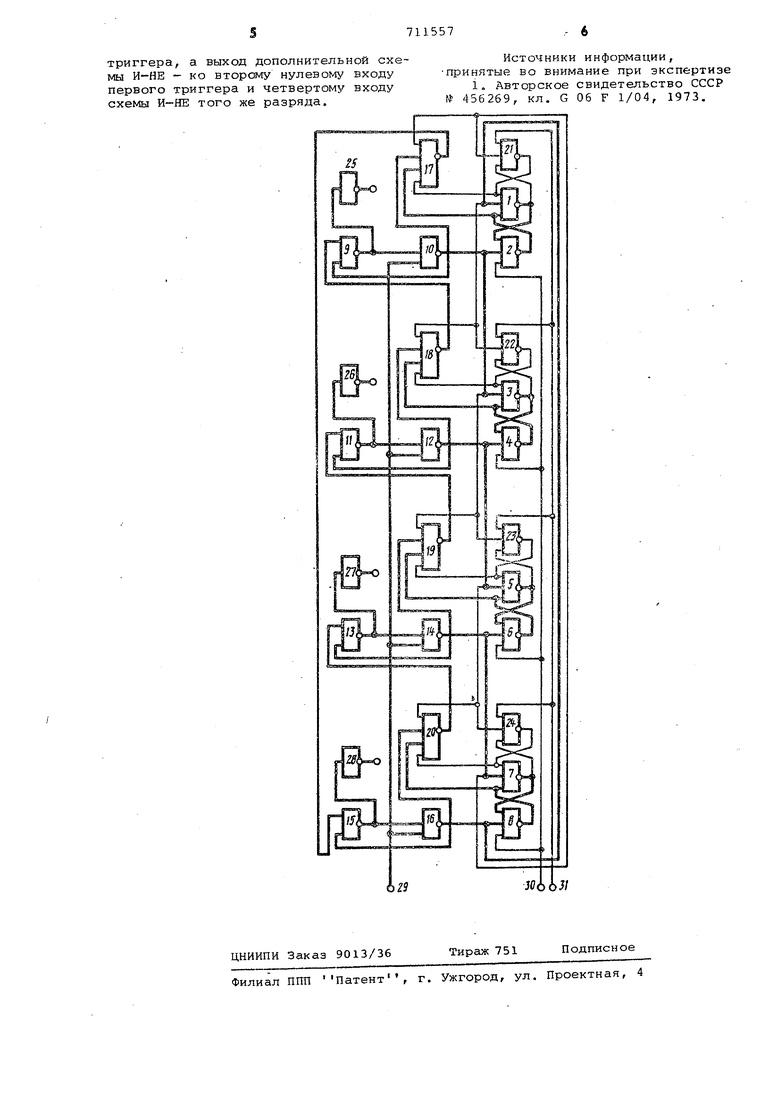

ры этих же разрядов, схемы И-ЯЕ 1720 являются основными, а 21-24 - дополнительными, схемы 25-28 служат для инвертирования выходных сигналов, 29 - шина тактирующего сигнала, 30 шина разрешения прямого распределения сигналов, а 31 - шина -разрешения обратного распределения сигналов.

Устройство работает следующим образом. В исходном состоянии первый триггер первого разряда устанавливается в единичное состояние, а остальные триггеры находятся в нулевом состоянии, тактирующий сигнал, подавае.мый на шину 29, отсутствует, равен логическому нулю. В режиме прямого распределения сигналов на шине 30 логическая единица, а на шине 31 логический нуль. В этом,случае на выходах схем 2, 4, б, 7, §, 11, 15, 20, 27 - логический нулк, на выходах: остальных схем - логическая единица. С приходсм тактирующего сигнала на выходе схемы 14 появляется сигнал, равный логическому нулю, который устанавливает первый триггер второго разряда в единичное состояние, а первый триггер первого разряда в нулевое состояние. Наличие связи с выхода схемы 14 на вход схемы 19 препятствует появлению на выходе И-НЕ 19 сигнала, равного логическому нулю, в момент действия тактирующего сигнала, равного логическому нулю, хотя первый триггер второго разряда изменил свое состояние.

Таким образом, на выходе схемы 14 возникает сигнал, длительность которого равна длительности входного сигнала, а на нулевом выходе первого триггера второго разряда появляется сигнал, длительность которого равна периоду следования :входных импульсов rto окончании действия входного сигнала на выходе схемы И-ЙЕ 19 появляется сигнал, равный логическому нулю, длительность которого равна длительности входного сигнала, а на выходе схемы 26 появляется сигнал, длительность которого равна периоду следования входных сигналов. С приходсм следующего входного сигналана выходе схемы Й-НЕ 12 появляется нуль, который устанавливает первый триггер третьего разряда в единичное состояние, а первый триггер второго разряда в нулевое состояние, при этом опять на выходе схемы И-НЕ 12 формируется сигнал, длительность которого равна длительности входного сигнала, а на выходе схемы И-НЕ 3 формируется сигнал, длительность которого равна периоду следования тактирующих импульсов. Наличие связей с выхода схемы И-НЕ 12 на входы схем 11 и 18 препятствует появлению на выходах этих схем логического нуля в момент действия данного входного сигнала. По

остальньлм ВЫХОДНЕЛМ каналам сигналы распределяются аналогичным образом.

В режиме обратного распределения сигналов на шине 30 - логический нуль, а на ишне 31 - логическая единица. В этом случае схемы И-НЕ 2, 4 , 6, 8 постоянно закрыты, а триггеры памяти образуются из схем 1 и 21-, 3 и 22, 5и23, 7и24. В силу симметричности устройства распределение сигналов в обратном направлении осуществляется точно так же, как и в прямом направлении.

Таким образом, предлагаемый датчик тактов позволяет организовать распределение сигналов, как в прямом, так и в обратном направлении, что ведет к расширению функциональньох возможностей устройства.

Применение предлагаемого изобретения в различных устройствах автоматики и вычислительной техники позволяет значительно сократить количество оборудования, поскольку отпадает необходимость в дополнительном датчике тактов, распределяющем сигналы в обратном направлении, исключить схему управления этими датчиками тактов, что дополнительно ведет к уменьшению габаритов веса, потребляемой мощности устройства, к повышению надежности его работы.

Кроме того, за счет того, что исключается дополнительный датчик тактов и схема управления упрощается изготовление регулировка и эксплуатация устройства.

Данные, подтверждающие достоверность достижения цели изобретения, и данные о технико-экономической эффективности, были получены при разработке, изготовлении и эксплуатации одного из проектируемых в части устройств.

Заявляемое изобретение готово для промьошленного использования.

Формула изобретения

Датчик тактов по авторскому свидетельству № 456269, о т л и ч а ющ и и с я тем, что, с целью расширения функциональных возможностей датчика тактов за счет обеспечения реверсивного режима распределения импульсов, он содержит две шины управления, а также дополнительную схему И-НЕ, в каждом разряде, причем первая шина управления подключена ко второму единичному входу первого триггера, а вторая шина управления - к первому входу дополнительной схемы И-НЕ каждого разряда, второй вход дополнительной схемы И-НЕ и третий, вход схемы И-НЕ i-ro разряда (1 1-т, где m - число разрядов) подключены к нулевому выходу второго триггера (.1 + 2)-го разряда, третий вход дополнительной схемы И-НЕ 5 подключен к нулевсму выходу первого

| название | год | авторы | номер документа |

|---|---|---|---|

| Датчик тактов | 1976 |

|

SU615470A2 |

| Делитель частоты на 3,5 | 1975 |

|

SU539382A1 |

| Делитель частоты на 2,5 | 1975 |

|

SU515288A1 |

| Многопрограмный делитель частоты | 1976 |

|

SU641658A1 |

| Делитель чатоты на 2,5 | 1976 |

|

SU570205A1 |

| Устройство для задержки импульсов | 1984 |

|

SU1280695A1 |

| Датчик тактов | 1973 |

|

SU456269A1 |

| Регистр сдвига | 1975 |

|

SU552638A1 |

| Делитель частоты на четыре, пять | 1976 |

|

SU744996A1 |

| Устройство для устранения влияния дребезга сигнала | 1989 |

|

SU1725371A1 |

Авторы

Даты

1980-01-25—Публикация

1977-09-19—Подача