(54) ДЕЛИТЕЛЬ ЧАСТОТЫ НА 2,5

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты на четыре, пять | 1976 |

|

SU744996A1 |

| Делитель на 7 | 1976 |

|

SU576662A1 |

| Многопрограмный делитель частоты | 1976 |

|

SU641658A1 |

| Делитель частоты на 4,5 | 1977 |

|

SU677106A1 |

| Делитель частоты на 1,5 | 1976 |

|

SU566359A1 |

| Делитель частоты на двенадцать | 1977 |

|

SU698131A1 |

| Делитель частоты следования импульсов на 5,5 | 1978 |

|

SU746945A1 |

| Делитель частоты на шесть | 1976 |

|

SU617846A1 |

| Делитель частоты на девять | 1977 |

|

SU687603A1 |

| Делитель частоты на 5,5 | 1978 |

|

SU771880A1 |

1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах, где необходимо деление последооательности импульсов на 2.5.

Известны делители частоты, каждый . разряд которых содержит триггеры памяти, комкгутационные триггеры и элементы И-НЕ tl,2.

Первое из известных устройств содержи большое количество оборудования и обладает невысокой надежностью.

Второе устройство является более совершенным н содержит три разряда, каждый из которых состоит из триггера памяти и элемента И-НЕ, я двух коммутационных триггеров и дополнительного элемента И-НЕ, npv этом к входной шине подключены единичный вход первого коммутационного триггера, нулевой вход второго коммутационного триггера и входы элементов И-НЕ второго и третьего разрядов. Единичный выход первого коммутационного триггера соединен с нулевым входом триггера памяти первого разряда и с нулевым входом второго коммутационного триггера, нулевой выход которого соединен с единичным входом триггера памяти первого разряда и со входом элемента И-НЕ второго разряда. Единичньй выход триггера Памяти первого разряда подклЮ чен к единичному входу второго коммутационного триггера р ко входу элемента И-НЕ второго разряда, выход которого соединен с единичными входами триггеров памяти первого и второго разрядов и со входом элемента И-НЕ третьего раз яда. Нулевой выход триггера памяти второго разряда подключен к нулевым входам триггера памяти первого разряда и второго коммутационного триггера, единичный выход триггера памяти второго разряда соеди йен со входом элемента И-НЕ третьего разряда, выхс i которого подключен к единичным входам триггеров памяти второго и третьего разрядов. Нулевой выход триг гера памяти третьего разряда соединен с нулевым входом триггера памяти второго разряда.

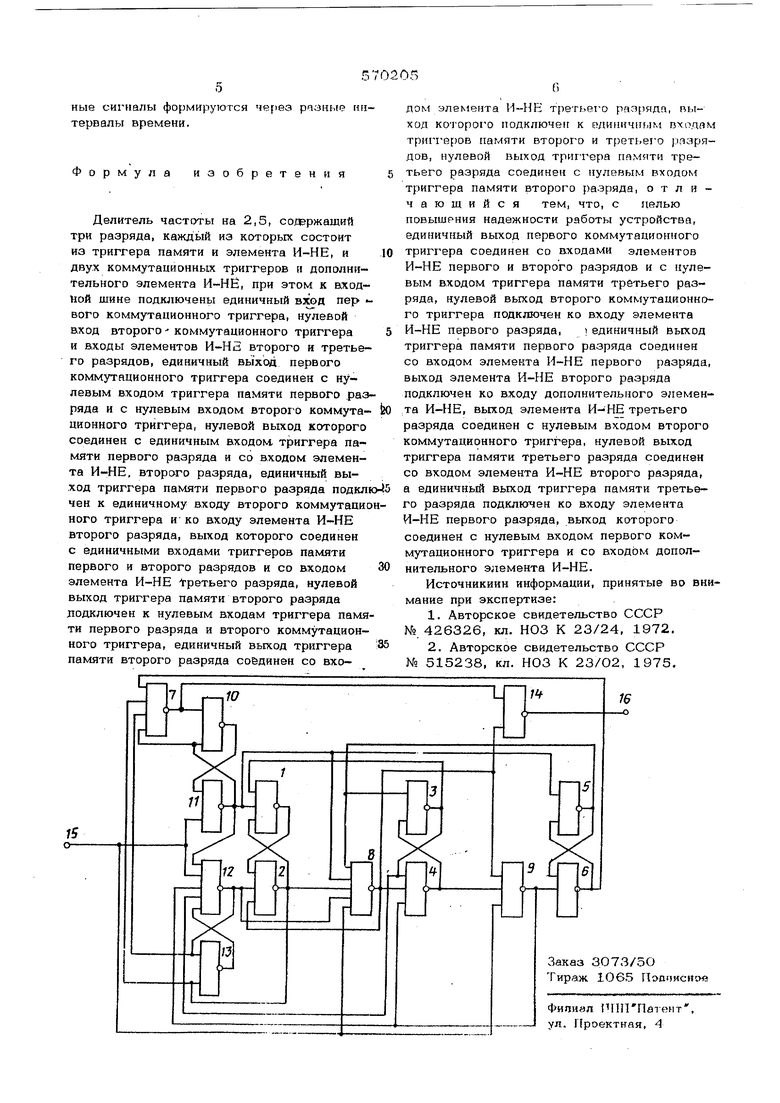

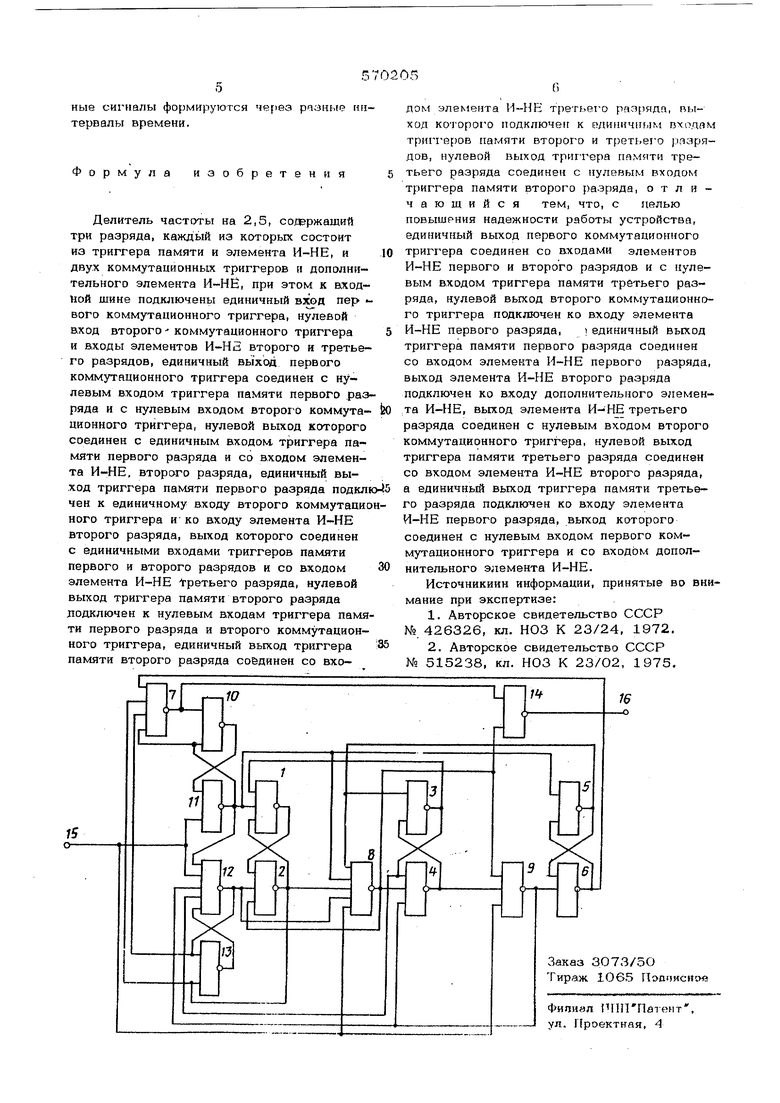

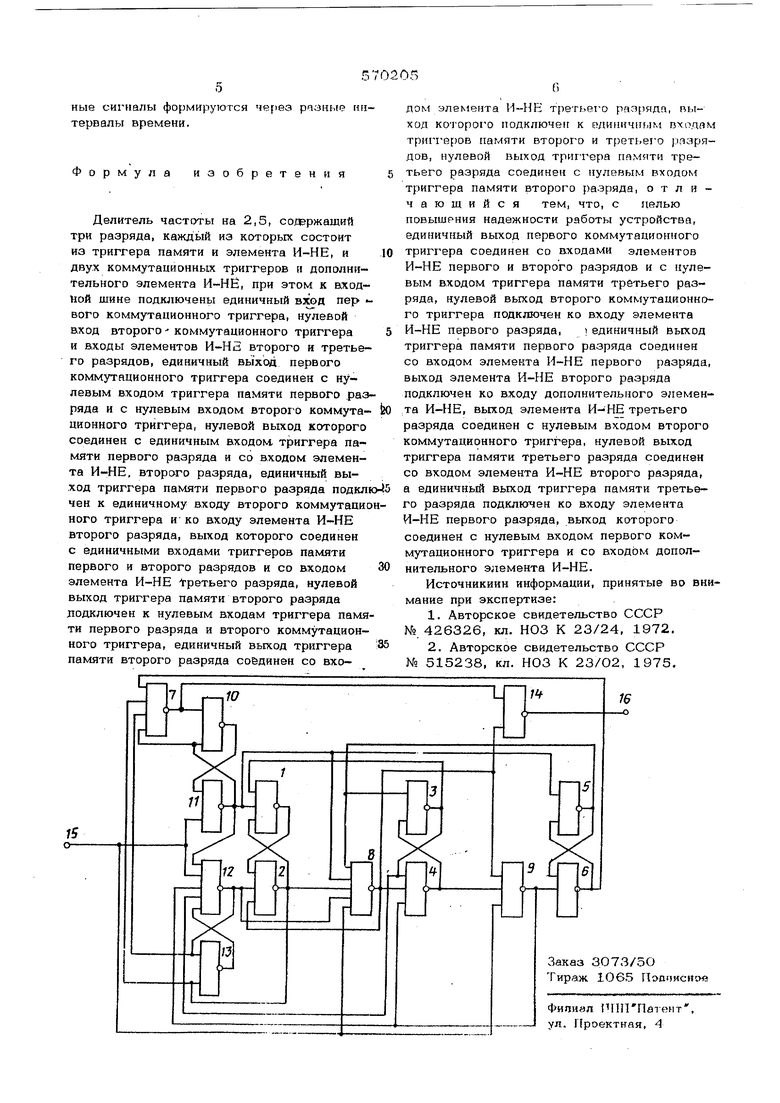

Однако известное устройство вьшопнено на большом ктичестве элементов И-НЕ и, следо1затвл1 но, обладает невысокой иодеж их:тью. Цель изобретения - повышение надежнос ти работы устройства. Для этого в делителе частоты па 2,5,содержанюм три разряда, каждый из которы состоят из триггера памяти и элемента Hи двух коммутационных триггеров и дополнитйльного элемента , единичный выход первого коммутационного триггера соединен со входом элементов И-НЕ первого и второго разрядов и с нулевым входом триггера памяти третьего разряда, нулевой выход второго коммутадионЕшго триггера подключен ко входу элемента И-НЕ первого разряда, единичный выход триггера памяти первого разряда соединен со входом элемента И-НЕ первого разряда, выход элемента второго разряда подключен ко входу дополнительного элемента И-НЕ, выход эле: 1ента И-НЕ третьего разряда соединен с нулевым входом второго комму тационного триггера, нулевой выход триггера памяти третьего разряда соединен со «.ходом элемента И-НЕ второго разряда, а единичный выход триггера памяти третьего разряда подключен ко входу элемента И-НЕ первого разряда, вьгсод которого сое динен с нулевым входом первого коммутационного триггера и со аходом дополнительного элемента И-НЕ, На чертеже представлена структурная электрическая схема делителя частоты на 2,5. Устройство содержит элементы 1-6 И-НЕ, попарно образующие триггеры памя ти первого, второго и третьего разрядов, .элементы 7-9 И-НЕ этих разрядов, элементы Ю-13 И-НЕ, попарно образующие первый и второй коммутационные триггеры элемент 14 И-НН дополнительный, входную шину 15, выходную шину 16. Устройство работает следующим образо В исходном состоянии триггеры памяти всех разрядов нахрдятся в нулевом состоя нии, а тактирующий сигнал, Люступаю.щий на входную шину 1Й, отсутствует (равеЕ логическому нулю). В этом случае на выходах элементов 7,11,12,13,1,8,3,9,5 бу дет сигнал, равный логической единице, на выходах остальных элементов будет сигнал равный логическому нулю. С при:ходом пер вого тактирующего импульса открывается -jvMeMRUT 12 и на его выходе появляется сигнял, равный логическому нулю, который устан.чвли. триггер первого разряда п едииич. о .-остояипе. Наличие связи с RbtxuAii Гло.мента 12 на нходы элементов .1.3 и 8 1}р иятстяует появлению на кыко;i:i. . .ЧЯО.МРНТОР сигнала, равного лиги ческому нулю, гз момент действия тактирую.шег.о сигнала, Послеокончания действия тактирую.шего импульса на выходе элемента 13 появляется сигнал, равный логическому нулю, поэтому с приходом второго тактирующего импульса логический нуль появляется на выходе элемента 8, который устанавливает триггер второго разряда в единичное состояние и через дополнительный элемент 14 поступает на выходную шину 16. Сигнал, равный логическому iнулю, с нулевого выхода триггера второго разряда (элемент 3) устанавливает в нулевое состояние триггер второго разряда. Наличие связей и с вьгхода элемента 8 на в.ходы элементов 2 и 9 препятствует появлению на вьрсодах этах элементов сигнала, равного логическому нулю, в момент действия так- ирующего сигнала. Аналогичным образом с приходом третьего тактирующего импульса логический нуль появляется на выходе элемента 9, устанавливая триггер третьего разряда в единичное состояние, при этом сигналом с вы.хода элемента 5 триггер второго разряда устанавливается в нулевое состояние. Наличие связи с выхода элемента 9 на вход элемента 12 препятствует открыванию элемента 12 в момент действия третьего тактирующего импульса. С приходом четвертого тактирующего импульса открывается элемент 12. Появившийся на его выходе сигнал, равный логическому нулю, устанавливает триггер первого разряда в единичное состояние, наличие связи с выхода элемента 3 2 на вход элемента 7 Препятствует появлению на выходе элемента 7 сигнала, равного слогическому нулю, в момент действия тактирующё го импульса. По окончании действия тактирующего импульса на выходе элемента 7 появляется сигнал, равный логическому нулю, который через элемент 14 поступает на выходную шину 16, а на выходе элемента 10 появляется сигнал, . равный логической единице. С приходом пятого тактирующего импульса открывается элемент 11, поя вившийся на его выходе сигнал, равный логическому нулю, устанавливает триггеры первого и третьего разрядов в нулевое состг. тояние и закрывает элемент 7. Наличие связей Свьгхода элемента 11 на входы элементов 10, 12, 8 препятствует появлению опасных состязаний в схеме устройства. По окончании действия пятого тактирующего импульса схема возвращается в исходное состояние. Таким образг.-м, на 5 входных импульсов схема выдает два выходных, т.е. происходит деление частоты на 2,5, приче.ч выход

Авторы

Даты

1977-08-25—Публикация

1976-04-16—Подача