(54) ДЕЛИТЕЛЬ ЧАСТОТЫ НА НЕТЫРЕ, Изобретение относится к автоматике и вычислительной технике и может быть иопользовано в устройствах, где необходимо деление последовательности импульсов на .четыре, пять. Известны делители частоты, выполненные на логических элементах, которые д&лят последовательность импульсов на четыре, пять Ш, И. Первое из известных устройств содержит разряды, каждый из которых выполнен на триггере памяаги, коммутационном триггере и элементе СЦ Однако оно имеет большое количество оборудования и обладает низкой надежностью. Второе из известных устройств выбирается в качестве прототипа. Оно содержи четыре разряда, каждый из которых состо ит из триггера памяти, коммутационного триггера и схемы И-НЕ, причем в каждом из первых трех разрядов единичный выход триггера памяти соединен с единичным ncoflOM коммутационного триггера, нулеПЯТЬвой выход которого связан с единичным входом триггера памяти данного разряда, с нулевыми входами триггеров памяти и коммутационных триггеров всех предыду щих разрядов и со входом схемы И-НЕ предыдущего разряда, единичный выход коммутационного триггера первого разряда соединен со входом схемы И-НЕ этого разряда, выход которой соединен с обоими входами коммутационного второго разряда, а единичный выход коммутационного триггера второго разряда - со входом схемы И-НЕ этого разряда, вьтход которой подключен к обоим входам коммутационного Tpinrepa третьего разряда и - вход схемы И-НЕ четвертого разряда, выход схемы И-НЕ четвертого разряда соединен с единичным входом триггера памяти этого разряда, нулевой вход которого связан с единичным выходом коммутационного триггера четвертого разряда, а шина тактирующего сигнала - с нулевыми входами коммутационных триггеров первых трех разрядов, со входом схемы И-НЕ и с ед нйчным входом коммутационного триггера четвертого разряда.

Однако известное устройство вьшо,тнено на большом количестве оборудования, поскольку в четвертом разряде содерлшт дополнительный элемент И-НЕ, кроме , для организации деления частоты на 4, 5 требуется еще минимум четыре элемента И-НЕ с большим числом межрззрялных связей. Это существенно снижает общутю надежность устройства.

Целью изобретения является повыиюние йадежности работы устройства.

Это достигается тем, что в делителе частоты на четыре, нять, содержащем выходвой. элемент И-НЕ и четыре разряда, каждый из которых состоит из коммутационного триггера, триггера памяти, :вы полненных на нерекрестно соединенных эломентах 14-НЕ, и элемент И-НЕ, причем в каждом из первых трех разрядов единичный выход триггера памяти соединен с еди нячным входом коммутационного триггера, нулевой выход которого связан с единичным входом триггера памяти данного раз- ряда, с нулевьм входом .триггера памяти и с нулевым вкодсм коммутацио1шого гриГ герз предыдущего разряса, единичный выход коммутационного триггера первого раз ряда соединен со входом элемента этого разряда, выход которого подключен к нулевому и еданичному нходам коммутационного триггера второго разрйда, единичный выход коммутацион юго триггера второго разряда - со входом элемента

этого разряда, выход которого подключен к нулевому и единичному входам € ммутационного триггера третьего разряда и ко входу элемента И-НЕ четв vpioго разряда, которого соеданен с

единичным входом триггера памяти этого разряда, нулевой нход которого связен с единичным выходом коммутационного четвертого разряда, а шина тактир5ао щего сигнала соединена с нулевыми вхо дами коммутационных триггеров первых трех разрядов, со жодом элемента И.НЕ и с единичным входом коммутациоТлНого триггера четвертого разряда, входы элемента И-НЕ третьего разряда соединены с выходами элемента И-НЕ и единичным выходом триггера памяти четвертого разряде, а выход - со входом выходного элемента И-НЕ, с нулевыми входами триггеров памяти трех первых разрядов и с ну- левым входом комм утациошюго триггера четвертого разряда, единичный выход ко подключен к нулевому шсоду коммутационного триггера яерво1Х) разряда, нулевой выход коммутационного триггера третьего разряда соединен со входом элемента И-HFZ четвертого разряда, со входом выходного элемента И-НЕ и с нулевыми ачодами триггера памяти и коммутационного триггера первого разряда, а единичный выход триггера памяти третье-го разряда подалючен ко входу элемента И-НЕ четвертого разряда.

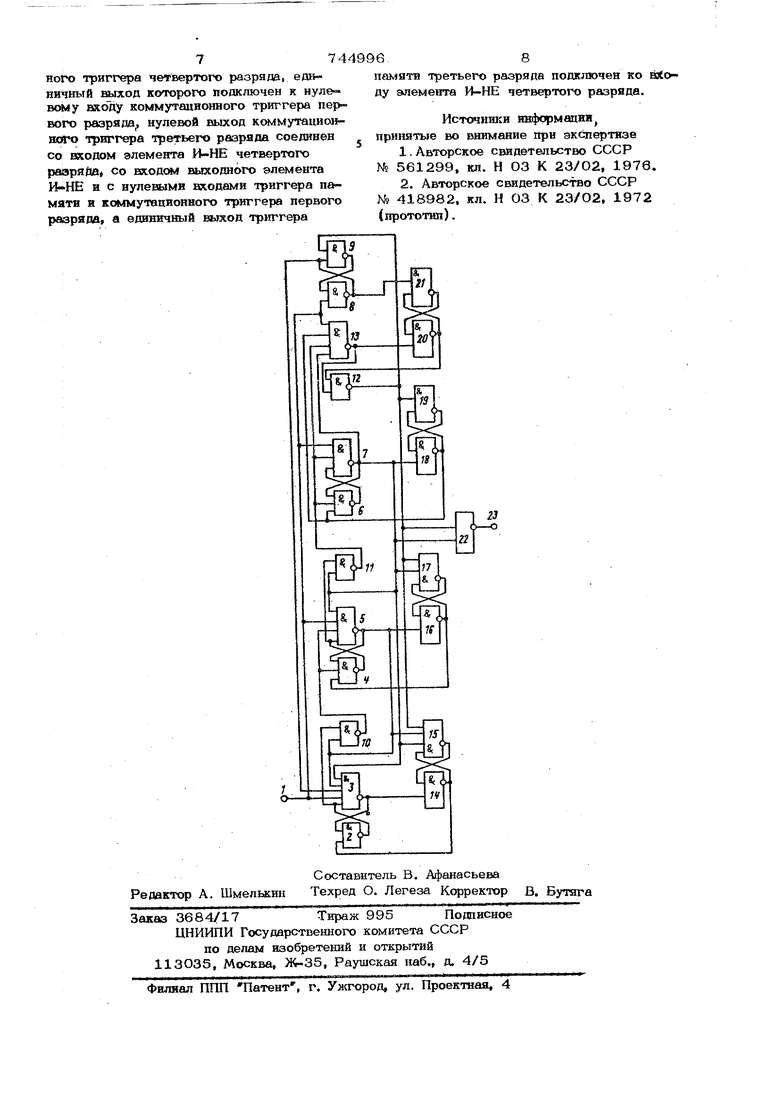

На чертеже представлена структурная электрическая схема делителя частоты на Четыре, пять.

Устройство содержит шину 1 тактовых .импульсов, элементы И-НЕ 2 и 3, 4 и 5, 6 и 7, 8 и 9, образующие, коммутационные триггеры первого-четвертого разрядов элементы И-НЕ, 10, 11, 12, 13 этих раз рядов, элементы И-НЕ 14 и 15, 16 и 17 18 и 19, 2О и 21, образующие триггеры памяти этих разрядов, выходной элемент 22, выходную шину 23.

Устройство работает следующим образом.

В исходном положении триггеры памяти всех разрядов находятся в нулевом состоянии, а тактирующий сигнал, прст тхающий по штге 1, отсутствует (равен логическо-му нулю), в этом случае на ныходах элементов И™НЕ 9, 11, Ю, 20, 18. 16, , 14 и на шине 23 - логический нуль, на выходах остальных элементов И-НЕ логическая единица. С приходом -первого так- тирующего импульса открывается элемент И- liE 3s на его выходе появ/ьчется сигнал, равный логическому нулю,, который устанавливает риггер памяти разряда в единичное состояние. После окончания действия тактирующего импульса не выходе элемента И-НЕ 12 появляется сигнал, равга тй логическому нулю, а на выходе элемента 10 - сигнал, равный логической еди нице. Поэтому с приходом второго тшстирующего импульса откры.вается элемент И-НЕ 5, Сигнал, равшлй логическому ну лю, с выхода этого элемента устанавливает триггер памяти второго разряда в единичное сосч-ояние, а триггер памяти первого разряда - в нулевое. Наличие связей с выхода элемента И-НЕ S на входы эле- i-лентов И-НЕ 4, 10, 3 препятствует по явлению на выходах этих элементов ло гического нуля в мсяиепт действг-ш тестирующего сигнала, когда триггеры памяти изменяют свое состояние,

С приходом третьего тшстирующего импульса логический нуль снова появляется на выходе элемента 3, устанавливая

триггер памяти пер.вого разряда в единичное состо5щие. После окончания действия тактирующего импульса на выходе элемента И-НЕ появляется сигнал, равный лоп ческой единице, следовательно, на выходе элемента И-НЕ 4 будет сигнал, равный логическому нулю, а на выходе элемента I4-HE 4 - сигнал, равный логической единице. Поэтому с приходом четвертого так- .тирующего импульса сигнал, раышгй логическому нулю, появляется на выходе элемента И-НЕ 7, который устанавливают триггеры памяти первого и второго разрядов в нулевое состояние и который через выходной элемент И-НЕ 22 поступает в вьрсодную шину 23.. Наличие связей с выхода элемента И-НЕ 7 на входы элементов И-НЕ 13, 16, 11, 5,3 опять препятствует неправильной работе устройства С приходом пятого тактирующего импульгса снова открывается только элемент И-НЕ 13, устанавливается триггер памяти первого разряда в единичное состояние.

Элементы И-НЕ 8, 13, 7, 5 не открь ваются, поскольку на выходах элементов И-НЕ 9, 11, 10 - логический нуль. Аналогично с приходом шестого тактир}тощего импульса логический нуль появляется на выходе элемента И-НЕ 5, устанавливая триггер памяти второго разряда в единичное Состояние, а триггер памяти первого разряда - в нулевое. С приходом седьмого тактирующего импульса триггер памяти первого разряда снова переводится в единичное состояние. После окончания дейс-рВИЯ седьмого тактирующего импульса н выходе элемента И-НЕ 11 появляется сигнал, равный логической единице, а на выходе элемента И-НЕ 6 - сигнал, равный логическому нулю. Поэтому с приходом восьмого тактирующего импульса логический нуль появляется на выходе элемента И-НЕ 13, устанавливая триггер памяти четвертого разряда в единичное состояние.

После окончания действия тактирующёго импульса на выходе элемента И-НЕ 12 появляется сигншГ, равный логическому нулю,. который устанавливает триггеры памяти первых трех разрядов в нулевое состояние и который через выходной элемент И-НЕ 22 поступает в выходную шину 23. С приходом девятого тактирующего импульса логический нуль образуется на выходе элемента И-НЕ 8, переводя триггер памяти четвертого разряда в нулевое состо ние, при этом на выходе элемента И-НЕ 12 снова появляется сигнал, равный логической единице, и устройство возвращается в исходное положение. Надшчие связи с выхода элемента И-НЕ 8 на нход элемента И-НЕ 3 препятствует открыванию этого

элемента в момент действия девятого тактирующего импульса.

Таким образом, на 9 входных импульгсов устройство вьгдает два выходных, т.е. происходит деление частоты на 4, 5, причем Ш)Гходные сигналы формируются через равные интервалы времени.

Формула изобретения

Делитель частоты на четыре, пять, содержащий выходной элемент И-НЕ и четыре разряда, каждый из которых .состоит из коммутадиогшого триггера, триггера памяти, выполненных на перекрестно соеди, ненных элементах И-НЕ, и элемент И-НЕ, причем в каждом из первых трех разрядов единичный выход триггера памяти соединен с единичным входом коммутационного триггера, нулевой выход которого соединен с единичным входом триггера памяти данного разряда, с нулевым входом триггера памяти и с нулевым входом коммутационного триггера предыдущего разряда, еш ничный выход коммутационного триггера первого разряда соединен со входом элемента И-НЕ этого разряда, выход которого подключен к нулевому и единичному входам коммутационного триггера второго разряда, единичнь1Й выход коммутационного триггера второго разряда соединен со входом элемента И-НЕ этого разряда, выход которого подключен к нулевому и единичному входам коммутационного триггера третьего разряда и ко входу элемента И-НЕ че-пвертого разряда, выход которого соединей с единичным входом триггера памяти этого разряда, нулевой вход которого соединен с единичным выходом коммутационного триггера четвертого разряда, а щина так- Т1фующего сигнала соединена с нулевыми входами коммутационных триггеров первых трех , со входом элемента И-НЕ и с единичным входом коммутационного триггера четвертого разряда, отличающийся тем, что, с целью повышэния надеишости работы устройства, входы элемента И-НЕ третьего разряда соединены с выходами элемента И-НЕ и единичным выходом триггера памяти четвертого разряда, а выход - со axojaoM выходного элемента И-НЕ, с нулевыми входами триггеров памяти трех первых разрядов и с нулевым входом кс лмутацио№

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоичный счетчик | 1976 |

|

SU653747A2 |

| Делитель чатоты на 2,5 | 1976 |

|

SU570205A1 |

| Делитель частоты на шесть | 1976 |

|

SU617846A1 |

| Делитель частоты следования импуль-COB HA 15 | 1979 |

|

SU818022A1 |

| Делитель частоты следования импульсов на 5,5 | 1978 |

|

SU746945A1 |

| Делитель частоты на двенадцать | 1977 |

|

SU698131A1 |

| Делитель на 7 | 1976 |

|

SU576662A1 |

| Делитель на 5 | 1976 |

|

SU558405A1 |

| Делитель частоты на 3,5 | 1975 |

|

SU539382A1 |

| Делитель частоты на 5,5 | 1978 |

|

SU771880A1 |

Авторы

Даты

1980-06-30—Публикация

1976-11-22—Подача