1

Изобретение относится к вычислитель ной технике и может быть использовано для построения различных устройств вычислительной техники, для которых требуется, чтобы перерывы питания не приводили к потере информации.

Известно запоминающее устройство, сохраняющее информацию при перерывах питания, у которого в качестве запоминающего элемента служит сердечник с прямоугольной петлей гистерезиса (ППГ) 1. .

Основным недостатком такого устройства является большое потребление мощности. Это вызвано тем, что ток, необходимый для перемагничивания сердечника, протекает на протяжении всего времени подачи питания на триггер. Кроме того, данное устройство не позволяет использовать статические триггеры в интегральном исполнении.

Из указанных устройств наиболее близким по технической сущности является запоминающее устройство, сохраняю-

щее состояние при перерывах питания. Оно содержит статический триггер, запоминающийсердечник с ППГ и одностабильный пороговый элемент, причем начало первой обмотки записи, конец которой подключен к катоду диода, при ;оединенного анодом к коллектору второго транзистора статического триггера, соединено с концом второй обмотки записи, начало которой подключено к катоду диода, присоединенного анодом к средней точке делителя, состоящего из резистора, подключенного к клемме коллекторного питания и диода, анод которого подключен к нулевой клемме, а к точке соединения обмоток записи подключены резистор, соединенный другим концом с клеммой коллекторного питания, и катод диода, соединенного анодом с выходом порогового устройства, к которому подключены аноды диода, соединенного катодом с коллектором первого транзистора статического триггера, И диода, соединенного катодом со средней точкой

делителя, у которого одни резистор подключен к шине коллекторного питания, а второй резистор, шунтированный конденсатором, подключен к шине нулевого потенциала, причем к средней точке этого делителя присоединен конец обмотки считывания сердечника с ППГ, начало которой соединено с анодом диода, катод которого соединен с базой первого триода статического триггера 2.

Недостатками этого устройства являются большое потребление мощности, низкая помехоустойчивость, отсутствие возможности записи в запоминающее устройство и восстановление на статическом триггере информации в заданный момент времени.

Целью предлагаемого изобретения является повышение помехоустойчивости и уменьшение потребляемой мощности устройства.

Уменьшение мощности, потребляемой запоминающим устройством, достигается благодаря использованию импульсного способа записи и считывания, а также записью и считыванием только в момент выключения и включения питания соответственно или в заданный момент времени. Повышение помехоустойчивости достигается благодаря тому, что питание триггера производится от накапливающего конденсатора, причем считывание производится только в тот момент, когда энер гии, запасенной в конденсаторе, будет достаточно для выполнения операции считывания и записи.

Поставленная цель достигается тем, что в устройство, содержащее накопитель триггер, первый пороговый элемент, соединенный с первой шиной питания, вторую шину питания и шину управления, введены второй пороговый элемент, элементы И, элемент ИЛИ, элемент запрета и формирователи импульсов, причем первый пороговый элемент, первый элемент И, . первый и второй формирователи импульсов соединены последовательно, выход второго формирователя импульсов подключен к одному из входов элемента ИЛИ и к одному из входов второго элемента И, другой вход которого соединен с выходом накопителя, входы накопителя соединены с выходами третьего элемента И и элемента ИЛИ соответственно, другой вход элемента ИЛИ подключен к выходу четвертого элемента И, одни из входов третьего и четвертого элементов И соединены с выходами триггера, а другие Bxoaiii - с выходом третьего формирователя импульсов, ВХ0ДЫ триггера соединены с выходом второго элемента И и выходом первого формирователя импульсов соответственно, выход второго порогового элемента соединен с первым входом пятого элемента И, выход которого подключен к одному из входов элемента запрета, другой вход элемента запрета через четвертый формирователь импульсов соединен с первого элемента И, входы которого подключены ко вторым входам пятого элемента И и шине управления, выход элемента запрета соединен со входом третьего формирователя импульсов, вход второго порогового элемента соединен со второй шиной питания.

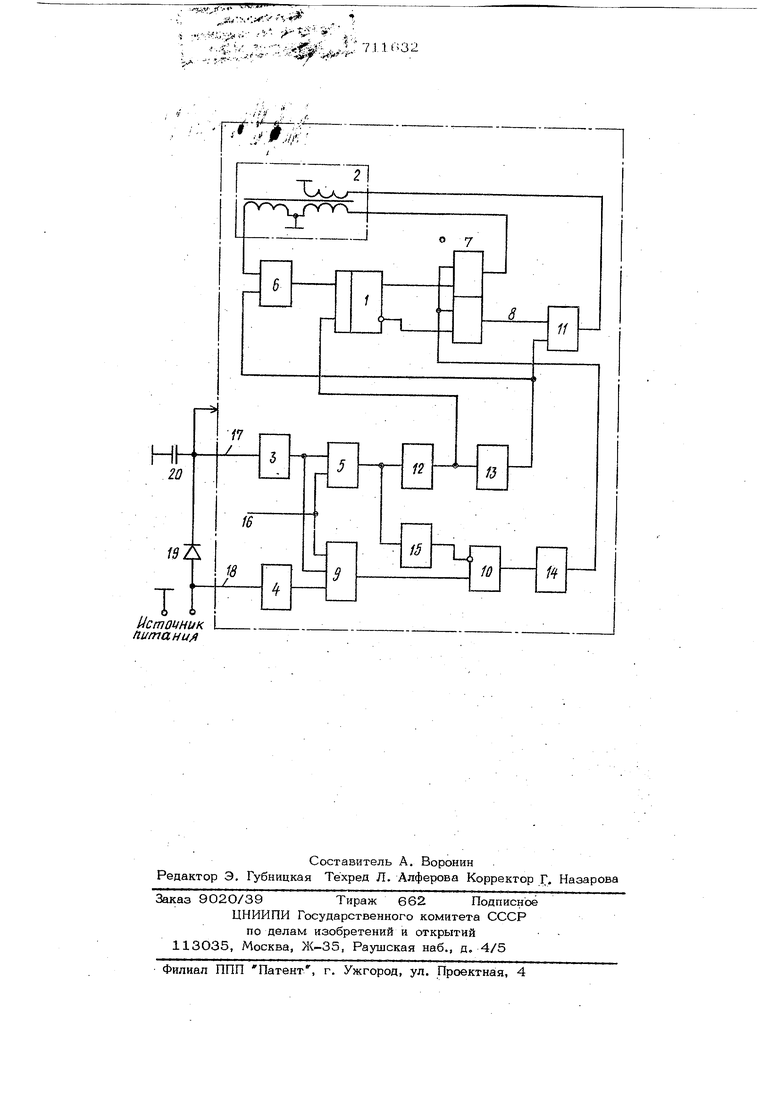

На чертеже представлена функциональная схема устройства.

Оно содержит триггер 1, накопитель 2, пороговые элементы 3, 4, элементы И 5-9, элемент запрета 10, элемент ИЛИ 11, формирователи импульсов 1215, шину управления 16, шины питания 17 и 18, диод источника питания 19 и конденсатор 20.

Устройство работает следующим образом. После того как включится питание, срабатывает пороговый элемент 3 и положительный фронт выходного сигнала порогового элемента 3 через элемент И 5 запускает формирователи импульсов 12, 15. Выходной сигнал формирователя 12 устанавливает триггер 1 в нулевое состояние и задним фронтом запускает фор- мирователь импульса 13.- Считывающий .импульс через элемент ИЛИ 11поступае на накопитель 2 и производит считывание. Если сердечник накопителя 2 был в единичном состоянии, то сигнал с выходной обмотки через элемент И 5 установит триггер 1 в единичное состояние.. В противном случае триггер 1 так и останется в нулевом состоянии.

При выключении питания срабатывает пороговый элемент 4 и через элемент И 9 и элемент запрета 10 отрицательным перепадом выходного сигнала порогового элемента 4 запускает формирователь импульса 14. Записывающий импуль через элемент И 6 или 8 (в зависимости от состояния триггера) поступает на накопитель 2.

Длительность сигнала на выходе формирователя импульса 15 выбрана больше чем суммарная длительность сигналов формирователей импульсов 12 и 13. Это выполнено с целью исключить возможность неправильной работы триггера в случае появления питания на время мень шее, чем суммарное время, необходимое для. формирования импульсов формирователями 12 и 13. (Элемент запрета 10 будет закрыт на время, необходимое для формирования указанных импульсов). Записывающий -импульс не будет выработан также в том случае, если питание Ёключится на время, не достаточное для заряда конденсатора 20, так как пороговой элемент 3 будет закрывать элемент И 9. При подаче нуля на шину управления 16 закрываются элементы И 5, 9 и фор мируется импульс записи. С этого момен та информации о промежуточном состоянии триггера 1 будут храниться в накопи теле 2, а триггер 1 может выполнять дальнейшие операции. Если необходимо восстановить на триггере 1 информацию, записанную в накопителе 2, то на шину управления 16 подается единичный потенциал, который вызывает появление сигналов на формирователях 12 и 13, что при водит к восстановлению промежуточного состояния триггера 1. Для построения устройств, содержащих несколько триггеров, достаточно к каждому статическому триггеру добавить по одному накопителю 2, элементы И 6, 8, 7 и элемент ИЛИ 11, а остальная часть устройства может быть общей для всех триггеров. На базе триггера с запоминанием информации при перерывах питания могут быть построены счетчики, которые могут заменить механические и электромеханические счетчики, имеющие большие габариты, малое быстродействие, большую трудоемкость в изготовлении. Изготовлен макетный образец запоминающего устройства и проведены климатические испытания, которые показали, что устройство работоспособно в диапазоне температур от - 5О до + 70 С. ФОрмула изобретения Запоминающее устройство, содержащее накопитель, триггер, первый пороговый элемент, соединенный первой с шиной питания, вторую шину питания и шину управления, отличающееся тем, что, с целью повышения помехоустойчивости и уменьшения потребляемой мощности устройства, в него введены второй пороговый элемент, элементы И, элемент ИЛИ, элемент запрета и-формирователи импульсов, причем первый пороговьтй элемент, первый ачемент И, первый и второй формирователи импульсов соединены последовательно, выход второго формирователя импульсов подключен к одному из входов элемента ИЛИ и к одному из входов второго элемента И, другой вход которого соединен с выходом накопителя, входы накопителя соединены с выходами третьего элемента И и; элемента ИЛИ соответственно, другой вход элемента ИЛИ подключен к выходу четвертого элемента И, одни из входов третьего и четвертого элег/.энтов И соединены с выходами триггера, а другие входы - с выходом третьего формирователя импульсов, входы триггера соединены с выходом второго элемента И и выходом первого формирователя импульсов соответственно, выход второго порогового еттемента соединен с первым входом пятого элемента И, выход которого подключен к одному из входов элемента запрета, другой вход элемента запрета через четвертый формирователь импульсов сое- динен с выходом первого элемента И, входы которого подключены ко вторым ходам пятого элемента И и шине управения, выход элемента запрета соединен о входом третьего формирователя импульов, вход второго порогового элемента оединен со второй шиной питания. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 25О998, кл. G 11 С 11/06 05.О8.68. 2. Авторское свидетельство СССР № 239384, кл. G 11 С 11/00, О9.08.67 (прототип).

г ::;:. ..

, .., - ,;,

..€v ---..: 711032 } ....:,.:-:-5-

| название | год | авторы | номер документа |

|---|---|---|---|

| СОХРАНЯЮЩИЙ СОСТОЯНИЕ ПРИ ПЕРЕРЫВАХПИТАНИЯ | 1969 |

|

SU239384A1 |

| Регистр сдвига | 1982 |

|

SU1111207A1 |

| Накопитель для запоминающего устройства | 1983 |

|

SU1137537A1 |

| Реверсивный дешифратор | 1976 |

|

SU604151A1 |

| Триггерное устройство | 1979 |

|

SU813709A1 |

| Запоминающее устройство | 1988 |

|

SU1547032A1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1990 |

|

RU2037872C1 |

| ПИКОВЫЙ ДЕТЕКТОР | 2012 |

|

RU2506598C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2002 |

|

RU2248662C2 |

| Элемент памяти | 1989 |

|

SU1642521A2 |

;у у

F.AV

Тхх-/

I

Авторы

Даты

1980-01-25—Публикация

1977-09-30—Подача