1

Изобретение относится к области вычислительной техники и цифровых измерительных приборов и может быть использовано для преобразования мгновенного значения переменного напряжения в цифровой код.

Известны аналого-цифровые преобразователи параллельно-последовательного типа для преобразования мгновенного значения переменного напряжения в цифровой код, построенные по известной кJтaccичecкoй схеме, в которой уровень сигнала- для последующего набора компараторов образуется вычитанием в сумматоре уровней входного сигнала и сигнала, полученного на предьщущем такте 1 .

Такие аналого-цифровые преобразователи имеют недостаточно высокое быстродействие.

Наиболее близким по технической сущности к предложенному является аналого-цифровой преобразователь параллельно-последовательного типа, содержаидий два набора компараторов, шифраторы, регистры,цифроаналоговый преобразователь, сумматор и резисторные делители эталонного напряжения, на первом такте работы которого определяются старшие, а на вто|зОм младшие разряды выходного двоичного кода 2.

К недостаткам этого преобразователя следует отнести низкое быстродействие по сравнению с аналого-цифровым преобразователем непосредственного считывания, содержащим один набор компараторов по числу уровней квантования входной величины.

Целью изобретения является повышение быстродействия.

Доставленная цель достигается тем, что в аналого-цифровой преобразователь параллельнопоследовательного типа, содержащий два резисторных делителя эталонных напряжений, два набора компараторов, выходы которых через соответствующие шифраторы соединены с первыми входами соответствуюи)их регистров, управляющие входы которых и управляющий вход второго шифратора соединены с соответствующими шинами тактовых импульсов, дополнительно введены два дифференщ1альных усилителя, логический блок управления и блок выборки и хранения, первый и второй входы которого соединены соответственно с шиной

входного сигнала и шиной тактовых импульсов, первый выход блока выборки и хранения соединен с первым входом компараторов первого набора, второй выход блока выборки и хранения соединен с первыми входами первого и второго дифференциальных усилителей, вторые входы которых соединены соответственно с первым источником эталонного напряжения и шиной земля, а выходы первого и второго дифференциальных усилителей соединены с входами первого резисторного делителя эталонного напряжения, выход которого соединен с вторым входом компараторов первого набора, а выход второго дифференциального усилителя соединен также с первым входом компараторов второго набора второй вход которого соединен с выходом второго резисторного делителя эталонного напряжения, входы которого соединены соответственно с вторым источником эталонного напряжения и шиной земля, причем выход компараторов второго набора через логический блок управления соединен с вторым входом . первого регистра.

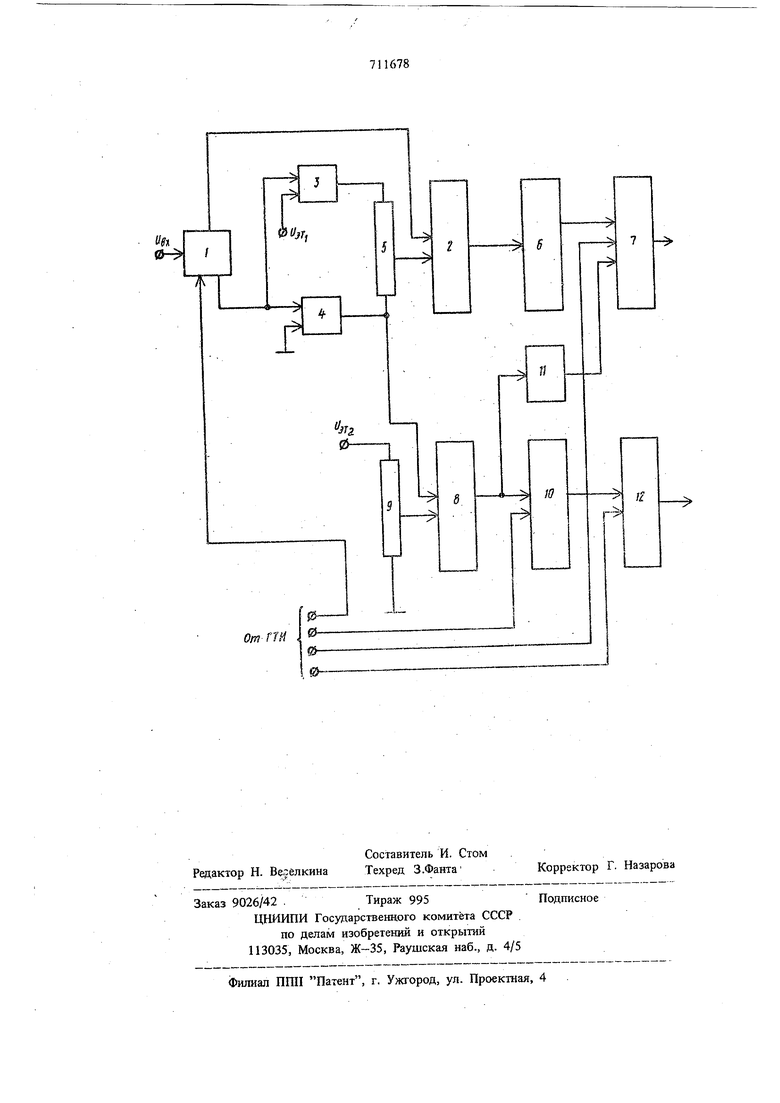

На чертеже изображена структурная электрическая схема аналого-цифрового преобразователя.

Входной сигнал Ug поступает на вход блока 1 выборки и хранения имеющего два выхода, первый из них соединен с одними входами компараторов 2 первого набора, второй с одними из входов дифференциальных усилителей 3, 4, второй вход первого дифференциального усилителя 3 подключен к первому источнику эталонного напряжения Ug-i , второй вход второго дифференциального усилителя 4 соединей с шиной земля, а между выходами дифференциальных усилителей 3, 4 включен резисторный делитель 5 эталонного напряжения, выходы которого подсоединены к второму входу компараторов 2, выход компараторов 2 первого набора соединен с входом первого шифратора 6, последнего соединен с входами первого регистра 7, выход второго дифференциального усилителя 4 -одновременно подключен к первым вхоДаМ компараторов 8 второго набора, а второй вход компараторов 8 соединен с выходом второго резисторного делителя 9 эталонного напряжения Ugj выход компараторов 8 второго набора подсоединен к входу второго шифратора 10 и одновременно к входу логического блока 11. управления, выходы шифратора 10 подключены к входам второго регистра 12, а выход логического блока 11 управления подключен к второму входу первого регистра 7, управляющие входы регистров 7, 8, шифратора 10 и блока 1 выборки и хранения соединены с шинами тактовых импульсов.

Аналого-цифровой преобразователь работает следующим образом.

Входной аналоговый сигнал посгупает на блок 1 выборки и хранения, который производит дискретизацию его во времени. Блок 1 выборки и хранения имеет два независимых выхода. Один из них обеспечивает хранение мгновенного значения входной величины на время цикла преобразования и соединен с входами компараторов 2 первого набора (младшие разряды) . Другой выход блока 1 выборки и хранения выполнен такнм образом, что после времени At, необходимого для срабатывания компаратора, происходит быстрое уменьшение хранимого значения входной величины до нуля, по экспоненте (емкостной разряд). Этот выход подключен к входам дифференциальных усилителей 3, 4,, образующих вместе с резисторами делителя 5 управляемый делитель с Ugj равным величине кванта грубого отсчета.

Итак, после поступления тактового импульса на выходах блока 1 выборки и хранения появляются потенциалы,.соответствующие мгновенному значению входного сигнала. Ввиду того, что Уровни на выходе делителя 5 эталонного напряжения приподняты над уровнем входного сигнала, компараторы 2 первого набора (младшие разряды) сработать не могут. Мгновенное значение входного сигнала со второго выхода блока I выборки и хранения через дифференциальный усилитель 4 поступает на входы компараторов 8 второго набора (старшие разряды) и в течение времени At вызывает срабатывание соответствуюших нз них. Сразу же соответствующая комбинация поступает на вход шифратора 10 и затем в виде двоичного кода записывается в регистр 12 .(по соответствуюшему тактирующему импульсу). В то время, когда срабатывают компараторы В второго набора начинается быстрое уменьшение уровня на вюром выходе блока 1 выборки и хранения и соо1ветственно на входах управляемого делителя. В этом процессе наступит такой момент, когда уровень на одном из входов управляемого делителя, который подключен к выходу второго дифференциального усилителя 4 и одновременно к одним входам компараторов 8 второго набора, станет равным уровню, зафиксированному компараторами 8 второго набора.

Если предположить, что во втором наборе компараторов 8, где осуществляется грубая оценка входного сигнала, сработали два компаратора, тогда уровень входного сигнала лежит между уровнями срабатывания второго и третьего компараторов. Таким образом, если уровень на одном из входов управляемого делителя, который подключен к выходу второго дифференилального усилителя 4 и одновременно к одним входам компараторов 8 второго набора, станет равным уровню срабатьшания втоporo компаратора, a уровни эталонного напряжения на выходах управляемого делителя за полняг зону между, уровнями срабатывания второго и третьего компараторов 8 второго на бора, то в это время количество сработавших компараторов 2 первого набора будет соответствовать более точно измеренной разности меж ду уровнем входного сигнала и уровнем срабатывания второго компаратора 8 второго набора. К выходам компараторов 8 второго набора подключен логический блок 11 управления, необходимый для того, чтобы выработать разрешающий импульс для записи в регистр 7 млад ишх разрядов, в тот момент времени, когда это значение правильно измерено компараторами 2 первого набора. Логический блок 11 управления выполнен таким образом, что он формирует непродолжительный разрешающий импульс только в тот момент, когда какой-ли бо из сработавших компараторов 8 второго на бора возвращается в исходное состояние. Время задержки, сигнала в логическом бло-. ке 11 управления равно задержке в шифраторе, поэтому правильно отсчитанное компараторами 2 первого набора значение входной величины поступает на вход регистра 7 мзгадших разрядов одновременно с разрешающим импульсом и фиксируется. Таким образом время, необходимое для пр

образования входногоаналогового сигнала в цифровой код, в данном устройстве значительно сокращается.

Формула изобретения

Аналого-цифровой преобразователь параллельно-последовательного типа, содержащий два резисторных делителя эталонных напряжений, два набора компараторов, выходы котонапряжения и шиной земля , причем выход компараторов второго набора через логический блок управления соединен с вторым входом первого регистра.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР N 337936, кл. Н 03 К 13/175, 05.10.70.

2.Авторское свидетельство СССР N 407423, кл. Н 03 К 13/18, 23.02.72 (прототип). 8& рых через соответствующие шифраторы соединены с первыми входами соответствующих регистров, управляющие входы которых и управляющий вход второго шифратора соединены с соответствующими шинами тактовых импульсов, отличающийся тем, что, с целью увеличения быстродействия, в него дополнительно введены два дифференциальных усилителя, логический блок управления и блок выборки и хранения, перЁьш и второй входы которого соединены соответственно с шиной входного сигнала и шиной тактовых импульсов, перйый выход блока выборки и хранения соединен с Первым входом i компараторов первого набора, второй выход блока выборки и хранения соединен с первыми входами первого и второго дифференциальных усилителей, вторые входы которых соединены соответственно с первым источником этало1шого напряжения и шиной земля, а вььходы первого и второго дифференциальных усилителей соединены с входами первого резисторного делителя эталонного напряжения, выход которого соединен с вторым входом компараторов первого набора, а выход второго дифференциального усилителя соединен также с первым входом компараторов второго набора, второй вход которого соединен с выходом второго резисторного делителя эталонного напряжения, входы которого соединены со;ответственно с вторым источником эталонного

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство аналого-цифрового преобразования узкополосных сигналов | 1984 |

|

SU1225014A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU938396A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1181144A1 |

| УСТРОЙСТВО ОБРАБОТКИ АНАЛОГОВЫХ СИГНАЛОВ С ПРИМЕНЕНИЕМ ЦИФРОВОЙ ФИЛЬТРАЦИИ | 2021 |

|

RU2777306C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО КОНТРАСТИРОВАНИЯ ТЕЛЕВИЗИОННОГО ИЗОБРАЖЕНИЯ | 2002 |

|

RU2233044C2 |

| Устройство предварительного автоматического контроля изоляции участка электрической сети | 1989 |

|

SU1661686A2 |

| Аналого-цифровой преобразователь | 1982 |

|

SU1102033A1 |

| МНОГОКАНАЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1973 |

|

SU400021A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU809555A1 |

| Измерительный преобразователь для тензорезисторных весоизмерительных устройств | 1990 |

|

SU1830463A1 |

Авторы

Даты

1980-01-25—Публикация

1977-05-05—Подача