1

Изобретение относится к области микроэлек,троники, автоматики, цифровой измерительной и вычислительной техники и может быть использовано в качестве счетного устройства при построении различных счетчиков, преобразователей.

Известны триггеры, выполненные на МДПтранзисторах 1.

Недостаток известных устройств заключается в том, что они не обеспечивают режима пересчета.

Известен также квазистатический триггер на МДП-транзисторах, который обеспечивает режим прямого счета, но не обеспечивает режим реверсивного счета и формирование импульсов переноса прямого и обратного счета на последующие разряды 2.

Целью изобретения является обеспечение реверсивного счета и формирования импульсов переноса на последующий разряд.

Дпя достижения поставленной цели в устрой ство, содержащее первый инвертор, выход которого подключен ко входу второго инвертора, а вход - к выходу второго инвертора через первый проходной транзистор, дополнительно введены проходные транзисторы, двухтактный усилитель, содержащий два последовательно включенных между шинами питания Транзистора, и формирователи импульсов переноса прямого и обратного счета, каждый из которых содержит последовательно включе1шые повторяющий и ключевой транзисторы, подключенные соответственно между входной шиной прямого или обратного счета и общей шиной, причем второй проходной транзистор включен между выходом первого инвертора и затворами первого транзистора усилителя и повторяющего транзистора формирователя импульсов переноса прямого счета, третий проходной транзистор включен между выходом второго инвертора и затворами второго транзистора усилителя и ключевого транзистора формирователя импульсов переноса прямого счета и затвором повторяющего транзистора формирователя импульсов переноса обратного счета череЗ четвертый приходной транзистор, затворы первого, второго, третьего и четвертого проходных транзисторов подключены ко входной шине инверсных сигналов прямого и обратного счета пятый и шестой проходные транзисторы включены между выходом усилителя и входом первого инвертора, затвор пятого проходного транзистора подключен ко входной шине прямого счета, а затвор шестого проходного транзистора подключен ко входной ишне обратного счета, выход усилителя подклюkeH к затвору ключевого транзистора формирователя импульсов переноса обратного счета, между затворами и истоками повторяющих транзис торов формирователей импульсов переноса прямого и обратного счета включены запоминающие конденсаторы, истоки повторяющих транзисторов подключены соответственно к выходным шинам прямого и обратного счета.

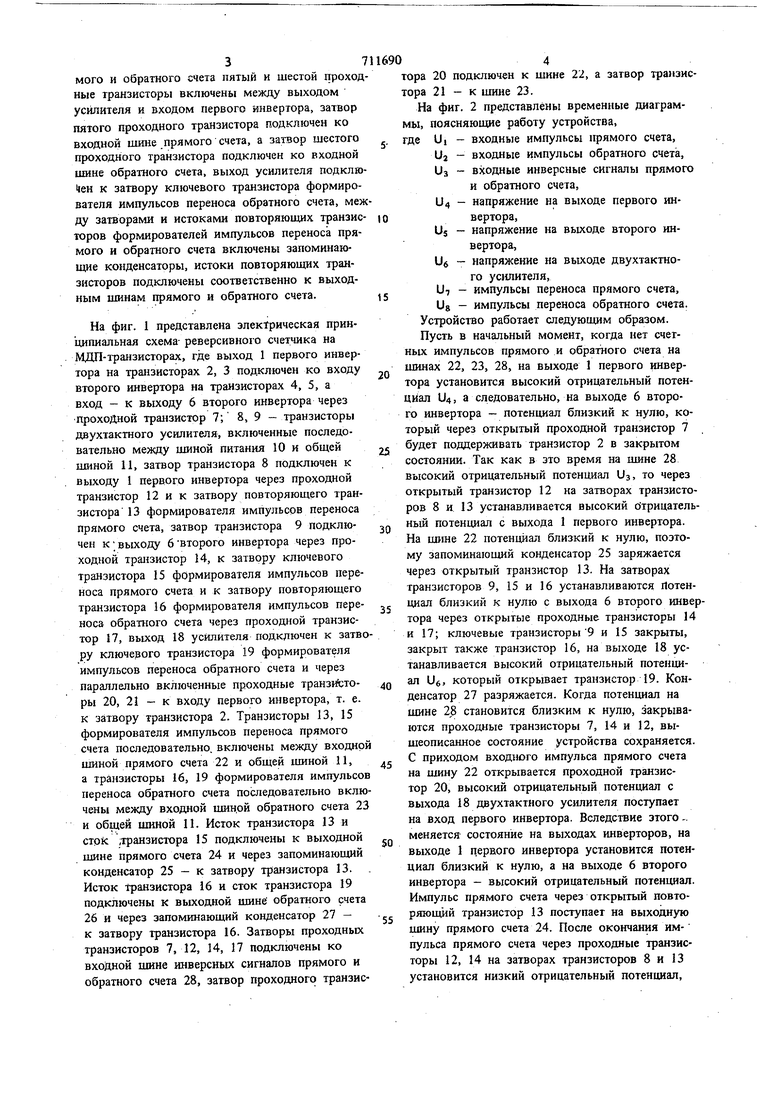

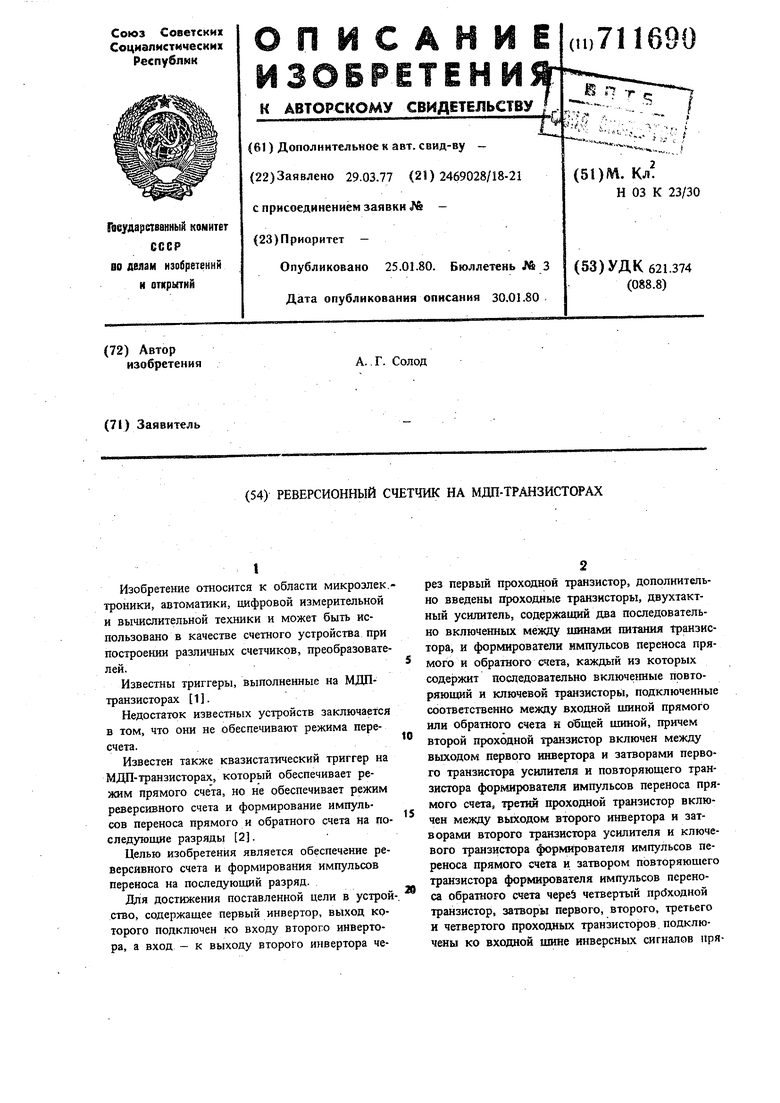

На фиг. 1 представлена электрическая принципиальная схема- реверсивного счетчика на МДП-транзисторах, где выход 1 первого инвертора на транзисторах 2, 3 подключен ко входу второго инвертора на транзисторах 4, 5, а вход - к выходу 6 второго инвертора через проходной транзистор 7; 8, 9 - транзисторы двухтактного усилителя, включенные последовательно между шиной питания 10 и общей шиной И, затвор транзистора 8 подключен к выходу 1 первого инвертора через проходной транзистор 12 и к затвору повторяющего транзистора 13 формирователя импульсов переноса прямого счета, затвор транзистора 9 подключен к выходу 6 второго инвертора через проходной транзистор 14, к затвору ключевого транзистора 15 формирователя импульсов переноса прямого счета и к затвору повторяющего транзистора 16 формирователя импульсов переноса обратного счета через проходной транзистор 17, выход 18 усилителя подключен к затвору ключевого транзистора 19 формирователя импульсов переноса обратного счета и через параллельно включенные проходные транзЛторы 20, 21 - к входу первого инвертора, т. е. к затвору транзистора 2. Транзисторы 13, 15 формирователя импульсов переноса прямого счета последовательно, включены между входной шиной прямого счета 22 и общей тиной 11, а транзисторы 16, 19 формирователя импульсов переноса обратного счета последовательно включены между входной шиной обратного счета 23 и обиден шиной П. Исток транзистора 13 и сток ;транзистора 15 подключены к выходной шине прямого счета 24 и через запоминающий конденсатор 25 - к затвору транзистора 13. Исток транзистора 16 и сток транзистора 19 подключены к выходной шине обратного счета 26 и через запоминающий конденсатор 27 - к затвору транзистора 16. Затворы проходных транзисторов 7, 12, 14, 17 подключены ко входной шине инверсных сигналов прямого и обратного счета 28, затвор проходного транзистора 20 подключен к шине 22, а затвор транзистора 21 - к шине 23.

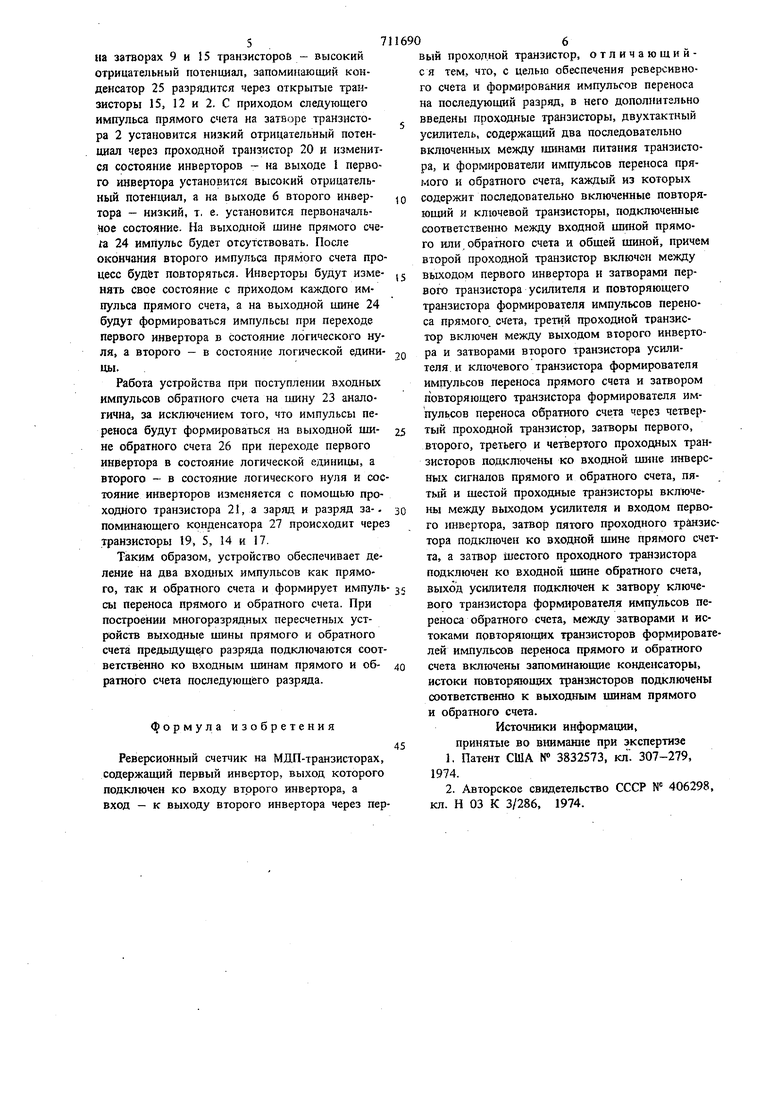

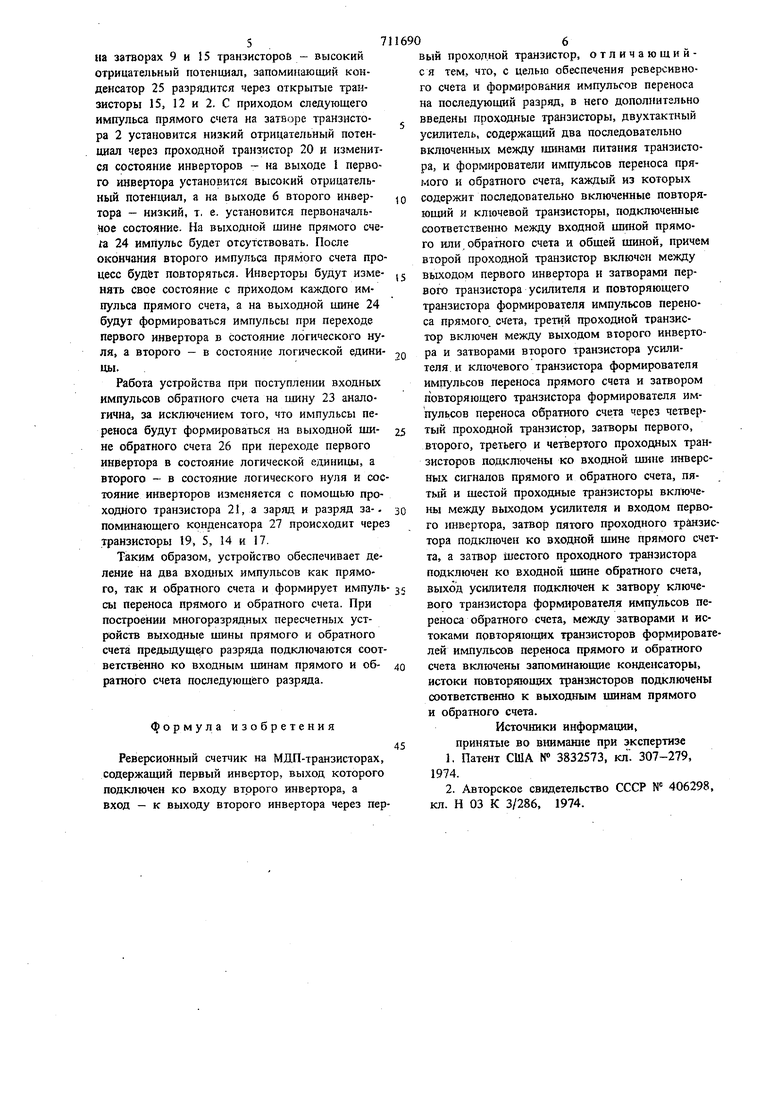

На фиг. 2 представлены временные диаграммы, поясняющие работу устройства, где Ui - входные импульсы прямого счета,

Ui - входные импульсы обратного счета,

Us - входные инверсные сигналы прямого и обратного счета,

и - напряжение на выходе первого инвертора,

Uj - напряжение на выходе второго инвертора,

Ue - напряжение на выходе двухтактного усилителя,

U - импульсы переноса прямого счета,

Ug - импульсы переноса обратного счета. Устройство работает следующим образом. Пусть в начальный момент, когда нет счетных импульсов прямого и обратного счета на шинах 22, 23, 28, на выходе 1 первого инвертора установится высокий отрицательный потенциал U4, а следовательно, на выходе 6 второго инвертора - потенциал близкий к нулю, который через открытый проходной транзистор 7 будет поддерживать транзистор 2 в закрытом состоянии. Так как в зто время на шине 28 высокий отрицательный потенциал Ua, то через открытый транзистор 12 на затворах транзисторов 8 и 13 устанавливается высокий отрицательньш потенциал с выхода 1 первого инвертора. На шине 22 потенциал близкий к нулю, поэтому запоминающий конденсатор 25 заряжается через открытый транзистор 13. На затворах транзисторов 9, 15 и 16 устанавливаются Потенциал близкий к нулю с выхода 6 второго инветора через открытые проходные транзисторы 14 и 17; ключевые транзисторы9 и 15 закрыты, закрыт также транзистор 16, на выходе 18 устанавливается высокий отрицательный потенциал Ufi, который открывает транзистор 19. Конденсатор 27 разряжается. Когда потенциал на шине 2,8 становится близким к нулю, закрываются проходные транзисторы 7, 14 и 12, вышеописанное состояние устройства сохраняется. С приходом входного импульса прямого счета на шину 22 открывается проходной транзистор 20, высокий отрицательный потенциал с выхода 18 двухтактного усилителя поступает на вход первого инвертора. Вследствие этого -. меняется- состояние на выходах инверторов, на выходе 1 первого инвертора установится потенциал близкий к нулю, а на выходе 6 второго инвертора - высокий отрицательный потенциал. Импульс прямого счета через открытый повторяющий транзистор 13 поступает на выходную шину прямого счета 24, После окончания импульса прямого счета через проходные транзисторы 12, 14 на затворах транзисторов 8 и 13 установится низкий отрицательный потенциал. на затворах 9 и 15 транзисторой - высокий отрицательный потенциал, запоминающий конденсатор 25 разрядится через открытые транзисторы 15, 12 и 2. С приходом следующего импульса прямого счета на затворе транзистора 2 установится низкий отрицательный потенциал через проходной транзистор 20 и изменится состояние инверторов на выходе 1 первого инвертора установится высокий отрицательный потенвдал, а на выходе б второго инвертора - низкий, т, е. устаноактся первоначальное состояние. На выходной шине прямого снега 24 импульс будет отсутствовать. После окончания второго импульса прямого счета про цесс будбт повторяться. Инверторы будут изменять свое состояние с приходом каждого импульса прямого счета, а на выходной шине 24 будут формироваться импульсы при переходе первого инвертора в состояние логического нуля, а второго - в состояние логической единиЦЫ. Работа устройства при поступлении входных импульсов обратного счета на шину 23 аналогична, за исключением того, что импульсы переноса будут формироваться на выходной шине обратного счета 26 при переходе первого инвертора в состояние логической единицы, а второго - в состояние логического нуля и сос тояние инверторов изменяется с помощью проходного транзистора 21, а заряд и разряд за-, поминающего конденсатора 27 происходит чере транзисторы 19, 5, 14 и 17. Таким образом, устройство обеспечивает деление на два входных импульсов как прямого, так и обратного счета и формирует импуль сы переноса прямого и обратного счета. При построении многоразрядных пересчетных устройств выходные шины прямого и обратного счета предыдущ о разряда подключаются соответственно ко входным шинам прямого и обратного счета последующего разряда. О ормула изобретения Реверсионный счетчик на МДП-транзисторах, содержащий первый инвертор, выход которого подключен ко входу второго инвертора, а вход - к выходу второго инвертора через пер ВЫЙ проходной транзистор, отличающийся тем, что, с целью обеспечения реверсивного счета и формирования импульсов переноса на последующий разряд, в него дополнительно введены проходные транзисторы, двухтактный усилитель, содержащий два последовательно включенных между Д1шами питания транзистора, и формирователи импульсов переноса прямого и обратного счета, каждый из которых содержит последовательно включенные повторяющий и ключевой транзисторы, подключенные соответственно между входной штюй прямого или обратного счета и обшей шиной, причем второй проходной транзистор включен между вь1ходом первого инвертора и затворами первого транзистора усилителя и повторяющего транзистора формирователя импульсов переноса прямого, счета, третий проходной транзистор включен между выходом второго инвертора и затворами второго транзистора усилителя, и ключевого транзистора формирователя импульсов переноса прямого счета и затвором повторяющего транзистора формирователя импульсов переноса обратного счета через четвертый проходной транзистор, затворы первого, второго, третьего и четвертого проходных транзисторов подключены ко входной шине инверсных сигналов прямого и обратного счета, пятый и щестой проходные транзисторы включены между выходом усилителя и входом первого инвертора, затвор пятого проходного транзистора подключен ко входной шине прямого счетта, а затвор шестого проходного транзистора подключен ко входной шине обратного счета, выход усилителя подключен к затвору ключевого транзистора формирователя импульсов переноса обратного счета, между затворами и истоками повторяющих транзисторов формирователей импульсов переноса прямого и обратного счета включены запоминающие конденсаторы, истоки повторяющих транзисторов подключены соответственно к выхощпым шинам прямого и обратного счета. Источники информации, принятые во внимание при экспертизе 1,Патент США N 3832573, кл. 307-279, 1974. 2.Авторское свидетельство СССР N 406298, кл. Н 03 К 3/286, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсный генератор (его варианты) | 1980 |

|

SU911693A1 |

| Квазистатическое счетное устройство на МДП-транзисторах | 1986 |

|

SU1319255A1 |

| Формирователь тактовых импульсов | 1975 |

|

SU566355A1 |

| Устройство формирования импульсов на МДП-транзисторах | 1986 |

|

SU1345339A1 |

| Устройство формирования импульсов на МДП-транзисторах | 1985 |

|

SU1277380A1 |

| Квазистатический счетный триггер на мдп-транзисторах | 1975 |

|

SU632060A1 |

| Усилитель-формирователь на металло= диэлектрических полупроводниковых транзисторах | 1974 |

|

SU531284A2 |

| Усилитель-формирователь импульсов | 1980 |

|

SU944110A1 |

| Формирователь импульсного сигнала по переднему и заднему фронтам адресных сигналов на МОП -транзисторах | 1985 |

|

SU1381694A1 |

| Формирователь импульсов на моп-транзисторах | 1978 |

|

SU790335A1 |

Авторы

Даты

1980-01-25—Публикация

1977-03-29—Подача