Изобретение oTiiociiTCH к импульсной технике.

Известен квазистатическ.чй триггер на M,iri-T|inH3HCTOi)ax, содержниип три инвертора на МДГ1- транзисторах и уиравляющие Л ДГ1-транзистор1 1 1 .

Недостатком данного триггера является невозможность работы в режиме цересчета.

Наиболее близок к предлагаемому квазистат 1ческий триггер, содержащий входной инвертор на двух иоследовательно соединенных транзисторах, выход которого соединен со входом выходного инвертора, а вход - с выходом выходного инвертора через проходной транзистор, иричем затвор проходного транзистора соединен с тактовой шиной триггера, и три управляющих транзистора, затворы двух из которых соединены с тактовой шиной триггера, а затвор третьего связан со счетной шиной триггера 2.

Этот триггер не формирует имиульсов переноса на последующий разряд и при последовательном соединении счетных триггеров требуются дополнительные блоки формирования имнульсов переноса.

Цель изобретения - формирование импульсов переноса.

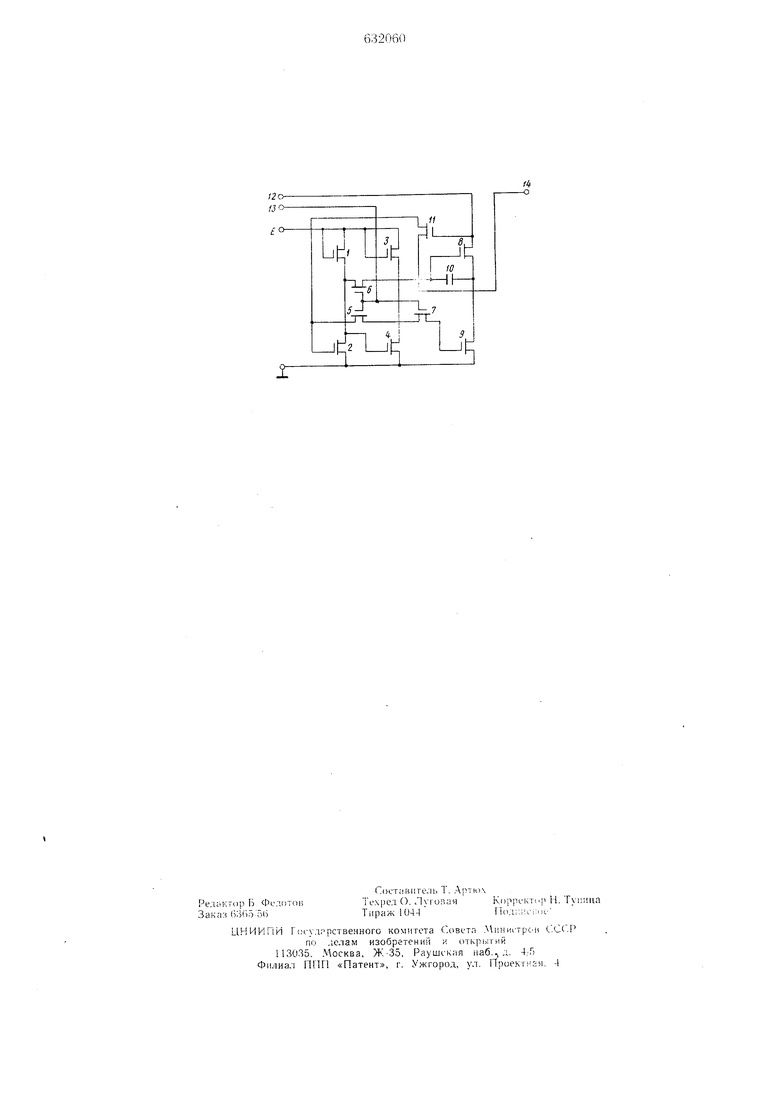

Поставленная цель достигается тем, что в квазистатический триггер на МДП-транзисторах, содержащий входной инвертор на двух последовательно соединенных транзисторах, выход которого соединен со входом выходного инвертора, а вход - с его выходом через проходной транзистор, причем затвор проходного транзистора соединен с тактовой шиной триггера, и три упраатяющие транзистора, затворы двух из которых соединены с гактовой шиной триггера, а затвор третьего связан со счетной шиной триггера, введены дополнительные повторяющий и ключевой МДП-транзисторы и конденсатор, причем сток повторяющего транзистора соединен со счетной щиной триггера, исток - с выходом триггера и со стоком ключевого транзистора, затвор повторяющего транзистора - со стоком первого управляющего транзистора, а затвор ключевого транзистора -со стоком второго управляюп1его транзистора, причем конденсатор включен между истоком и затвором повторяющего транзистора, а третий правляющий транзистор - между выходом триггера и входом входного инвертора. П р и н ц и ;in a.i ы i а я э;1 сктр кч ее ка я схе м а онисьваемого триггера при.ведена на чертеже. Триггер содержит входной инвертор на МДП-транзисторах , 2, выходной инвертор на МДП-транзисторах 3, 4 проходной AlZUi-Tpai 3ncTop 5, управ;1яюни1е Л ДПтра ызисторы -, 1. повторя1о;н, Л1;,11-гранзисгО|) 8. ключевой МДП-транзистор 9, конденсатор iO и управ; яю ций МДП-транзистор .Ма iHHiiy 12 подают актовгяе нмну;1ЬС1 1, на 13 -- счетные и.,тьсы. F- абота триггера заключается в следуюHiCM. Koivia нет счетного импульса на uiHпе 13, на выходе входного инвертора имеется высокий отрииател1)|1ый иотеиниа.т, на выходе выходного инвертора -- низкий отрицательный, на входе входного инве ггора - низкий нотени ал. Так как в этот момен нроходной МДИгранзистор 5 открыт отринател; 11ьгч иотенциало.м на HiHiie тактовьгх нмиу.и.сон 12, следуюн.их в нрот11во{|) со счетными . , то ЭТО состоянис устойчивое, и открьггые транзисторы 6 и 7 на обк.тдка ч конденсатора 10 соотиетственио устанав.иваются высокий и низкий отрниате/идн С нотекниа.и.. Высок;.Й отрицательный потенциал открывает иовторяющий МДП-транзистор 8 и, так как ;а тине КЗ в это время отсутствует счетн1)1Й , т.е. имеется низкий отриц.ч.е.. иотснц ал, то на в лходе 14 также низкий отрр 1ательный потенциал. К.онденсатор заряжается такн.м образом, что на его обкладке, иодк.поченной к затвору IIOBторяюнего МДГ1-транз СТОра, более OT|iiiцатсльи1) поте.чи.иал, нем на другой об1.|ал,ке. С п;И1хо. счетного i:Mii .ibca т)анзисторы о -7 закрып.-ются, но состояние первого иивертС)),:; ;;:-)м ииается на копдене торе ii. ii траиз1 стор 8 остаегся закрытым. - е|1ез He.io счетный импульс передается на выход, а через открытый TpaiKiiiCTOp 1 на входе ВХОДН01-0 инвертора усг,; навлнвается отрицательиое нанряжение. н на выходе входно -о 1 11ве{)тора оказываетея низкий отр11цате. потенциал, а на выходе выхс..тного - высокий. После окончания импульса на выхСДе 4 устанавливается низкий иотснниа,. iloc.ie окончаиия счетного импульса открьн- пиг|-ся транзисторы 5- 7. Пр-и чтом траизис ()р -1 поддерживает становивн1ееся состояние, а транзисторы 6. / устанавливают соответстр,енно на затворах транзисторов инзкнй и высокий отрицательный потенциалы. Конденсатор 10 разряжается через транзисторы 9, 6 и 2. С приходом следующего счетного импульса транзисторы 5-7 закрываются, а транзистор 1 1 открывается. В этот мо.мент транзистор 9 открыт, а транзистор 8 закрыт. Следовательно, на выходе 14 - низкий отрицательный потенциал, на вы.ходе входного инвертора - высокий отрицательный иотенциал. на выходе выходного - низкий.. После окончания счетного импульса триггер устанавливается в первоначальное состояние и с приходом очередного сметного имиульса цикл иовторяетФормула изобретения Квазистатическнй счетный триггер на МДГ -траизисторах, содержащий входиой инвертор на двух последовательно соединенных транзисторах, выход которого соединен со входом выходного инвертора, а вход - с его вьгходо.м через нроходиой транзистор, иричем затвор проходного транзистора соединен с тактовой щпной триггера, и три управляющих транзистора, затворы двух из которых соединены с тактовой щиной триггера, а затвор третьего связан со счетной ши}1ой триггера, отличающийся те.м, что, с целью формирования имиульса переноса, в него введены допо..тнительные гювторяющий и ключевой МДП-транзисторы и конденсатор, причем сток повторяющего транзистора соединен со счетной щиной триггера, исток- с выходом триггера и со стоком ключевого транзистора, затвор повторяющего транзистора - со стоком первого хтпзавляющего транзистора, а затвор ключевого транзистора -- со стоком второго управляюптего транзистора, причем конденсатор включен межд истоком и затвором повторяющего транзистора, а третий управляющий транзистор - между выходом триггера и входом в.ходного инвертора. Источники информации, принятые во вни.мание при экспертизе: 1.Патент США № 3832578, кл. 307--279, 27.08.74. 2.Авторское свидете,аьство СССР ЛЬ 406293, Н 03 К 3/286, 14.08.73.

| название | год | авторы | номер документа |

|---|---|---|---|

| Квазистатическое счетное устройство на МДП-транзисторах | 1986 |

|

SU1319255A1 |

| Реверсивный счетчик на мдп-транзисторах | 1977 |

|

SU711690A1 |

| Формирователь сигнала выборки на МДП-транзисторах | 1986 |

|

SU1338024A1 |

| Ячейка памяти для регистра сдвига | 1972 |

|

SU503295A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Элемент памяти для регистра сдвига | 1978 |

|

SU706880A1 |

| Ячейка памяти на МДП транзисторах | 1981 |

|

SU968854A1 |

| Формирователь выходного сигнала на МДП-транзисторах | 1986 |

|

SU1338055A1 |

| Устройство формирования импульсов на МДП-транзисторах | 1986 |

|

SU1345339A1 |

| Формирователь тактовых импульсов | 1975 |

|

SU566355A1 |

Авторы

Даты

1978-11-05—Публикация

1975-08-18—Подача