(54) ФАЗОВЫЙ ДИСКРИМИНАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Фазовый дискриминатор | 1981 |

|

SU970634A1 |

| Фазовый дискриминатор | 1986 |

|

SU1334355A1 |

| Анализатор плотности распределения случайной фазы сигнала | 1978 |

|

SU737862A1 |

| КОМПЛЕКСНЫЙ ИЗМЕРИТЕЛЬ ДАЛЬНОСТИ | 1992 |

|

RU2018861C1 |

| Устройство для стабилизации частоты вращения электродвигателя | 1989 |

|

SU1686681A1 |

| ДЕМОДУЛЯТОР МНОГОПОЗИЦИОННЫХ СИГНАЛОВ | 2003 |

|

RU2246794C1 |

| Электропривод постоянного тока | 1981 |

|

SU995247A1 |

| ФАЗОВЫЙ ДИСКРИМИНАТОР | 2013 |

|

RU2541899C1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ОБЪЕМНОГО РАСХОДА ВЕЩЕСТВ С ПОМОЩЬЮ УЛЬТРАЗВУКОВЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1999 |

|

RU2169906C2 |

| ЦЕЗИЕВЫЙ СТАНДАРТ ЧАСТОТЫ | 1994 |

|

RU2076411C1 |

1

Изобретение относится к измерительной технике, может быть использовано для измерения разности фаз двух напряжений.

Известен фазовый дискриминатор, содержащий триггер, две трехвходовые схемы совпадения, инверторы входного и опорного сиг: налов и сумматор; при этом два входа одной схемы совпадения соединены с источником входного сигнала и выходом инвертор а опорного сигнала соответственно, третий ее вход соединен с прямым выходом триггера, два входа второй схемы совпадения соединены с источником опорного сигнала и выходом инвертора входного сигнала соответственно 1.

Однако известный фазовый дискриминатор сложен и поэтому недостаточно надежен.

Цель изобретения - упрощение и повышение надежности схемы.

Для этого в фазовом дискриминаторе, содержащем триггер, две трехвходовые схемы совпадения, инверторы входного и опорного сигналов и сумматор, причем дйа входа одной схемы совпадения соединены с источником входного сигнала и выходом инвертора опорного сигнала соответственно.

третий ее вход соединен с прямым выходом триггера, два входа второй схемы совпадения соединены с источником опорного сигнала и выходом инвертора входного сигнала соответственно, fpeтий ее вход совпадения соединен с инверсным выходом триггера, выходы схем сбвпаденйя подключены ко входам сумматора,а входы триггера подключены к выходамдвухдополнигельно введенных схем совпадения, два входа каждой из которых соединены с выходами инверторов входного и опориого сигналов, а третьи входы подключены к источнику входного и опорного сигййлов соответствённо.

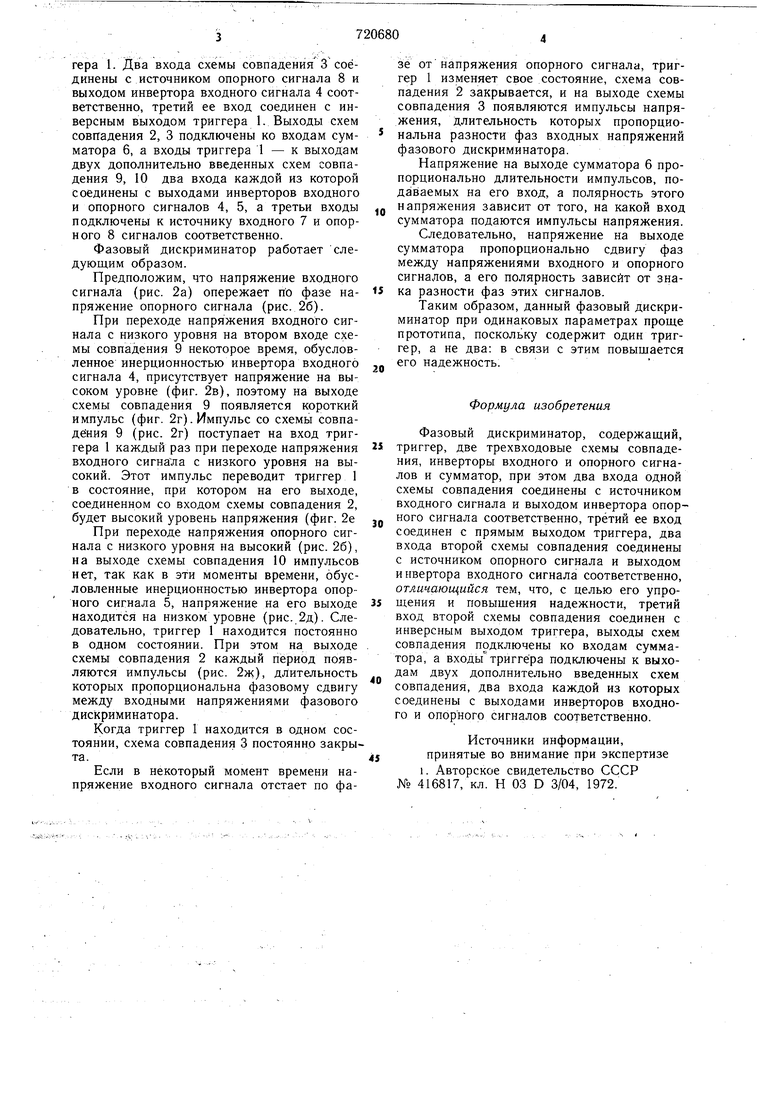

На фиг. 1 изображена структурная электрическая схема фазового дискриминатора, на фиг. 2 изображены временные диаграммы поясняющие работу схемы.

Фазовый дискриминатор содержит триггер 1, две трехвходовые схемы совпадения 2, 3, инверторы входного и опорного сигналов 4, 5 и сумматор 6, причем два входа схемы совпадения 2 соединены с источником входного сигнала 7 и выходом инвертора опорного сигнала 5 соответственно, третий ее вход соединен с прямым выходом триггера 1. Два входа схемы совпадения 3 соединены с источником опорного сигнала 8 и выходом инвертора входного сигнала 4 соответственно, третий ее вход соединен с инверсным выходом триггера 1. Выходы схем совпадения 2, 3 подключены ко входам сумматора 6, а входы триггера 1 - к выходам двух дополнительно введенных схем совпадения 9, 10 два входа каждой из которой соединены с выходами инверторов входного и опорного сигналов 4, 5, а третьи входы подключены к источнику входного 7 и опорного 8 сигналов соответственно.

Фазовый дискриминатор работает следующим образом.

Предположим, что напряжение входного сигнала (рис. 2а) опережает по фазе напряжение опорного сигнала (рис. 26).

При переходе напряжения входного сигнала с низкого уровня на втором входе схемы совпадения 9 некоторое время, обусловленное инерционностью инвертора входного сигнала 4, присутствует напряжение на высоком уровне (фиг. 2в), поэтому на выходе схемы совпадения 9 появляется короткий импульс (фиг. 2г). Импульс со схемы совпадения 9 (рис. 2г) поступает на вход триггера 1 каждый раз при переходе напряжения входного сигна ла с низкого уровня на высокий. Этот импульс переводит триггер 1 в состояние, при котором на его выходе, соединенном со входом схемы совпадения 2, будет высокий уровень напряжения (фиг. 2е

При переходе напряжения опорного сигнала с низкого уровня на высокий (рис. 26), на выходе схемы совпадения 10 импульсов нет, так как в эти моменты времени, обусловленные инерционностью инвертора опорного сигнала 5, напряжение на его выходе находится на низком уровне (рис. 2д). Следовательно, триггер 1 находится постоянно в одном состоянии. При этом на выходе схемы совпадения 2 каждый период появляются импульсы (рис. 2ж), длительность которых пропорциональна фазовому сдвигу между входными напряжениями фазового дискриминатора.

Когда триггер 1 находится в одном состоянии, схема совпадения 3 постоянно закрыта.

Если в некоторый момент времени напряжение входного сигнала отстает по фазе от напряжения опорного сигнала, триггер 1 изменяет свое состояние, схема совпадения 2 закрывается, и на выходе схемы совпадения 3 появляются импульсы напряжения. Длительность которых пропорциональна разности фаз входных напряжений фазового дискриминатора.

Напряжение на выходе сумматора 6 пропорционально длительности импульсов, подаваемых на его вход, а полярность этого напряжения зависит от того, на какой вход сумматора подаются импульсы напряжения.

Следовательно, напряжение на выходе сумматора пропорционально сдвигу фаз между напряжениями входного и опорного сигналов, а его полярность зависит от знака разности фаз этих сигналов.

Таким образом, данный фазовый дискриминатор при одинаковых параметрах проще прототипа, поскольку содержит один триггер, а не два: в связи с этим повышается его надежность.

Формула изобретения

Фазовый дискриминатор, содержащий, триггер, две трехвходовые схемы совпадения, инверторы входного и опорного сигналов и сумматор, при этом два входа одной схемы совпадения соединены с источником входного сигнала и выходом инвертора опорного сигнала соответственно, третий ее вход соединен с прямым выходом триггера, два входа второй схемы совпадения соединены с источником опорного сигнала и выходом инвертора входного сигнала соответственно, отличающийся тем, что, с целью его упрощения и повышения надежности, третий вход второй схемы совпадения соединен с инверсным выходом триггера, выходы схем совпадения подключены ко входам сумматора, а входьГ триггера подключены к выходам двух дополнительно введенных схем совпадения, два входа каждой из которых соединены с выходами инверторов входного и опорного сигналов соответственно.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 416817, кл. Н 03 D 3/04, 1972.

, г

«; Г

,

0/7(7. С

;

USbix.unS

;

AbiKMH i

г;

.хЗ

;

„(&ык. триг

;ff) ивых СХ.2

ч ч

II I

14

Г

ж

ч-q

Авторы

Даты

1980-03-05—Публикация

1977-01-05—Подача