(54) БАЗОВЫЙ ДИСКРИМИНАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ФАЗИРОВАНИЯ ШКАЛЫ ВРЕМЕНИ ЭЛЕКТРОННЫХ ЧАСОВ | 1994 |

|

RU2084944C1 |

| Фазовый дискриминатор | 1986 |

|

SU1334355A1 |

| Фазовый дискриминатор | 1988 |

|

SU1598109A1 |

| Система цикловой синхронизации для многоканальных систем связи | 1988 |

|

SU1598193A1 |

| Цифровой фазовый дискриминатор | 1975 |

|

SU602881A1 |

| Фазовый дискриминатор | 1977 |

|

SU720680A1 |

| Преобразователь кода в скорость вращения вала | 1988 |

|

SU1599991A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Источник питания фазовой следящей системы | 1984 |

|

SU1238027A1 |

| ФАЗОВЫЙ ДИСКРИМИНАТОР | 2013 |

|

RU2541899C1 |

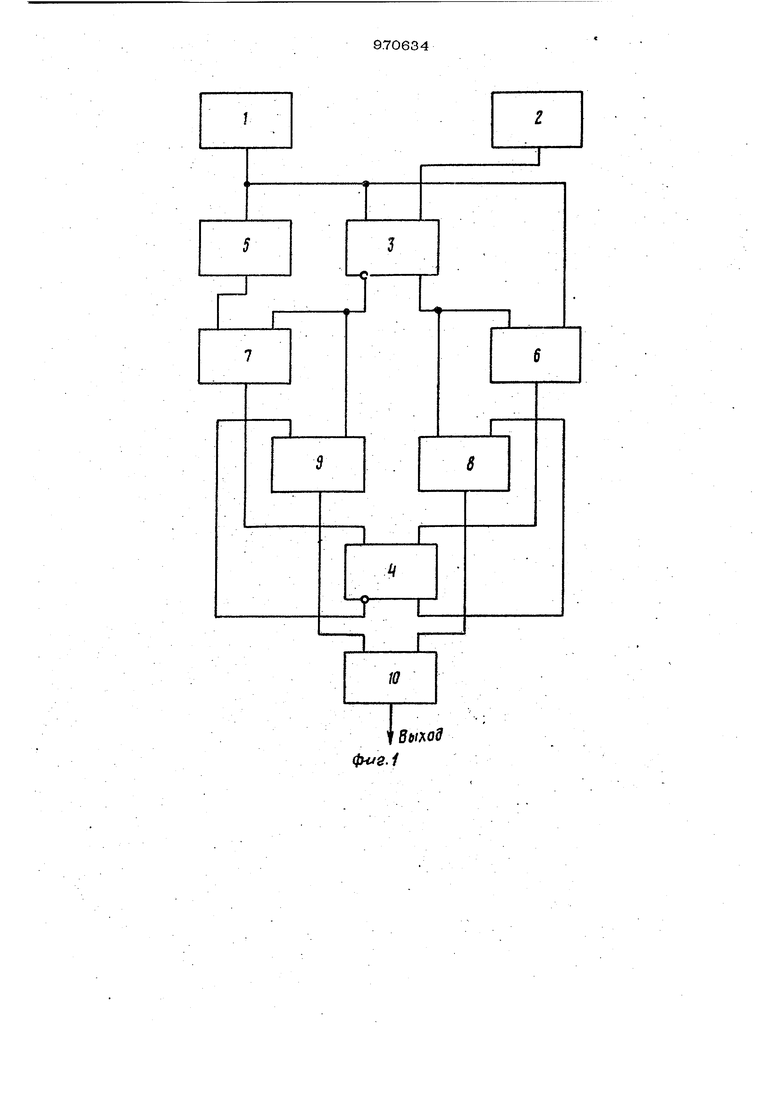

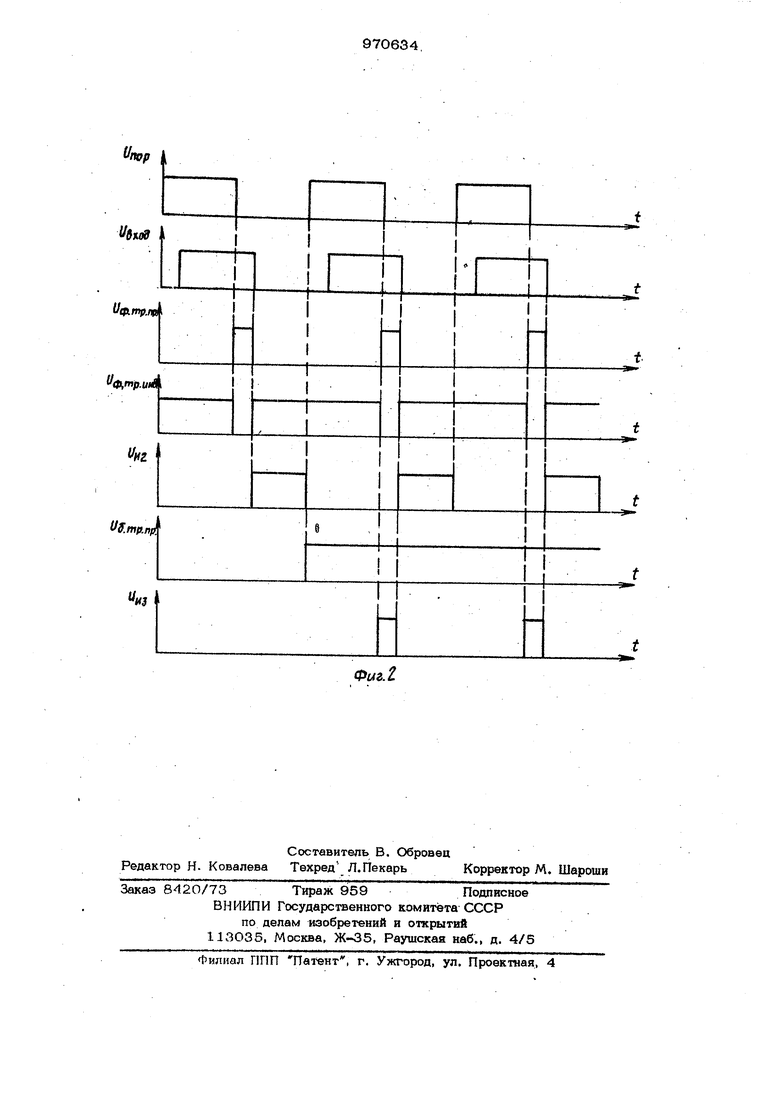

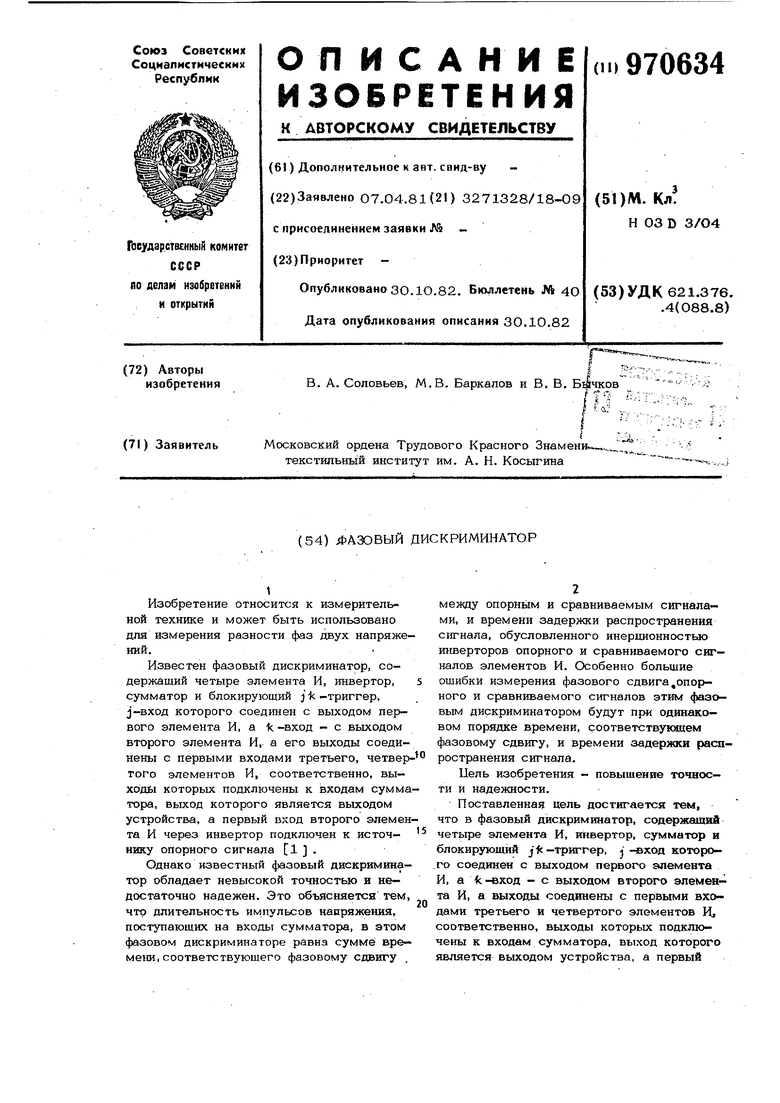

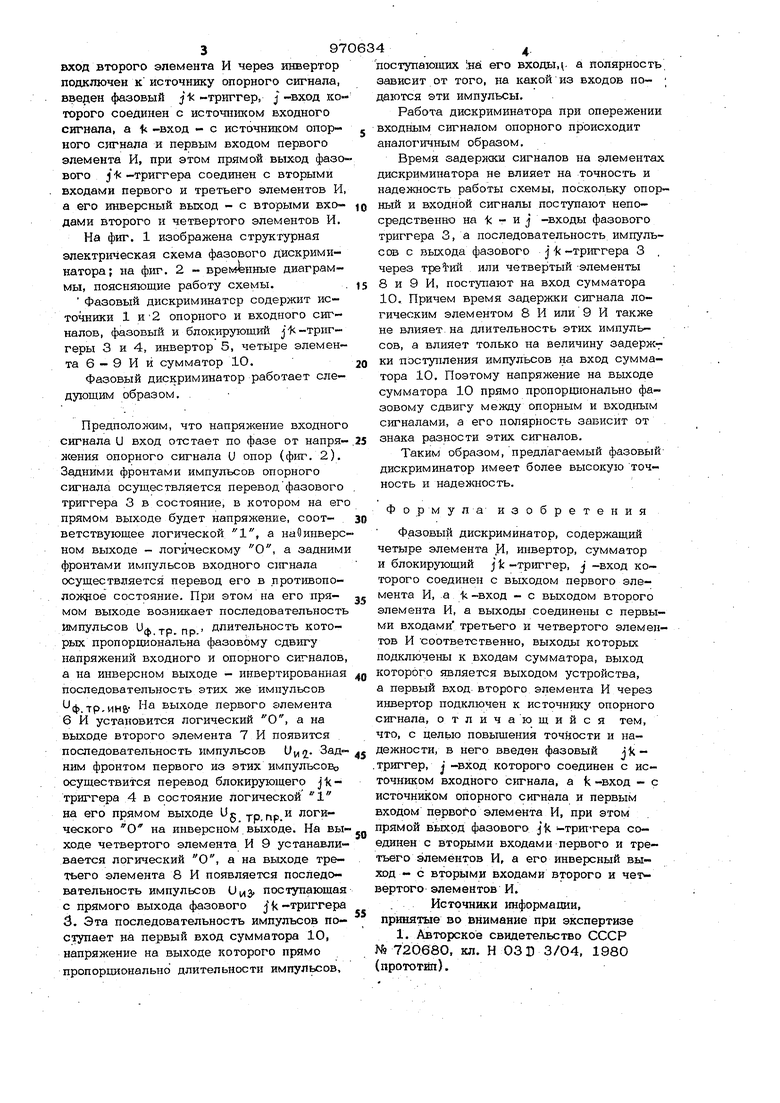

Изобретение относится к измерительной технике и может быть использовано для измерения разности фаз двух напряже ний. Известен фазовый дискриминатор, содержащий четыре элемента И, инвертор, сумматор и блокирующий j -триггер, J-вход которого соединен с выходом первого элемента И, а k -вход - с выходом второго элемента И, а его выходы соединены с первыми входами третьего, четвер того элементов И, соответственно, выходы которых подключены к входам сумма тора, выход которого является выходом устройства, а первый вход второго элемен та И через инвертор подключен к источнику опорного сигнала 1 . Однако известный фазовый дискриминатор обладает невысокой точностью и недостаточно надежен. Это объясняетсятем что длительность импульсов напряжения, поступающих на входы сумматора, в этом фазовом дискриминаторе равна сумме времени, соответствующего фазовому сдвигу между опорнь1м и сравниваемым сигналами, и времени задержки распространения сигнала, обусловленного инерционностью инверторов опорного и сравниваемого сигналов элементов И. Особенно большие ощибки измерения фазового сдвига,опорного и сравниваемого сигналов этим фазовым дискриминатором будут при одинаковом порядке времени, соответствующем фазовому сдвигу, и времени задержки распространения сигнала. Цель изобретения - повышенна точности и надежности. Поставленная цель достигается тем, что в фазовый дискриминатор, содержащий четыре элемента И, ршвертор, сумматор и блокирующий J -триггер, j -вход которого соединен с выходом первого элемента И, а -вход - с выходом второго элемента И, а выходы соединены с первыми входами третьего и четвертого элементов Ц, соответственно, выходы которых подключены к входам сумматора, выход которого является выходом устройства, а первый 397 вход второго элемента И через инвертор подключен к источнику опорного сигнала, вверен фазовый jk -триггер, J -вход которого соединен с источником входного сигнала, а 1 -вход - с источником опорного сигнала и первым входом первого элемента И, при этом прямой выход фазо вого jk -триггера соединен с вторыми входами первого и третьего элементов И, а его инверсный выход - с вторыми входами второго и четвертого элементов И. На фиг. 1 изображена структурная электрическая схема фазового дискриминатора; на фиг. 2 - временные диаграммы, поясняющие работу схемы. Фазовый дискриминатор содержит источники 1 и 2 опорного и входного сигналов, фазовый и блокирующий j-1 -триггеры 3 и 4, инвертор 5, четыре элемента 6 - 9 И и сумматор 10. Фазовый дискриминатор работает следующим образом. Предполо:ншм, что напряжение входного сигнала и вход отстает по фазе от напряжения опорного сигнала U опор (фиг. 2). Задними фронтами импульсов опорного сигнала осуществляется перевод фазового триггера 3 в состояние, в котором на его прямом выходе будет напряжение, соответствующее логической 1, а наОинверс ном выходе - логическому О, а задними фронтами импульсов входного сигнала осуществляется перевод его в противоположное состояние. При этом на его прямом выходе возникает последовательность Импульсов пр, длительность которых пропорциональна фазовому сдвигу напряжений входного и опорного сигналов, а на инверсном выходе - инвертированная последовательность этих же импульсов -ф.тр.инь- На выходе первого элемента 6 И установится логический О, а на выходе второго элемента 7 И появится последовательность импульсов Ui/i2- Задним фронтом первого из этих импульсово осуществится перевод блокирующего j1 триггера 4 в состояние логической 1 на его прямом выходе Ug -j-p, пр логического О на инверсном выходе. На выходе четвертого элемента И 9 устанавливается логический О, а на выходе третьего элемента 8 И появляется последовательность импульсов и из- поступающая с прямого выхода фазового j1 -триггера 3. Эта последовательность импульсов поступает на первый вхОд сумматора 10, напряжение на выходе которого прямо пропорпионально длительности импульсов. 4 поступающих 1на его входы,(. а полярность, зависит от того, на какой из входов по- ; даются эти импульсы. Работа дискриминатора при опережении входным сигналом опорного происходит аналогичным образом. Время задержки сигналов на элементах дискриминатора не влияет на точность и надежность работы схемы, поскольку опорный и входной сигналы поступают непосредственно на 1 - и j -входы фазового триггера 3, а последовательность импульсов с выхода фазового j k -триггера 3 через третий или четвер тый -элементы 8 и 9 И, поступают на вход сумматора 10. Причем время задержки сигнала логическим элементом 8 И или 9 И также не влияет на длительность этих импульсов, а влияет только на величину задержки поступления импульсов на вход сумматора 10. Поэтому напряжение на выходе сумматора 10 прямо пропоршгонально фазовому сдвигу между опорным и входным сигналами, а его полярность зависит от знака разности этих сигналов. Таким образом,предлагаемый фазовыйдискриминатор имеет более высокую точность и надежность. Формула изобретения Фазовый дискриминатор, содержащий четыре элемента И, инвертор, сумматор и блокирующий j 1с -триггер, j -вход которого соединен с выходом первого элемента И, а 1 -вход - с выходом второго элемента И, а выходы соединены с первы- ми входамитретьего и четвертого элементов И соответственно, выходы которых подключены к входам сумматора, выход которого является выходом устройства, а первый вход, второго элемента И через инвертор подключен к источнику опорного сигнала, отличающийся тем, что, с целью повышения точности и надежности, в него введен фазовый j1 триггер, j -вход которого соединен с источником входного сигнала, а k -вход - с источником опорного сигнала и первым входом первого элемента И, при этом прямой выход фазового j1 -тржтера соединен с вторыми входами первого и третьего элементов И, а его инверсный выход - с вторыми входами второго и четвертого элементов И. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР 720680, кл. Н 03 Э 3/04, 1980 (прототип).

Фиг.2

Авторы

Даты

1982-10-30—Публикация

1981-04-07—Подача