(54) УСТРОЙСТВО ДЛЯ МНОГОКАНАЛЬНОЙ ПЕРЕДАЧИ СИГНАЛОВ С КОРРЕКЦИЕЙ ОШИБОК

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тактовой синхронизации | 1985 |

|

SU1332552A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство контроля ошибок многоканальной аппаратуры магнитной записи | 1987 |

|

SU1529285A1 |

| Устройство для управления шаговым двигателем | 1977 |

|

SU663058A1 |

| Способ магнитной записи асинхронных потоков цифровой информации и устройство для его осуществления | 1990 |

|

SU1788520A1 |

| Многоканальная система для морских сейсмических исследований | 1981 |

|

SU949587A2 |

| Многоканальное устройство приема сложных сигналов | 1989 |

|

SU1786664A1 |

| Преобразователь частоты следования импульсов | 1986 |

|

SU1394394A1 |

| Устройство для контроля многоканального аппарата магнитной записи | 1986 |

|

SU1420615A1 |

| Цифровой умножитель частоты | 1978 |

|

SU803100A1 |

1

Изобретение относится к телеметрии и может быть использовано для. многоканальной передачи измерений контролируемых процессов в цифровой форме.

Известно устройство для многоканальной передачи сигналов с коррекцией ошибок, содержащее генератор импульсов и последовательно соединенные входной регистр, матрицу, блок ключей, на сигнальные входы которых поданы сигналы сообщений, пре- образователь а налог-код, инвертор и формйроват-ёль выходного сигнала, второй управляющий вход которого, соединен с выходом генератора импульсов 1.

Однако в- таком устройстве ощибки от перегрузки многоканального тракта передачи велики.

Цель изобретения - уменьшение ощибок от перегрузки многоканального тракта передачи.

Цель достигается тем, что в устройство для многоканальной передачи сигналов с коррекцией ошибок, содержащее генератор импульсов и последовательно соединенные входной регистр, матрицу, блок ключей, на сигнальные входы которого поданы сигналы

сообщений, преобразователь аналог-код, инвертор и формирователь выходного сигнала, второй управляющий вход которого соединен с выходом генератора импульсов, введены первый и второй делители частоты, блок памяти, элемент И, элемент ИЛИ и элементы несовпадения по числу сигнальных выходов преобразователя аналог-код, при этом выход генератора импульсов через первый делитель частоты подключен ко входу в ходного регистра, первому управляю.щему

входу блока памяти, третьему управляющему входу формирователя выходного сигнала, второй управляющий вход которого соединен со вторым управляющим входом блока памяти, и входу второго делителя частоты, выход которого подключен к объединенным первым входам элементов И и ИЛИ, объединенные вторые входы которых соединены с соответствующим выходом матрицы, а в з1ходы элементов И и ИЛИ .подключены соответственно ко второму входу инвертора

и четвертому управляющему входу формирователя выходного сигнала, каждый сигнальный вход которого соединен с выходом соответствующего элемента несовпадения и соответствующим сигнальным входом блока памяти, выходы которого подключены к первым входам соответствующих элементов несовпадения, вторые входы которых соединены с соответствующими сигнальными выходами преобразователя аналог-код, при этом элемент несовпадения содержит первый и второй элементы И, выходы которых подключены соответственно к первому и второму входам элемента ИЛИ, выход которого является выходом элемента несовпадения, первым входом которого являются объединенные прямой вход первого элемента И и инверсный вход второго элемента И, прямой вход которого объединен с инверсным входом первого элемента И и яв-ч ляется вторым входом элемента несовпадения.-

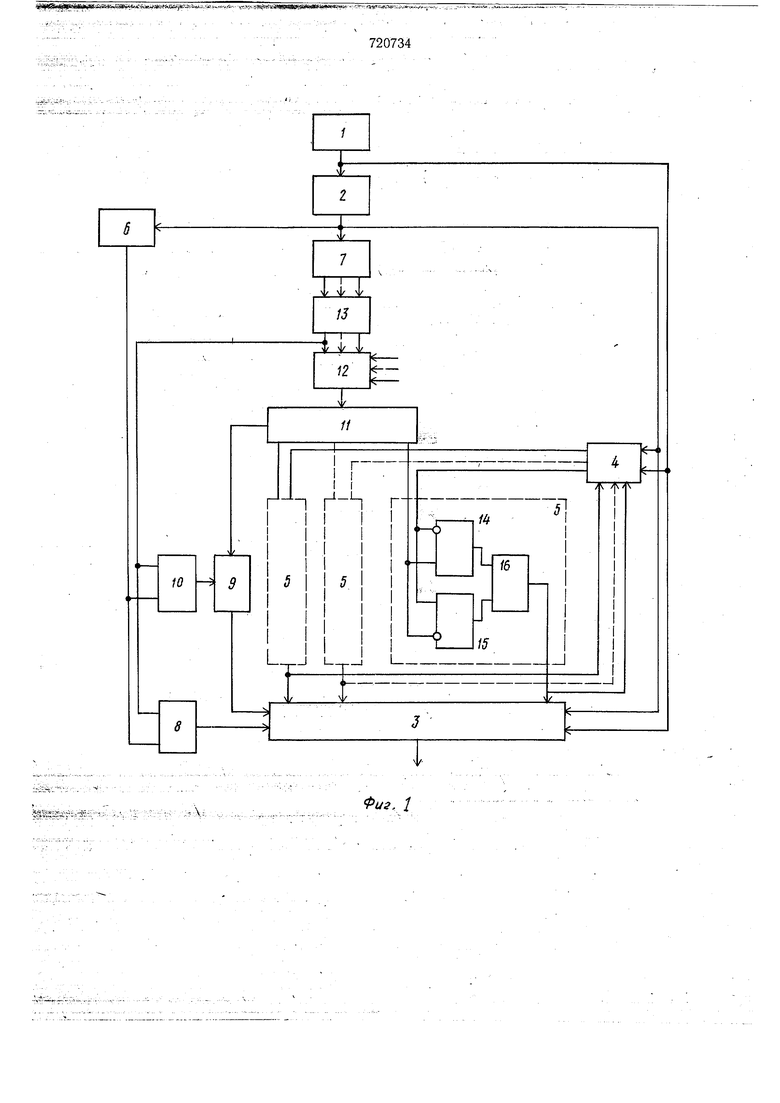

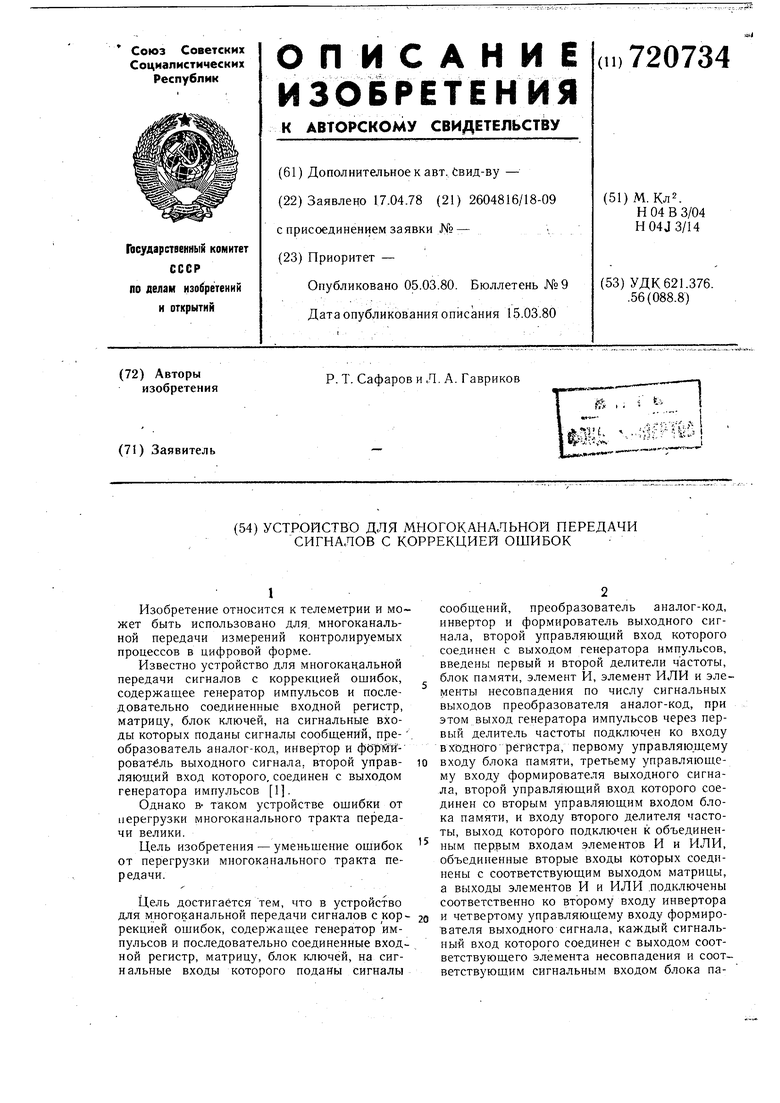

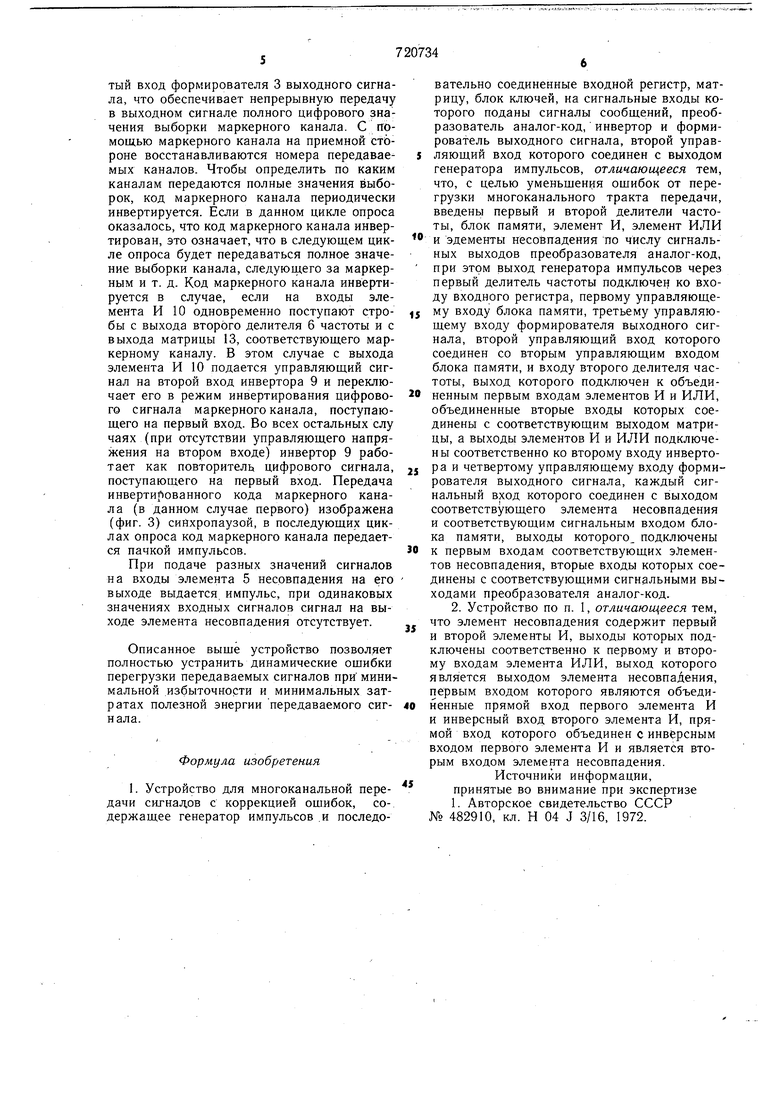

На фиг. 1 представлена структурная электрическая схема описываемого устройства; на фиг. 2 -диаграммы, поясняющие его работу; на фиг. 3 - структура кадра.

Данное устройство для многоканальной передачи сигналов с коррекцией ошибок содержит генератор 1 импульсов, первый делитель 2 частоты, формирователь 3 выходного сигнала, блок 4 памяти, элементы 5 несовпадения, второй делитель 6 частоты, входной регистр 7, элемент ИЛИ 8, инвертор 9, элемент И 10, преобразователь 11 аналог-код, блок 12 ключей, матрицу 13, при этом каждый элемент 5 несовпадения содержит первый и второй элементы И 14 и 15 и элемент ИЛИ 16.

Работа устройства иллюстрируется диаграммами (фиг. 2)- Генератор 1 импульсов генерирует последовательность синхроимпульсов (фиг. 2,а), которые подаются на вход первого делителя 2 частоты и на вторые управляющие входы формирователя 3 выходного сигнала и блока 4 памяти и служат для синхронизации работы этих блоков тактовой частотой. Первый делитель частоты осуществляет деление частоты следования импульсов от генератора 1 импульсов на число п, равное Значности цифровых кодовых сигналов, которыми представляются выборки измеряемых параметров (фиг. 2,6). Сформированная последовательность импульсов подается соответственно на третий и первый входы формирователя 3 выходного сигнала и блока 4 памяти, а также на входы второго делителя 6 частоты и входного регистра 7 и служит для синхронизации указанных блоков частотой опроса каналов. Входной регистр 7 и матрица 13 формируют на выходе матрицы 13 стробирующие импульсы, которыми поочередно отпираются ключевые схемы блока 12 ключей, на вторые входы которых подаются сигналы от источников сообщений. Сигналы, поочередно проходя через блок 12 ключей, преобразуются в цифровую двоичню форму и преобразователе 11 аналог-код (фиг. 2, в) и затем в параллельном коде подаются на вторые входы элементов 5

несовпадения, где значение каждого разряда сравнивается со значением каждого разряда предыдущей (предсказанной выборки, записанной в блоке 4 памяти (фиг. 2г). На выходы элементов 5 несовпадения выдается единичная посылка (импульс), если сравниваемые значения одноименных разрядных сигналов не совпадают, и выдается нулевая посылка (пауза), если эти значения совпадают (фиг. 2,д). С помощью синхроимпульса с выхода первого делителя 2 частоты п-разрядные дельта-сигналы с выходов элементов 5 несовпадения считываются в формирователь 3 выходного сигнала и в блок 4 памяти. При этом в блоке 4 памяти при экстраполяции нулевого порядка цифровые разрядные сигналы заполненной предыдущей (предсказанной) выборки меняются на противоположные, если в одноименных разрядах дельта-сигналов присутствует единичная посылка (импульс), и не меняются, если разрядные сигналы равны нулю, при этом в блоке 4 памяти записывается предсказанное измеряемого параметра.

Таким образом, осуществляется формирование п-разрядных дельта сигналов.

Формирование сигналов, характеризующих полные значения выборок, осущестсвляется следующим образом.

С выхода первого делителя 2 частоты импульсы, следующие с частотой опроса каналов, подаются во второй делитель б частоты, в котором происходит деление частоты следования импульсов таким образом, чтобы на выходе выдавалась последовательность импульсов с периодом следования (кЫ -f 1)Тг, где к - целое число, N - число каналов,

t-время,соответствующее периоду опроса каналов.

Проходя через элемент ИЛИ 8 импульсы с выхода второго делителя 6 частоты подаются на четвертый вход формирователя 3 выходного сигнала, где формируется управляющий сигнал, который закрывает вход длядельта-сигналов и открывает первый

вход, через который в формирователь 3 выходного сигнала с преобразователя 11 аналогкод через инвертор 9 считывается полное значение выборки измеряемого параметра. Выбранный коэффициент деления второго делителя б частотьт поэ воляет чередовать в передаваемом сигнале каналы с полным значением передаваемых выборок. (На фиг. 3 защтрихованы каналы с полным значением передаваемых выборок, при К 1).

Для осуществления декодирования и синхронизации сигнала при приеме на один из информационных входов блока 12 ключей подается постоянное заранее известное напряжение-маркер. С выхода матрицы 13, соответствующего маркерному каналу, строб подается через элемент ИЛИ 8 на четвертый вход формирователя 3 выходного сигнала, что обеспечивает непрерывную передачу в выходном сигнале полного цифрового значения выборки маркерного канала. С помощью маркерного канала на приемной стороне восстанавливаются номера передаваемых каналов. Чтобы определить по каким каналам передаются полные значения выборок, код маркерного канала периодически инвертируется. Если в данном цикле опроса оказалось, что код маркерного канала инвертирован, это означает, что в следующем цикле опроса будет передаваться полное значение выборки канала, следующего за маркерным и т. д. Код маркерного канала инвертируется в случае, если на входы элемента И 10 одновременно поступают стробы с выхода второго делителя 6 частоты и с выхода матрицы 13, соответствующего маркерному каналу. В этом случае с выхода элемента И 10 подается управляющий сигнал на второй вход инвертора 9 и переключает его в режим инвертирования цифрового сигнала маркерного канала, поступающего на первый вход. Во всех остальных слу чаях (при отсутствии управляющего напряжения на втором входе) инвертор 9 работает как повторитель цифрового сигнала, поступающего на первый вход. Передача инвертированного кода маркерного канала (в данном случае первого) изображена (фиг. 3) сиНхропаузой, в последующих циклах опроса код маркерного канала передается пачкой импульсов. При подаче разных значений сигналов на входы элемента 5 несовпадения на его выходе выдается импульс, при одинаковых значениях входных сигналов сигнал на выходе элемента несовпадения отсутствует. Описанное выше устройство позволяет полностью устранить динамические ощибки перегрузки передаваемых сигналов при минимальной избыточности и минимальных затратах полезной энергии передаваемого сигнала. Формула изобретения 1. Устройство для многоканальной передачи сигнадов с коррекцией ощибок, содержащее генератор импульсов .и последовательно соединенные входной регистр, матрицу, блок ключей, на сигнальные входы которого поданы сигналы сообщений, преобразователь аналог-код, инвертор и формирователь выходного сигнала, второй управляющий вход которого соединен с выходом генератора импульсов, отличающееся тем, что, с целью уменьщения ощибок от перегрузки многоканального тракта передачи, введены первый и второй делители частоты, блок памяти, элемент И, элемент ИЛИ и эдементы несовпадения по числу сигнальных выходов преобразователя аналог-код, при этом выход генератора импульсов через первый делитель частоты подключен ко входу входного регистра, первому управляющему входу блока памяти, третьему управляющему входу формирователя выходного сигнала, второй управляющий вход которого соединен со вторым управляющим входом блока памяти, и входу второго делителя частоты, выход которого подключен к объединенным первым входам элементов И и ИЛИ, объединенные вторые входы которых соединены с соответствующим выходом матрицы, а выходы элементов И и ИЛИ подключены соответственно ко второму входу инверторай четвертому управляющему входу формирователя выходного сигнала, каждый сигнальный вход которого соединен с выходом соответствующего элемента несовпадения и соответствующим сигнальным входом блока памяти, выходы которого, подключены к первым входам соответствующих элементов несовпадения, вторые входы которых соединены с соответствующими сигнальными выходами преобразователя аналог-код. 2. Устройство по п. 1, отличающееся тем, что элемент несовпадения содержит первый и второй элементы И, выходы которых подключены соответственно к первому и второму входам элемента ИЛИ, выход которого является выходом элемента несовпадения, первым входом которого являются объединенные прямой вход первого элемента И и инверсный вход второго элемента И, прямой вход которого объединен с инверсным входом первого элемента И и является вторым входом элемента несовпадения. Источники информации. принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 482910, кл. Н 04 J 3/16, 1972.

720734

Физ, i

Фиг. 2 Ч у/т NK 1к 2к Зк NK 1к 2к 3/ Фиг.д н-н МММ л/к 1к 2к Зк «

Авторы

Даты

1980-03-05—Публикация

1978-04-17—Подача