(54) ЦИФРОВОЙ УМНОЖИТЕЛЬ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты следования импульсов (его варианты) | 1983 |

|

SU1120483A1 |

| ЦИФРОВОЙ СЛЕДЯЩИЙ УМНОЖИТЕЛЬ ЧАСТОТЫ | 1991 |

|

RU2042977C1 |

| Цифровой умножитель частоты | 1984 |

|

SU1192106A1 |

| Формирователь случайных сигналов | 1990 |

|

SU1732419A1 |

| Цифровой умножитель частоты | 1980 |

|

SU930575A2 |

| Умножитель частоты следования импульсов | 1981 |

|

SU993451A1 |

| Цифровой умножитель частоты | 1983 |

|

SU1164857A1 |

| Цифровой умножитель частоты | 1980 |

|

SU928353A1 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1990 |

|

SU1795475A1 |

| Дискретный умножитель частоты | 1977 |

|

SU736099A1 |

1

Изобретение относится к электрорадиоизмерениям и может быть использовано в информационно-измерительных системах различного назначения.

Известен цифровой умножитель частоты, содержащий последовательно соединенные генератор опорной частоты, делитель частоты с постоянным коэффициентом деления, счетчик, регистр памяти, блок переноса кода, управляемый делитель частоты, блок коррекции и ключ, сигнальный вход которого подключен к выходу генератора опорной частоты, а также элемент ИЛИ, один из входов которого подключен к выходу управляемого делителя частоты, и последовательно соединенные формирователь импульсов, вход которого является входом цифрового умножителя частоты, и блок управления, первый выход которого подключен к управляющему входу блока коррекции, а второй выход - к управляющему входу делителя частоты с постоянным коэффициен.том деления 1.

Однако известный цифровой умножитель частоты имеет ограниченное значение коэффициента умножения и недостаточную точность.

Цель изобретения - увеличение коэффициента умножения и повыщение его точности.

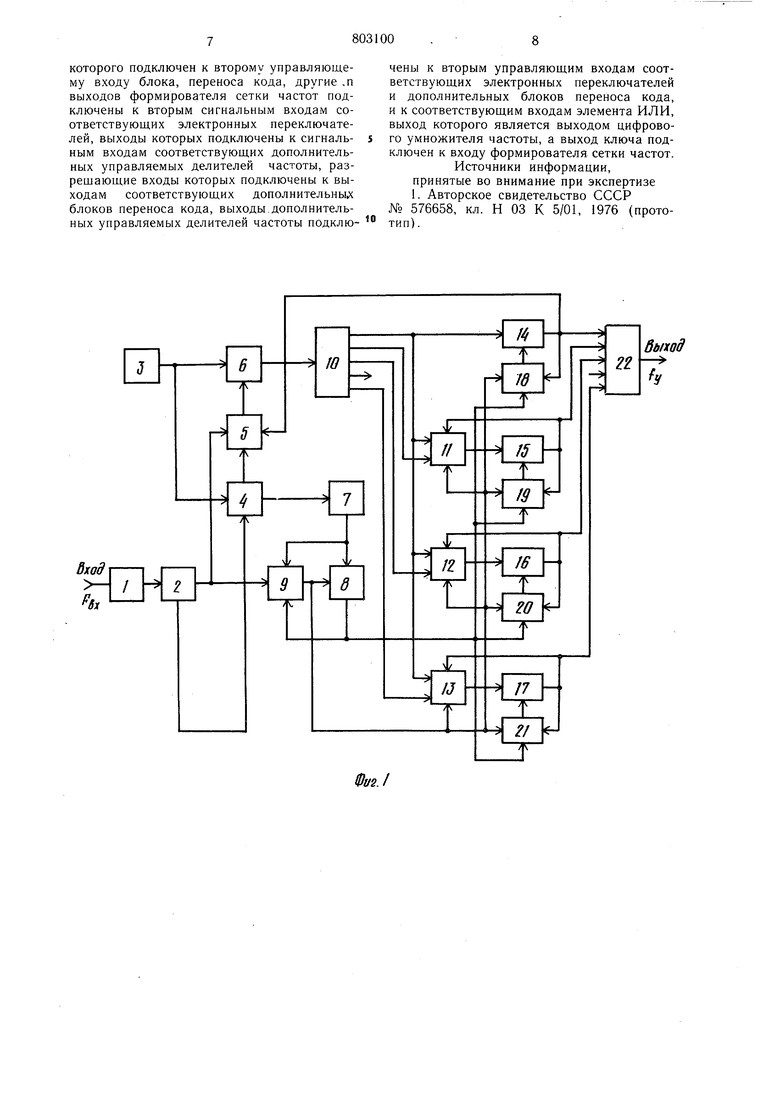

Для этого в цифровой умножитель частоты, содержащий последовательно соединен- ные генератор опорной частоты, делитель частоты с постоянным коэффициентом деления, счетчик, регистр памяти, блок переноса кода, управляемый делитель частоты, блок коррекции и ключ, сигнальный вход которого подключен к выходу генератора опорной частоты, а также элемент ИЛИ, один из входов которого подключен к выходу управляемого делителя частоты, и последовательно соединенные формирователь импульсов, вход которого является входом цифрового умножителя частоты, и блок управления, первый выход которого подключен к управляющему входу блока коррекции, а второй выход - к управляющему входу делителя частоты с постоянным коэффициентом деления, введены формирователь сетки

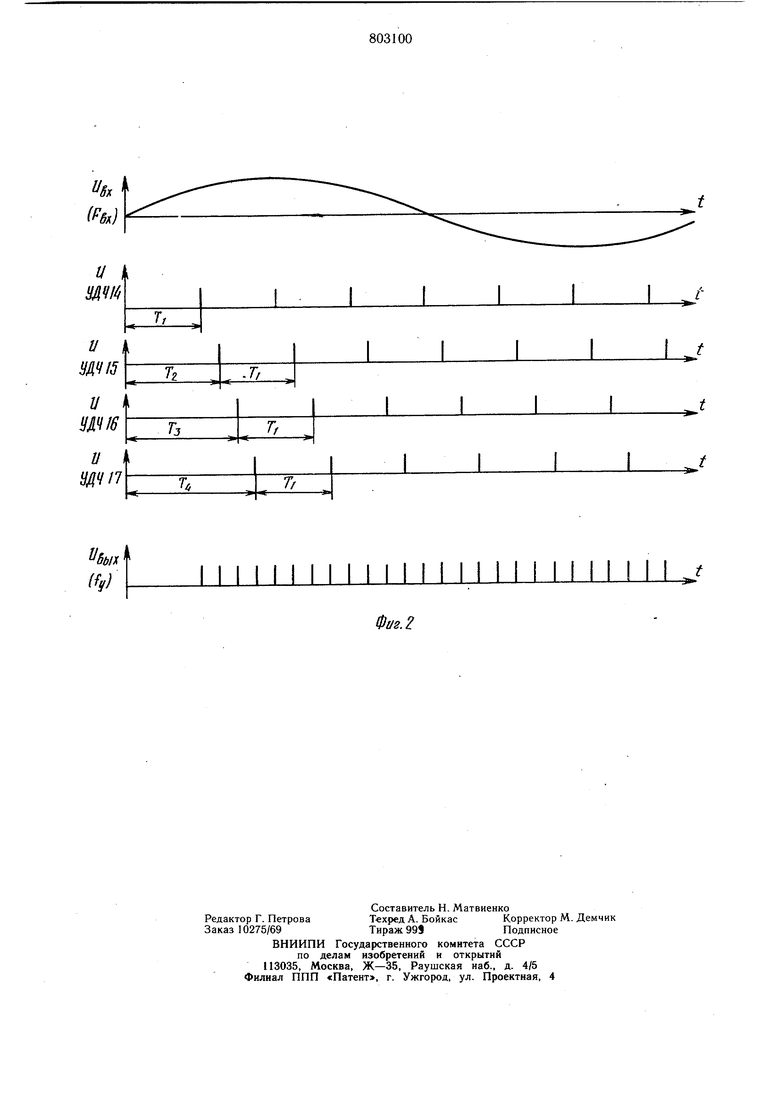

частот, п электронных переключателей, п дополнительных управляемых делителей частоты, п дополнительных блоков переноса кода и компаратор кодов, управляющий вход которого подключен к первому выходу блока управления, первый сигнальный вход - к выходу счетчика, второй сигнальный вход - к выходу регистра памяти и к разреидающим входам всех блоков переноса кода, а выход - к разрешающему входу регистра памяти, к первым управляющим входам электронных переключателей и всех блоков переноса кода, при этом первый выход формирователя сетки частот подключен к первым сигнальным входам электронных переключателей и к сигнальному входу управляемого делителя частоты, выход которого подключен к второму управляющему входу блока переноса кода, другие п выходов формирователя сетки частот подключены к вторым сигнальным входам соответствующих электронных переключателей, выходы которых подключены к сигнальным входам соответствующих дополнительных управляемых делителей частоты, разрешающие входы которых подключены к выходам соответствуюпд,их дополнительных блоков переноса кода, выходы дополнительных управляемых делителей частоты подключены к вторым управляющим входам соответствующих электронных переключателей и дополнительных блоков переноса кода, и к соответствующим входам элемента ИЛИ, выход которого является выходом цифрового умножителя частоты, а выход ключа подключен к входу формирователя сетки частот. На фиг. 1 представлена структурная электрическая схема цифрового умножителя частоты; на фиг. 2 - временные диаграм.мы его работы. Цифровой умножитель частоты содержит формирователь 1 импульсов, блок 2 управления, генератор 3 опорной частоты, делитель 4 частоты с постоянным коэффициентом деления, блок 5 коррекции, ключ 6, счетчик 7, регистр 8 памяти, компаратор 9 кодов, формирователь 10 сетки частот, электронные переключатели 11 -13, управляемые делители 14-17 частоты ,(с переменным коэффициентом деления), блоки 18- 21 переноса кода, элемент ИЛИ 22. Устройство работает следующим образом. При подаче на вход устройства сигнала умножаемой частоты блок 2 по началу периода сигнала разрешает прохождение импульсов генератора 3 частотой fo через делитель 4. В делителе 4 установлен коэффициент деления -, где к - требуемый коэффициент умножения частоты . Импульсы с выхода делителя 4 поступают с частотой п - на вход счетчика 7. По окончании первого периода сигнала LJftx импульс блока 2 переносит остаток кода ДЫ из делителя 4 в блок 5 и разрешает сравнение компаратором 9 кодов счетчика 7 и регистра 8. в счетчике 7 В конце периода Tjx зафиксировано число q, равное целой части выражения . За это время на вход делителя 4 поступило число импульсов частоты . N foTfrx В блоке 5 зафиксировано число AN, равное остатку от деления числа N на частное -5 дМ-//-. Так как в начальный момент работы устройства коды счетчика 7 и регистра 8 не совпадают, то на выходе компаратора 9 появляется импульс несовпадения кодов, разрешающий перенос кода счетчика 7 в регистр 8 и кода регистра 8 одновременно во все управляемые делители частоты (УДЧ) 14-17 посредством блоков 18-21 переноса. Выходной импульс компаратора 9 поступает также на переключатели 11 -13, которые переключают входы дополнительных УДЧ 15-17 с основного (первого) выхода формирователя 10 сетки частот на дополнительные выходы, таким образом, что вход i-ro управляемого делителя частоты подключается к i-му выходу формирователя 10, а i -f 1 вход - к i -f 1 выходу формирователя 10. Последний обеспечивает следующие значения выходных час™ У,- . гр« -Для случая п 4 (фиг. 1) значения выходных частот формирователя 10 сетки частот равны , ././oJ/ai- o /s-f e.: Л ТЛФормирователь 10 легко может быть реализован, например на основе делителя с дробным коэффициентом деления с изъятием отдельных импульсов из выходной импульсной последовательности. При этом импульсы на выходах УДЧ 14-17 появляются через различные интервалы времени от момента одновременного переноса кода регистра 8 в УДЧ 14-17. Действительно, интервал времени Тг. .-Taf .; . T,,4,75T. при изменении входной частоты Fjy устройства соответственно меняется код q, но выходные импульсы УДЧ 15-17 всегда равномерно расставлены в интервале (периоде) Tj. Выходной сигнал устройства представляет собой периодическую равномерную последовательность импульсов с периодом повторения ig ji n Tr%fe-.. fПервый же выходной импульс каждого дополнительного УДЧ 15-17 возвращает электронный переключатель И -13, расположенный на его входе, в исходное состояние, т. е. такое состояние, при котором вход дополнительного УДЧ 15-17 подключается к основному (первому) выходу формирователя 10. Электронный переключатель остается в таком состоянии до момента изменения кода в регистре 8. Начиная с второго периода входного сигнала, число q в дополняющем коде вводится через блоки 18-21 переноса раздельно в каждый из УДЧ 14-17 по их выходным импульсам. Число q равно целой части частного -. Для исключения погрешности умножения частоты входного сигнала из-за некратности чисел N и - в блоке 5, содержащего, например блок переноса кода делителя 4, счетчик, элементы И и одновибратор, осуществляется коррекция периода повторения выходных импульсов устройства. Если перенос из делителя 4 в счетчик блока 5 код AN О, то каждый выходной импульс УДЧ 14 запускает одновибратор, который выдает единичный импульс, закрывающий ключ 6 на время t 4. Из последовательности импульсов генератора 3 вычитается один импульс, что приводит к появлению следующего выходного импульса устройства позже на время Tj, кроме того, из кода счетчика блока 5 до установки его в нулевое значение по каждому импульсу одновибратора вычитается один импульс. В итоге сумма периодов ty, умноженной частоты равна периоду Т|д. к , .п , tyt ieX, Т. е. интегральное (среднее) за период Tg значение коэффициента умножения является точным. Однако, вследствие погрешности дискретности преобразования периода Tfx в число импульсов длительности единичных интервалов t,, выходной последовательноети устройства формируются с погрешностью, что суш,ественно ухудшает точность устройств, например фазоизмерительных, использующих цифровой умножитель частоты в качестве формирователя квантующей последовательности импульсов или в качестве входных умножителей Частоты в случае измерения мгновенных значений разности фаз сигналов. В заявленном устройстве эта погрешность уменьшена в п раз. Действительно, так как шаг дискретности преобразоваНИН в устройстве-прототипе равен kto, длительность первого интервала ty, а также периодов iyj, iyjti..., формирующихся после обнуления счетчика в блоке коррекции, равна tjq (точное значение периода умноженной частоты tyu tp (q Ч- , при этом погрешность формирования интервала tut At,., . В заявленном устройстве шаг дискретности преобразования равен , так как коэффициент деления делителя 4 в п раз меньще требуемого коэффициента умножения. Легко показать, что при этом погрешность формирования интервала Тйким образом, вследствие повышения з;и чо1П1Я выходной частоты делителя 4 от Ij до п-| при равных значениях и умножаемых частот точность заявленного устройства 3 i раз пыпге по сравкенню с устройством, выбранным в качестве прототипа. При задииных погрешности умножения 6 t ,.j-Hp(piin:itiife .-rliOH-jeKM); k верхняя граничили час1-..иа диапазона Заяв.-|яелк)го устройстгаа в п раз зы;;.:е по сравнению с прототипом. При рав;а-;х значениях частот и равной погрешности умножения (в случае есля К.)5ффициент де.пе)ия делителя А в зая15Л);сл10м vCTpoiiC; ,е paseii k) киэффициенг ;;Множенн: з,1:;;).1яемого уст.юйства в п раз выше ю сравнению с прототипом. Естественно, что по сравнению с известным устройством, одновременно могут быть новышены и T04iiOv ib j,:,аожения в м | раз и верхняя граничная частота устройства в П2 рзз и коэффициент умножения в п раз, но при этом n(-rij/n;| П. Форм;:.-:й изобр1 тен1,я Цифровой ум1-10житель частоты, содержащий последовательно соединенные генератор опорной част-оты, делитель частоты с постоянным коэффициентом делении, счетчик; .регистр памяти, блок переноса кода, управляемый делитель частоты, блок коррекции и ключ, сигнальный вход которО о подключен к выходу генератора опорной частоты, а также с лсмент ИЛИ, один из входов которого подключен к выходу управляемого делителя частоты, и последовательно соединенные формирователь импульсов, вход которого является входом цифрового умножителя частоты, и блок управления, первый вых-од которого подключен к управляющему входу блока коррекции, а второй выход - к управляющему входу делителя частоты с постоянным коэффициентом деления, отличающийся тем, что, с целью увеличения коэффициента умножения и повышения его точности, введены формирователь сетки частот, п электронных переключателей, п дополнительных управляемых делителей частоты, п дополнительных блоков переноса кода и компаратор кодов, управляющий вход которого подключен к первому выходу блока управления, первый сигнальный вход - к выходу счетчика, второй сигнальный вход - к выходу регистра памяти и к разрещающим входам всех блоков переноса кода, а выход - к разрещающему входу регистра памяти, к первым управляющим входам электронных переключателей и всех блоков переноса кода, при этом первый выход формирователя сетки частот подключен к первым сигнальным входам электронных переключателей и к сигнальному входу управляемого делителя частоты, выход

которого подключен к второму управляющему входу блока, переноса кода, другие ,п выходов формирователя сетки частот подключены к вторым сигнальным входам соответствующих электронных переключателей, выходы которых подключены к сигнальным входам соответствующих дополнительных управляемых делителей частоты, разрешающие входы которых подключены к выходам соответствующих дополнительные блоков переноса кода, выходы.дополнительных управляемых делителей частоты подклюВход

%

чены к вторым управляющим входам соответствующих электронных переключателей и дополнительных блоков переноса кода, и к соответствующим входам элемента ИЛИ, выход которого является выходом цифрового умножителя частоты, а выход ключа подключен к входу формирователя сетки частот.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 576658, кл. Н 03 К 5/01, 1976 (прототип). I I I I I I I I и I I I I I I I I I I I I I и I .

Авторы

Даты

1981-02-07—Публикация

1978-09-26—Подача