Изобретение относится к системам регулирования, а именно к цифровым системам, и может быть использовано для измерения и регулирований одного или соотношения двух параметров технологического процесса. Известны цифровые регуляторы технологических параметров, содержащие датчик регулируемого параметра, счёт чик, регистр памяти с ключами, вьдход ной преобразователь код-аналог и блок задания 1. Недостатком таких регуляторов является дополнительное преобразование разности между заданным и текущим значениями регулируемого параметра перед поступлением ее в выходной преобразователь ..код-аналог, всле ствие того что эта разность постпает ца регистр памяти в кодах. Наиболее близким к предлагаемому является цифровой регулятор, содержа щий датчик и задатчик, выходы которы соединены со входами первого счетчика, соединенного с соответствующими входами блока ключей,выходы которого соединены со входами первого блока памяти, подключенного к первым входам преобразователя- код-аналог 2. Недостатком такого регулятора является использование двоично-десятичного реверсивного счетчика для вьшолнения Ьперации вычитания действительного значения регулируемого параметра из заданного, что приводит к дополнительным преобразованиям, а, следовательно, к усложнению схемы регулятора. Кроме того, в работе реверсивного счетчика в процессе счета наблюдаются сбои, происхо-дящие в момент смены знака.разности. Все это снижает надежность работы регулятора. Цель изобретения - повышение надежности работы цифрового регулятора. Указанная цель достигается тем, что в цифровом регуляторе установлены второй счетчик и последовательно соединенные индикатор нуля и второй блок памяти, первый выход которого соединен с соответствуквдими входами блока ключей и со вторым входом преобразователя . код-аналог, а второй выход - с соответствующими входами блока ключей и второго счетчика, другой вход которого соединен с выходом датчика, а выходы соединены с соответствующими входами блока ключей, входы индикатора нуля соединены с соответствующими .в,ыходами первого счетчика, представляющего собой нереверсивный двоичный счетчик

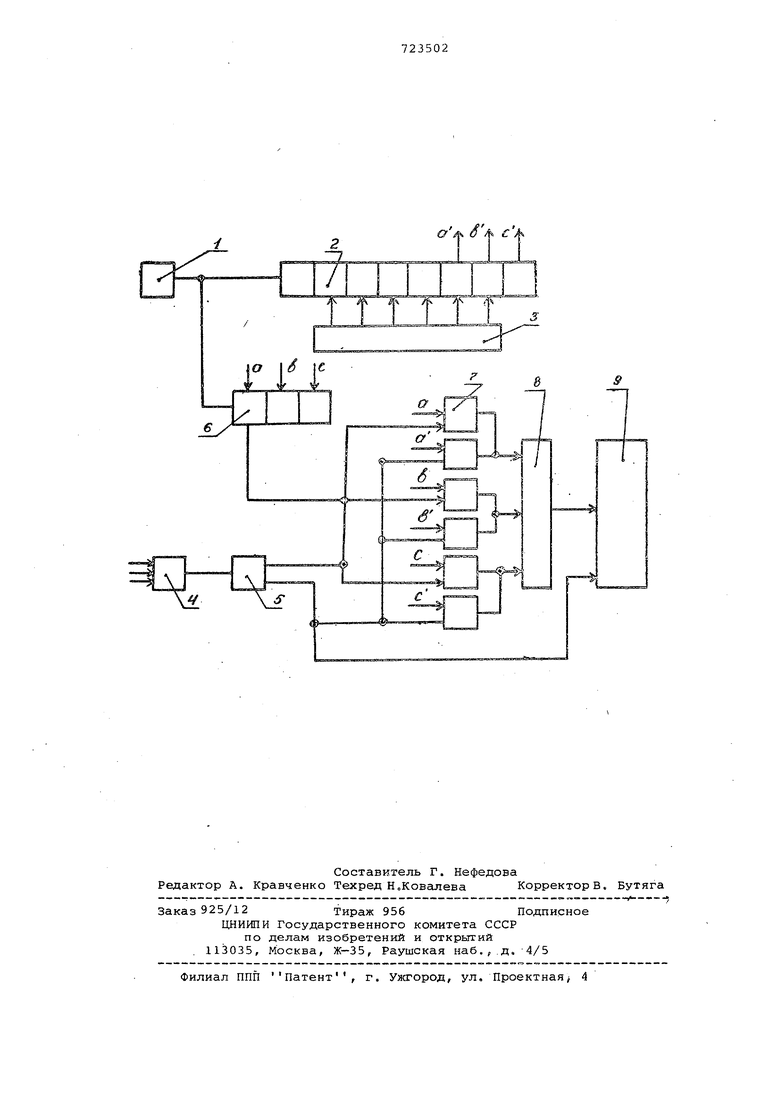

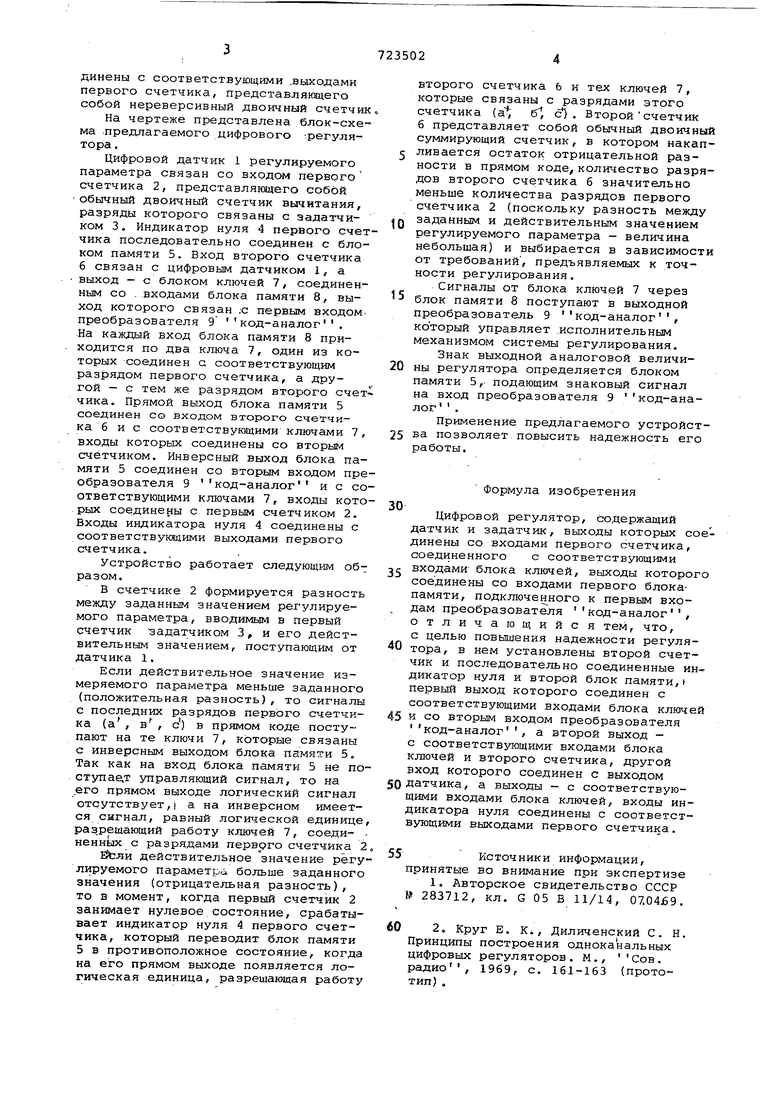

На чертеже представлена блок-схема предлагаемого цифрового регулятора.

Цифровой датчик 1 регулируемого параметра связан со входом первого счетчика 2, представлякяцего собой обычный двоичный счетчик вычитания, разряды которого связаны с задатчиком 3. Индикатор нуля 4 первого счетчика последовательно соединен с блоком памяти 5. Вход второго счетчика б связан с цифровым датчиком 1, а выход - с блоком ключей 7, соединенным со . входами блока памяти 8, выход которого связан ,с первым входом преобразователя 9 код-аналог. На каждый вход блока памяти 8 приходится по два ключа 7, один из которых соединен с соответствующим разрядом первого счетчика, а другой - с тем же разрядом второго счетчика. Прямой выход блока памяти 5 соединен со входом второго счетчика бис соответствующими ключами 7, входы которых соединены со вторым счетчиком. Инверсный выход блока памяти 5 соединен со вторым входом преобразователя 9 код-аналог и с соответствующими ключами 7, входы которых соединены с первым счетчиком 2. Входы индикатора нуля 4 соединены с соответствукнцими выходами первого счетчика.

Устройство работает следующим образом.

В счетчике 2 формируется разность между заданным значением регулируемого параметра, вводимым в первый счетчик эадатчиком 3, и его действительным значением, поступающим от датчика 1.

Если действительное значение измеряемого параметра меньше заданного (положительная разность), то сигналы с последних разрядов первого счетчика (а , в , с ) в прямом коде поступают на те ключи 7, которые связаны с инверсным выходом блока памяти 5. Так как на вход блока памяти 5 не поступае,т управляющий сигнал, то на .его прямом выходе логический сигнал отсутствует, а на инверсном имеется сигнал, равный логической единице раз.рещающий работу ключей 7, соединенн лх с разрядами первого счетчик а Е#сли действительное значение регулируемого параметра больше заданного значения (отрицательная разность), то в момент, когда первый счетчик 2 занимает нулевое состояние, срабатывает индикатор нуля 4 первого счетчика, который переводит блок памяти 5 в противоположное состояние, когда на его прямом выходе появляется логическая единица, разрешающая работу

второго счетчика 6 и тех ключей 7, которые связаны с разрядами этого счетчика (а б, с). Второйсчетчик б представляет собой обычный двоичный суммирующий счетчик, в котором накапливается остаток отрицательной разности в прямом коде, количество разрядов второго счетчика б значительно меньше количества разрядов первого счетчика 2 (поскольку разность между

Q заданным и действительным значением регулируемого параметра - величина небольшая) и выбирается в зависимости от требований , предъявляемых к точности регулирования.

Сигналы от блока ключей 7 через

5 блок памяти 8 поступают в выходной преобразователь 9 код-аналог, который управляет .исполнительным механизмом системы регулирования. Знак выходной аналоговой величины регулятора определяется блоком памяти 5,- подающим знаковый сигнал на вход преобразователя 9 код-аналог .

Применение предлагаемого устройства позволяет повысить надежность его работы.

Формула изобретения

30

Цифровой регулятор, содержащий датчик и задатчик, выходы которых содинены со входами Первого счетчика, соединенного с соответствующими

j входами блока ключей, выходы которог соединены со входами первого блока памяти, подключен1 ного к первым входам преобразователя код-аналог, отличающийся тем, что, с целью повышения надежности регулятора, в нем установлены второй счетчик и последовательно соединенные ин дикатор нуля и второй блок памяти, первый выход которого соединен с соответствующими входами блока ключе

45 и со вторым входом преобразователя код-аналог, а второй выход с соответствующими- входами блока ключей и второго счетчика, другой вход которого соединен с выходом

50 датчика, а выходы - с соответствующими входами блока ключей, входы индикатора нуля соединены с соответствующими выходами первого счетчика.

55 Источники информации,

принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 283712, кл. G 05 В 11/14, 07..

60 2. Круг Е. Ki, Диличенский С. Н. Принципы построения одноканальных цифровых регуляторов. М., Сов. радио , 1969, с. 161-163 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой регулятор | 1978 |

|

SU702343A1 |

| Регулятор постоянного тока для измерения тока срабатывания защиты стабилизаторов напряжения | 1982 |

|

SU1051522A1 |

| Устройство для регулирования температуры | 1988 |

|

SU1532907A1 |

| Цифровой регулятор | 1981 |

|

SU1004967A1 |

| Дискретный регулятор уровня | 1984 |

|

SU1262461A1 |

| Цифровой следящий электропривод | 1985 |

|

SU1308982A1 |

| ОПЕРАТИВНЫЙ КОНТРОЛЛЕР СУММАРНОЙ МОЩНОСТИ НАГРУЗКИ ГРУППЫ ЭНЕРГОПОТРЕБИТЕЛЕЙ | 1998 |

|

RU2145717C1 |

| УСТРОЙСТВО для АВТОМАТИЧЕСКОГО РЕГУЛИРОВАНИЯ | 1972 |

|

SU342171A1 |

| Цифровой регулятор | 1985 |

|

SU1293695A1 |

| Электропривод стенда для испытания механических передач | 1985 |

|

SU1429267A1 |

Авторы

Даты

1980-03-25—Публикация

1975-12-30—Подача