Изобретение относится к статическим системам автоматического регулирования и может быть использовано для регулирования одного параметра или соотношения двух параметров технологического процесса.

Цель изобретения является упрощение и повышение точности цифрового регулятора.

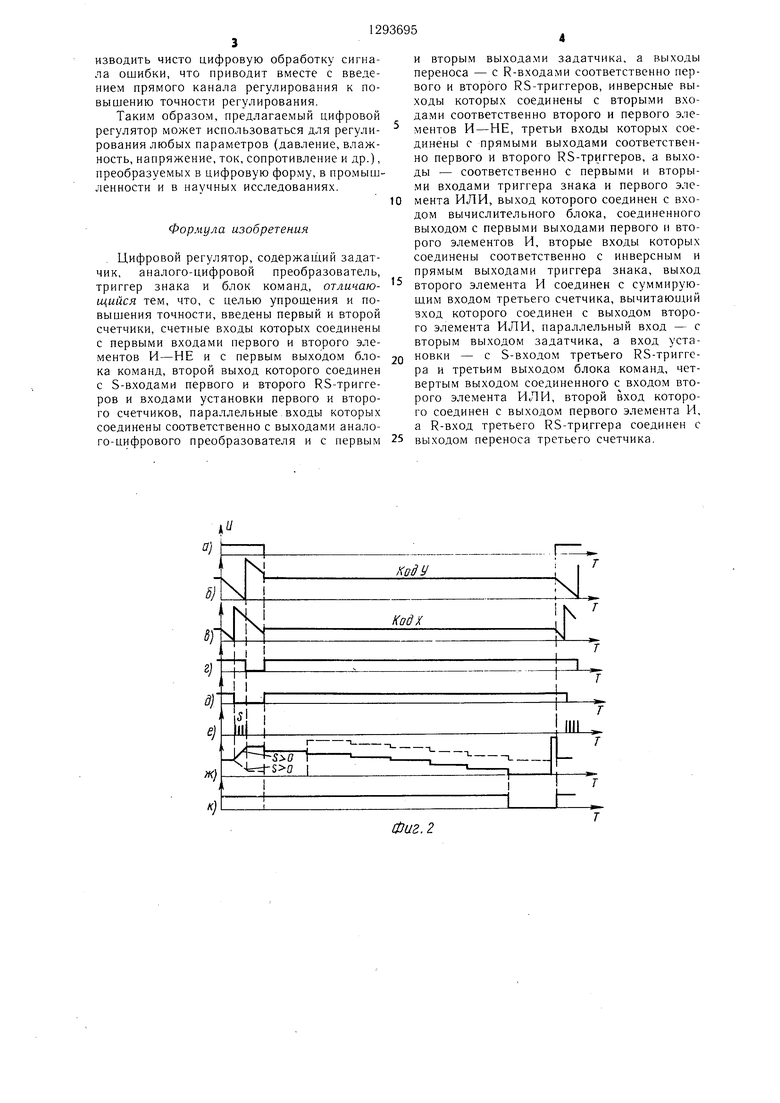

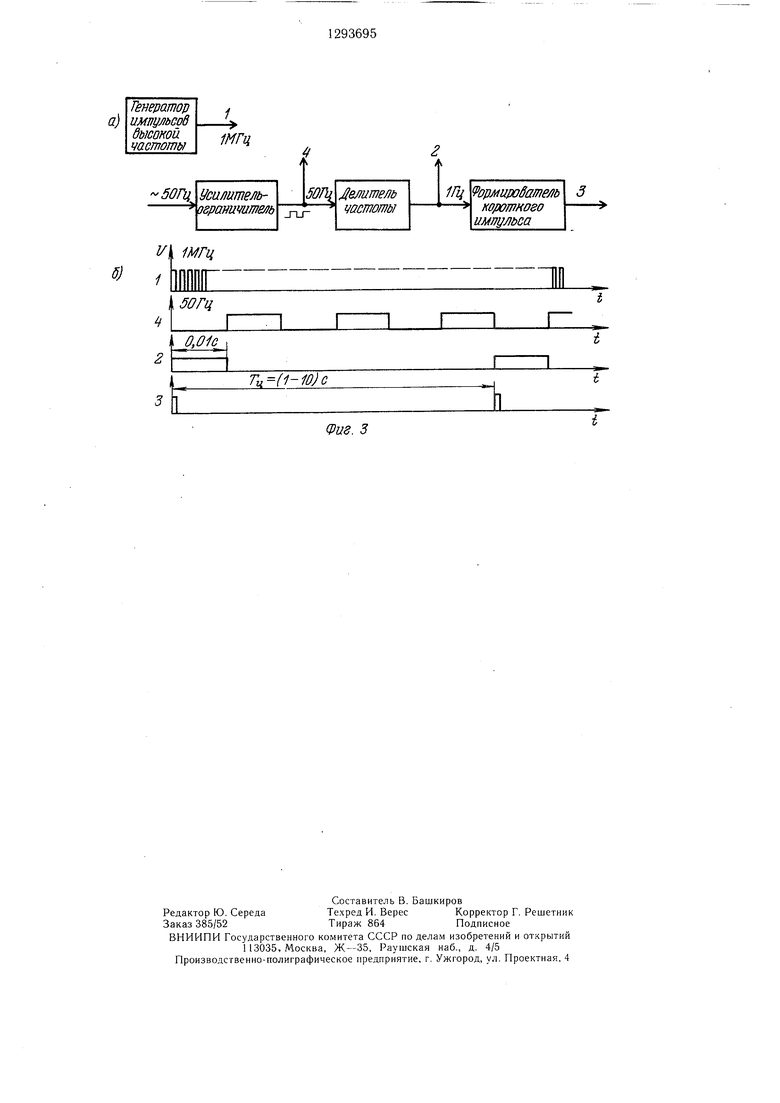

На фиг. 1 представлена функциональная схема предлагаемого регулятора; на фиг. 2 - временные диаграммы работы цифрового регулятора; на фиг. 3 - пример реализации и временные диаграммы работы блока команд.

Устройство содержит блок 1 команд, первый 2 и второй 3 счетчики, первый 4 и второй 5 элементы И-НЕ, первый 6 и второй 7 RS-триггеры, третий счетчик 8, тре- тий RS-триггер 9, первый элемент ИЛИ 10, аналого-цифровой преобразователь 11, задат- чик 12, второй элемент ИЛИ 13, триггер 14 знака, цифровой вычислительный блок 15, первый 16 и второй 17 элементы И.

Цифровой регулятор работает в системе регулирования с обратной связью по принципу комбинированного регулирования, т.е. осуществляет управление по рассогласованию и по заданию.

Цифровой регулятор работает следую- 25 заданию (участок цепи между вторым выхо35

40

щим образом.

Измеренное значение (X) регулируемой величины преобразуется с помощью аналого-цифрового преобразователя 11 в двоично-десятичный код. Заданное значение (Z) регулируемой величины формируется на выхо- 30 л1ах задатчика 12 также в двоично-десятичном коде.

На выходе блока 1 команд формируются импульсы цикла (фиг. 2а и 36), в интервалах между которыми на выходе цифрового регулятора действует широтно-импульсный сигнал регулируюшего воздействия (Y), а в течение самих импульсов цикла происходит формирование сигнала рассогласования S (ошибка S} между заданием и действительным значением регулируемой величины X.

Сигнал ошибки S образуется как сигнал разности S Z - X в соответствии с временными диаграммами, приведенными на фиг. 2, следуюшим образом.

По заднему фронту импульсов цикла в 45 первый счетчик 2 с выхода аналого-цифрового преобразователя 11 записывается в коде 8421 значение X, во второй счетчик 2 с выходов задатчика 12 в коде 8421 - значение Z (фиг. 2 б и в), RS-триггеры 6 и 7 устанавливаются в единицу (фиг. 2 гид).

По переднему фронту импульсов цикла числа, записанные, в счетчиках 2 и 3, начинают считываться до нуля высокочастотными импульсами, поступающими на счетные входы счетчиков 2 и 3 с выхода блока 1 команд. Импульсы переноса счетчиков 2 и 3 опрокидывают RS-триггеры 6 и 7, причем

50

55

дом задатчика 12 и параллельным входом третьего счетчика 8) может быть задан вы- боро.м определенного числа двоичных разрядов записываемого в третий счетчик 8 кода сигнала задания.

Сигнал ошибки, преобразованный в соответствии с законом регулирования, поступает с выхода цифрового вычислительного блока 15 через элементы И 16 и 17 и через элемент ИЛИ 13 на счетный вход третьего счетчика 8 в зависимости от состояния триггера 14 знака и алгебраически суммируется в течение импульса цикла с записанным в третьем счетчике 8 числом (фиг. 2 ж).

Полученная в счетчике 8 сумма считывается в интервале между и.мпульсами цикла до нуля, импульсами с выхода блока 1 команд, поступаюнлими через элемент ИЛИ 10 на вычитающий вход третьего счетчика 8. Сигнал переноса третьего счетчика 8 устанавливает в нуль третий RS-триггер 9.

Таким образом, на выходе третьего RS-триггера 9 формируется дискретный цш- ротно-импульсный сигнал (фиг. 2 к) с регулируемой скважностью, который может быть преобразован в ток, напряжение, мощность.

Длительность выходных импульсов пропорциональна заданию и ошибке, а период следования равен периоду следования импульсов цикла.

Использование для формирования сигнала ошибки двух счетчиков, двух триггеров и логической схемы типа .И, ИЛИ вместо параллельного двоично-десятичного накапливающего сумматора и регистра памяти прототипа позволяет упростить схему и про

5

0

при наличии ошибки RS-триггеры R и 7 опрокидываются в разные моменты времени (фиг. 2 г и д).

Из выходных сигналов RS-триггеров 6 и 7 с помощью элементов И-НЕ 4 и 5 формируются импульсы с высокочастотным заполнением (фиг. 2е), число высокочастотных импульсов в которых пропорционально ошибке S. Полученные пачки импульсов поступают на один из входов триггера 14 знака, на выходах которого формируется сигнал знака ошибки S, а также через элемент ИЛИ 10 -- на вход цифрового вычислительного блока 15, где преобразуются в соответствии с законом регулирования.

Преобразование ошибки в выходной дискретный широтно-импульсный сигнал происходит в соответствии с временными диаграммами следующим образом.

По переднему фронту импульсов с выхода блока 1 команд (фиг. 3 б) в третий счетчик 8 по параллельному входу записывается в коде 8421 сигнал задания, а третий RS-триггер 9 устанавливается в единицу. Коэффициент передачи цепи управления но

5 заданию (участок цепи между вторым выхо5

0

0

5

0

5

дом задатчика 12 и параллельным входом третьего счетчика 8) может быть задан вы- боро.м определенного числа двоичных разрядов записываемого в третий счетчик 8 кода сигнала задания.

Сигнал ошибки, преобразованный в соответствии с законом регулирования, поступает с выхода цифрового вычислительного блока 15 через элементы И 16 и 17 и через элемент ИЛИ 13 на счетный вход третьего счетчика 8 в зависимости от состояния триггера 14 знака и алгебраически суммируется в течение импульса цикла с записанным в третьем счетчике 8 числом (фиг. 2 ж).

Полученная в счетчике 8 сумма считывается в интервале между и.мпульсами цикла до нуля, импульсами с выхода блока 1 команд, поступаюнлими через элемент ИЛИ 10 на вычитающий вход третьего счетчика 8. Сигнал переноса третьего счетчика 8 устанавливает в нуль третий RS-триггер 9.

Таким образом, на выходе третьего RS-триггера 9 формируется дискретный цш- ротно-импульсный сигнал (фиг. 2 к) с регулируемой скважностью, который может быть преобразован в ток, напряжение, мощность.

Длительность выходных импульсов пропорциональна заданию и ошибке, а период следования равен периоду следования импульсов цикла.

Использование для формирования сигнала ошибки двух счетчиков, двух триггеров и логической схемы типа .И, ИЛИ вместо параллельного двоично-десятичного накапливающего сумматора и регистра памяти прототипа позволяет упростить схему и производить чисто цифровую обработку сигнала ошибки, что приводит вместе с введением прямого канала регулирования к повышению точности регулирования.

Таким образом, предлагаемый цифровой регулятор может использоваться для регулирования любых параметров (давление, влажность, напряжение, ток, сопротивление и др.), преобразуемых в цифровую форму, в промышленности и в научных исследованиях.

Формула изобретения

10 мента ИЛИ, выход которого соединен с входом вычислительного блока, соединенного выходом с первыми выходами первого и второго элементов И, вторые входы которых соединены соответственно с инверсным и прямым выходами триггера знака, выход

. Цифровой регулятор, содержап;1ий задат- чик, аналого-цифровой преобразователь,

триггер знака и блок команд, отличаю- второго элемента И соединен с суммирую- щийся тем, что, с целью упрощения и по- шим входом третьего счетчика, вычитаюц-1ий

вход которого соединен с выходом второго элемента ИЛИ, параллельный вход - с

вторым выходом задатчика, а вход уставышения точности, введены первый и второй счетчики, счетные входы которых соединены с первыми входами первого и второго элементов И-НЕ и с первым выходом бло-20 новки - с S-входом третьего RS-тригге- ка команд, второй выход которого соединенра и третьим выходом блока команд, чет- с S-входами первого и второго RS-тригге-вертым выходом соединенного с входом вто- ров и входами установки первого и второ-рого элемента ИЛИ, второй вход которого счетчиков, параллельные, входы которыхго соединен с выходом первого элемента И, соединены соответственно с выходами анало-а R-вход третьего RS-три.ггера соединен с го-цифрового преобразователя и с первым25 выходом переноса третьего счетчика.

и вторым выходами задатчика, а выходы переноса - с R-входами соответственно первого и второго RS-триггеров, инверсные выходы которых соединены с вторыми входами соответственно второго и первого элементов И-НЕ, третьи входы которых соединены с прямыми выходами соответственно первого и второго RS-триггеров, а выходы - соответственно с первыми и вторыми входами триггера знака и первого элемента ИЛИ, выход которого соединен с входом вычислительного блока, соединенного выходом с первыми выходами первого и второго элементов И, вторые входы которых соединены соответственно с инверсным и прямым выходами триггера знака, выход

второго элемента И соединен с суммирую- шим входом третьего счетчика, вычитаюц-1ий

вторым выходом задатчика, а вход установки - с S-входом третьего RS-тригге- ра и третьим выходом блока команд, чет- вертым выходом соединенного с входом вто- рого элемента ИЛИ, второй вход которого соединен с выходом первого элемента И, а R-вход третьего RS-три.ггера соединен с выходом переноса третьего счетчика.

а)

Tempamoj) импульсов дысокои. частоты

(Pus. 3

| название | год | авторы | номер документа |

|---|---|---|---|

| Электропривод | 1985 |

|

SU1275726A1 |

| Цифровой регулятор | 1982 |

|

SU1013907A1 |

| Устройство для регулирования температуры | 1986 |

|

SU1403025A1 |

| Цифровой регулятор | 1982 |

|

SU1019397A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1262504A1 |

| Устройство для регулирования скорости электродвигателя | 1984 |

|

SU1267375A1 |

| Устройство автоматического управления моталкой литейно-прокатного агрегата | 1983 |

|

SU1135514A1 |

| Цифровой следящий электропривод | 1985 |

|

SU1308982A1 |

| Устройство для управления многоканальным вибростендом | 1980 |

|

SU924665A1 |

| Гистерезисный электропривод | 1984 |

|

SU1261078A1 |

Изобретение относится к статическим системам автоматического регулирования и может быть использовано для регулирования одного параметра или соотношения двух параметров технологического процесса. Цель изобретения - повышение точности и упро- шение цифрового регулятора. Цифровой регулятор содержит блок 1 команд, первый 2 и второй 3 счетчики, первый 4 и второй 5 элементы И-НЕ, первый 6 и второй 7 RS- триггеры, третий счетчик 8, третий RS-триг- гер 9, первый элемент ИЛИ 10, аналого- цифровой преобразователь 11, задатчик 12, второй элемент ИЛИ 13, триггер знака 14, цифровой вычислительный блок 15, первый 16 и второй 17 элементы И. Цель изобретения достигается за счет введения элементов и блоков 2-10, 13, 15-17. 3 ил. Па/зс л. вшоа фиг. 1

| Круг Е | |||

| К., Дилигенский С | |||

| Н | |||

| Принципы построения одноканальных цифровых регуляторов | |||

| М.: Советское радио, 1969 |

Авторы

Даты

1987-02-28—Публикация

1985-02-04—Подача