(54) ЗАПОМИНАЮЩИЙ МОДУЛЬ ДЛЯ ПОСТОЯННЫХ . .БЛОКОВ ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающий модуль для постоянной памяти | 1981 |

|

SU991510A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU752482A1 |

| Матричный накопитель для интегральных запоминающих устройств | 1977 |

|

SU710075A1 |

| ЭЛЕМЕНТ ПАМЯТИ | 1992 |

|

RU2032944C1 |

| Оперативное запоминающее устройство | 1980 |

|

SU942140A1 |

| Оптоэлектронное запоминающее устройство | 1982 |

|

SU1072096A1 |

| Постоянное запоминающее устройство | 1981 |

|

SU987680A1 |

| Электронное устройство | 1987 |

|

SU1427518A2 |

| Матричный накопитель для постоянного запоминающего устройства | 1982 |

|

SU1043752A1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1112411A1 |

. 1 .

Изобретение относится к области вычислительной техники, в частности к микроэлектроиным ЗУ и может быть использовано в устройствах обработки цифровой информации в качестве памяти подпрограмм, табличных данных, функций, преобразователей кодов и др.

Известен запоминающий модуль для : постоянных блоков памяти, содержащий матричный накопитель с элементами на диодах Щ .

Из известных запоминающих модулей для постоянных блоков памяти наиболее, близким по технической сущности К изобретению является запомина ощий модуль, содержащий матричный накопитель с элементами связи на анодах, элементы сог ласования на резисторах, вентильйые элеменпгы на диодах, элементы форсирования исходного состояния на диодах, две дополнительные шины с элементами связи запоминакщего модуля на диодах, предназначенные для варьирования разрядности зайоминагащего модуля, п защитные элементы на диодах 2 .

Недостатками этих запоминают их модулей являются высокий уровень выходнотх) сигнала логического нуля, большая Выходная емкость .и отсутствие расшифровки адреса.

Это снийсает их надежность и ограни чивает повышение степени интеграции.

Целью изобретения является повышение надежности и степени интеграции запоминающего модуля.

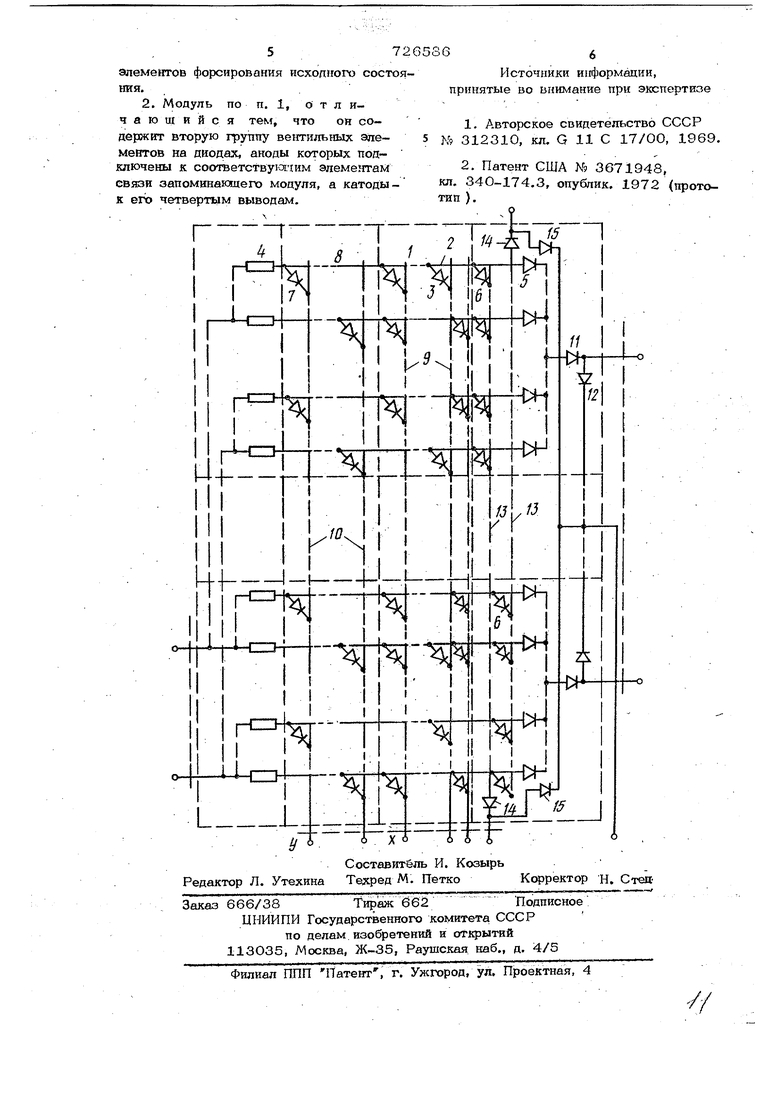

Для достижения этой цели предложенный запоминающий модуль дополнительно содержит п«рвую группу вентильных элементов на диодах, адресные шины и адресные элементы связи на диодах, катоды которых подключены к адресным шинам, а аноды - к разрядным шинам запоминающего модуля. Аноды диодов ,вентшиьных элементов первой группы подключены к кагодам диодов вентильных элементов, а катоды - к тоетьим соответствующим выводам 3- 72 раттоминакшего модуля, к которым подключены также аноды соответствую щих диодов элементов форсирования йс бедного состояния. при варьировании разрядностй или повышения надежности запоминающий йодупь вторую групну вентильных элементов на диодах. .На чертеже представлена электрическая: схема предложенНоГо запоминеющего модуля., Запоминакадий модуль содержит мат риЧ1й 1й Накопитель 1, разделанный на m секций, где Ж - число разрядов дво- ичных слоев, разрядные шины 2, к кото рым подключены аноды диодов элементов связи 3, элементы согласования: на ре зисторах 4, аноды диодов вентильных элементов 5, аноды дйодоё ёлё мёйтов связи запоминакщего модуля 6, предназ наченные для варьирования разрядности и аноды диодов адресных элементов связи 7 адресного блока 8, Вторые выводы согласования иа резистораа 4 подключены к соответствукщнм первым выводам запоминающего модуля. Числов;ые шины 9 матричного накопителя 1 сбгёдвйейы с катодами диодов элементов связи 3. и,.имеют внешше выводы i . Адресные шинь 10 соединены с катодами диодов адрес1 Ых Цементов связи 7 дмеют внешние выводы У . Вентильные ...-.-v---v... - - --:- „ элементы на диодах первой группы 11 подключены анодами к выходам (катодам BeisTimbHbix элементов на диодах 5, а ка тодами - ко входам (анодам) диоДов э сементов форсирования исходного состо ния 12. Дополнительные шины 13 для варьирования разрядности соединены с .катодами диодбв элементов связи, запрм накзцего модул.п 6,прёдназначенньтё для варьирования разрядности, и с анодом диодов вентитлЕЫх элементов второй группы 14. Выходы (катоды), последних соединены с анодами диодов элементов форсирования исходного СОСТОЯЕШЯ 15, Выходы (катоды) диодов элементов форсирования исходного состояния 12 н 15 подключены ко второму обцему выводу запоминающего модуля, а катоды диодов вентильных Элементов первой и второй групп подключены к третьим и четверты выводам запоминаклцего модузта соответ ственнб. Запоминающий модуль работает следуктоим образом. На один из первых выводов запомина юдего модуля подается высокий уровень апряжения (на осталь№1ё первые вывоы подается низкий ypoBetfb напряжения). ри этом в каждой секции предварительо выбираются те разрядные шины, котоые через элементы согласования на реисторах подключены к тому выводу заo raнaющeгo модуля, на который подан ысокий уровень напряжения. Выбор одой разрядной шины в каждой секции осуествляется подачей соответствующей омбинации высоких и низких напряжений а входы У . Для выбора необходимохх) слова из всех X входов, Кроме одного, подается высокий уровень напряжения. При этом выбраны те элементы связи на диодах, выходы (.катоды) которых подключены к тому входу X , на который подан низкий уровень напряжения. При этом с выхода запоминающего-модуля считывается W-разрядное слово., 1аки:м образом, наделсность и степень интеграции предлагаемого запоминающего модуля по сравнению с известными повышены. Формула«изобретения 1. Запоминающий модуль для постоянных блоков памяти, содержащий матричный накопитель с элементами связи на диодах аноды которых подключены к разрядным шинам запоминающего модуля, а катодык числовым шинам, элементы соглас ва- ния на резисторах и вентильные элементы на диодах, аноДы которых и одни выводы резисторов элементов согласования подключеггь к разрядным шинам, а другие вы-г воды - к первому выводу запоминающего модуля, элементы форсирования . исходного СОСТОЯНИЯ на диодах, катойЬ которых подключены ко второму общему выводу запоминающего модуля, о т л и ч а ю щ и и с я тем, что, с целью повы шения йадежности и степени интеграции з ррминакщего модуля, он содержит первую гру11пу ;веитилы1ых элементов на диодах,адресные шины и адресные элементы связи на диодах, катоды которых подключены к адресным шинам, а аноды - к разрядным шинам запоминающего модуля, аноды диодов вентильных элементов первой группы подключены к катодам дяодйв вентильных элементов, а катоды - к третьим соответствующим выводам запоми- наюшего модуля, к которым подключены также аноды соответствукихих диодов

5726536 j

элементов форсирования исходного состоя-Источники информации,

принятые во внимание при экспертизе

Авторы

Даты

1980-04-05—Публикация

1977-12-23—Подача