Изобретение относится к вычислительной технике, в частности, к микроэлектронным запоминающим устройствам, и может быть использовано в устройствах обработки двоичной информации в качестве памяти прдпрограмм, табличных данных, функций и преобразователей кодов.

Известен запоминающий модуль для постоянной памяти, содержащий диодный матричный накопитель, резисторы и две дополнительные шины с диодами для варьирования разрядности двоичного слова, выходные диодные сборки, дополнительные диоды для форсированного установления исходного состояния 1.

Недостатком этого запоминающего модуля для постоянной памяти является полное отсутствие в нем расширения адреса, что приводит к излишне большому количеству внешних выводов, увеличивает количество паяных соединений при сборке запоминающего модуля, снижает его надежность, а также является ограничивающим фактором увеличения степени интеграции запоминакядего модуля.Наиболее близким по технической сущности к изобретению является запоминающий модуль для постоянной памяти, который содержит матричный накопитель с элементами связи на диодах, катоды .которых объединены по столбцам и являются числовыми шинами и входами первой группы запоминающего модуля, а аноды объединены по строкам и являются разрядными шинами, которые объединены в группы, а группы - в секции, резисторы согласования, одни выводы которых подключены к разрядным шинам каждой группы, а другие выводы соответствующих резисторов каждой группы объединены и ЯВ.71ЯЮТСЯ вхо)1ами второй группы запоминающего модуля, диоды развязки, аноды которых подключены к разрядным шинам каждой группы, а катоды объединены по группам и подключены к анодам диодов развязки групп, диоды дешифрации, аноды которых подключены к разрядным шинсм, а катоды соответствующих диодов дешифрации объединены и являются входами третьей группы запоминанвдего модуля, диоды форсирования исходного состояния, катоды которых объединены и являются входом запоминакядего модуля, la аноды подключены к выходам запо30 у,4инающего модуля.

Кроме того, запоминающий модуль содержит диоды для варьирования разрядности двоичного слова, аноды которых подключены к разрядным шинс1М, а катоды - к шинам варьирования разрядности двоичного слова 2.

Недостатком этого запоминающего модуля является большое число диодо дешифрации, что ведет к усложнению запоминающего модуля, следовательно, снижает надежность его функционирова ния.

Целью изобретения является уменьшение числа диодов дешифрации, следовательно, повышение надежности запоминающего модуля . Поставленная цель достигается тем, что в запоминающем модуле для постоянной памяти, содержащем матричный накопитель с элементами связи на диодах, катоды которых объединены по столбцам и являются числовым шинами и входами первой группы запоминающего модуля, а аноды объединены по строкам и являются разрядными шинами, которые объединены в груп пы, а группы - в секции, резисторы согласования, одни выводы которых подключены к разрядным шинам каждой группы, а другие выводы соответствующих резисторов каждой группы объединены и являются входами второй групп запоминающего модуля, диоды развязки, аноды которых подключены к разряным шинам каждой группы, акатоды объединены по группс№1 и подключены к анодам диодов развязки групп, диод дешифрации, катоды которых объединены с катодами соответствующих диодов других секций и являются входами третьей группы запоминающего модуля, диоды форсирования исходного состояния, катоды которых объединены и являются входом запоминающего модуля, аноды диодов дешифрахщи и диодов форсирования исходного состояния подключены к анодам диодов развязки групп, катоды которых в каждой секции объединены и являются выходами запоминающего модуля.

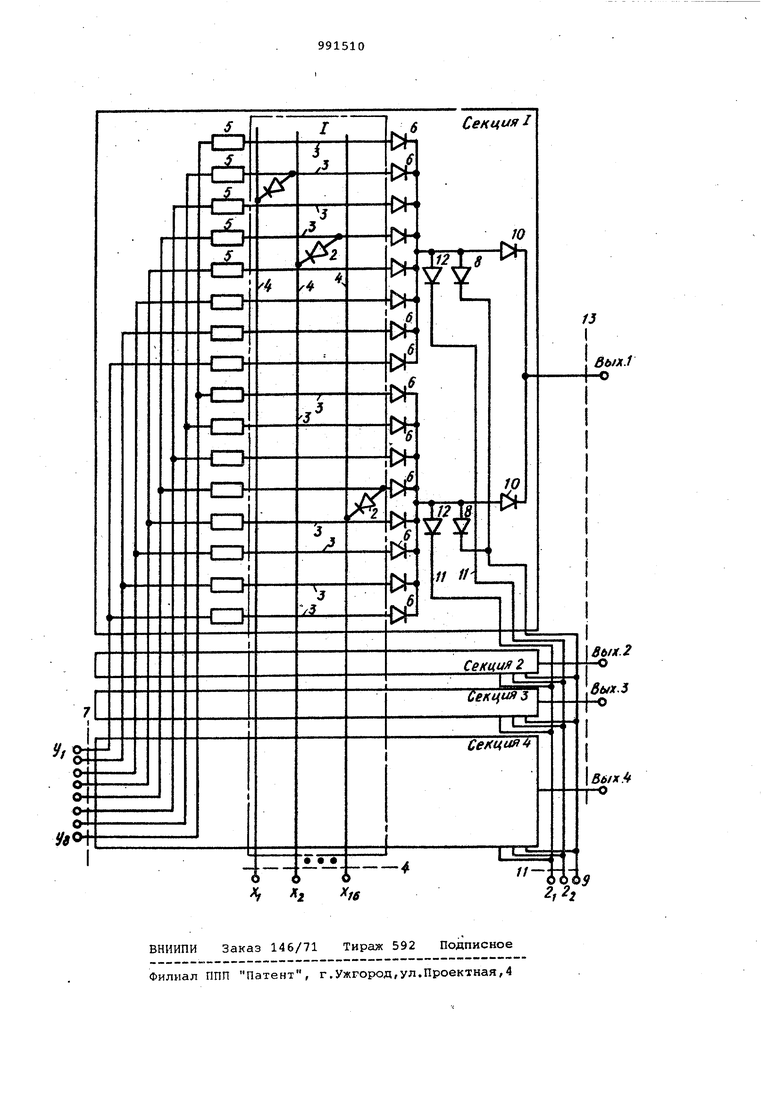

На чертеже приведена электрическа схема предложенного запоминающего модуля информационной емкостью 1024 (256x4) бит.

Запоминающий модуль .для постоянной памяти содержит матричный накопитель 1, разделенный на ю секций, где m -. разрядность двоичного сяова (для случая, приведенного на чертеже, равна 4), с элементами связи на диодах 2, аноды которых подключены к разрядным шинам 3 запоминающего модуля, а катоды - к числовым шинам, которые являются входами 4 первой группы запоминающего модуля, резисторы 5 согласования, диоды 6 ,раэвязки, аноды которых и одни выводы резисторов 5 согласования подключены, к разрядным шинам 3, а другие выводы резисторов согласования - к входам 7 второй группы запоминающего модуля. При этом катоды диодов 8 форсирования исходного состояния подключены к выводу 9 запоминающего модуля. Запоминающий модуль содержит также диоды 10 развязки группы, входы третьей группы 11 и диоды дешифратора 12, катоды которих подключены к шинам 11, причем аноды диодов развязки групп 10 подключены к катодам диодов б развязки, а катоды их являются выходами 13 запоминающего модуля. Аноды диодов 12 дешифрации и аноды диодов 8 форсирования исходного состояния подключены к анодам соответствующих диодов 10 развязки группы, катоды которых объединены в каждой секции.

Запоминающий модуль для постоянной памяти работает следующим образом.

На одни из входов 4 первой группы (X ) подается низкий уровень напряжения, на одни из входов 7 второй группы (Y) подается высокий уровень напряжения, а на входы 11 третьей группы (Z) подается комбинация высоких и низких уровней напряжения в зависимости от кодасоответствующих разг рядов адреса.

В результате из запоминанлцего Ьмодуля считывается m разрядное двоич,ное слово, значение разрядов которого определяется наличием или отсутствием элементов связи на диодах 2 на пересечении выбранных разрядных проводов и выбраннс го числового провода. После завершения считывания на вход 9 подается низкий уровень напряжения для форсирования процесса разряда паразитных емкостей выбранных разрядных шин.

Предложенный з.апоминающий модуль по сравнению с известным содержит значительно меньшее число диодов дешифрации. Так например,для рассмотренного случая, когда емкость модуля равна 1024 (256x4) бита, число диодов дешифрации у известного равно 64 (14x4), а у. предложенного устройства 8 (2x4). Это упрощает конструкцию и технологию изготовления запоминающего модуля, в результате чего надежность функционирования запоминающего модуля по сравнению с известными повышается.

Формула изобретения

Запоминающий модуль для постоянной памяти, содержащий матричный накопитель с элементами связи на диодах, катоды которых объединены

по столбцам и являются числовыми шинами и входами первой группы запоминающего модуля, а аноды объединены по строкам и являются разрядными шинами, которые объединены .в группы, а группы - в секции, резистры согласования, одни выводы которых подключены к разрядным шинам каждой группы, а другие вывода соответствукмих резисторов каждой группы объединены и являются входами второй группы запоминающего модуля, диоды развязки, аноды которых подключены к разрядным шинам каждой , а катоды объединены по груп пам и подключены к анодам диодов развязки групп, диоды дешифрации, катоды которых объединены с катодами соответствующих диодов других секций и являются входами третьей

группы запоминающего модуля, диоды форсирования исходного состояния .катоды которых объединены и являются входом згшомннающего модуля, отличающийся тем, что, с целью повышения нгшежности запоминающего модуля, аноды диодов дешифрации и диодов форсирования исходного состояния подключены к анодам диодов развязки групп, катоды которых в каждой секции объединены и являются выходгши запоминающего модуля.

Источники информации, принятые во BfiHMaHue при экспертизе 1. Патент ОНА 3671948, кл.340-174.3, опублик. 1972.

2. Авторское свидетельство СССР 726586, кл. G 11 С 11/00, 1980 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающий модуль для постоянных блоков памяти | 1977 |

|

SU726586A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU752482A1 |

| Полупостоянное запоминающее устройство с электрической перезаписью информации | 1983 |

|

SU1088068A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА СИГНАЛОВ КОМАНДНОЙ МАТРИЦЫ | 2011 |

|

RU2487393C1 |

| Электронное устройство | 1987 |

|

SU1427518A2 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ИНФОРМАЦИИ | 1985 |

|

RU1358631C |

| Реверсивный дешифратор | 1976 |

|

SU604151A1 |

| Вычислительное устройство и запоминающий масштабно-суммирующий блок | 1980 |

|

SU1043670A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ | 1972 |

|

SU434481A1 |

| Устройство для записи информации в матричные накопители на ферритовых сердечниках | 1980 |

|

SU888201A1 |

Авторы

Даты

1983-01-23—Публикация

1981-06-04—Подача