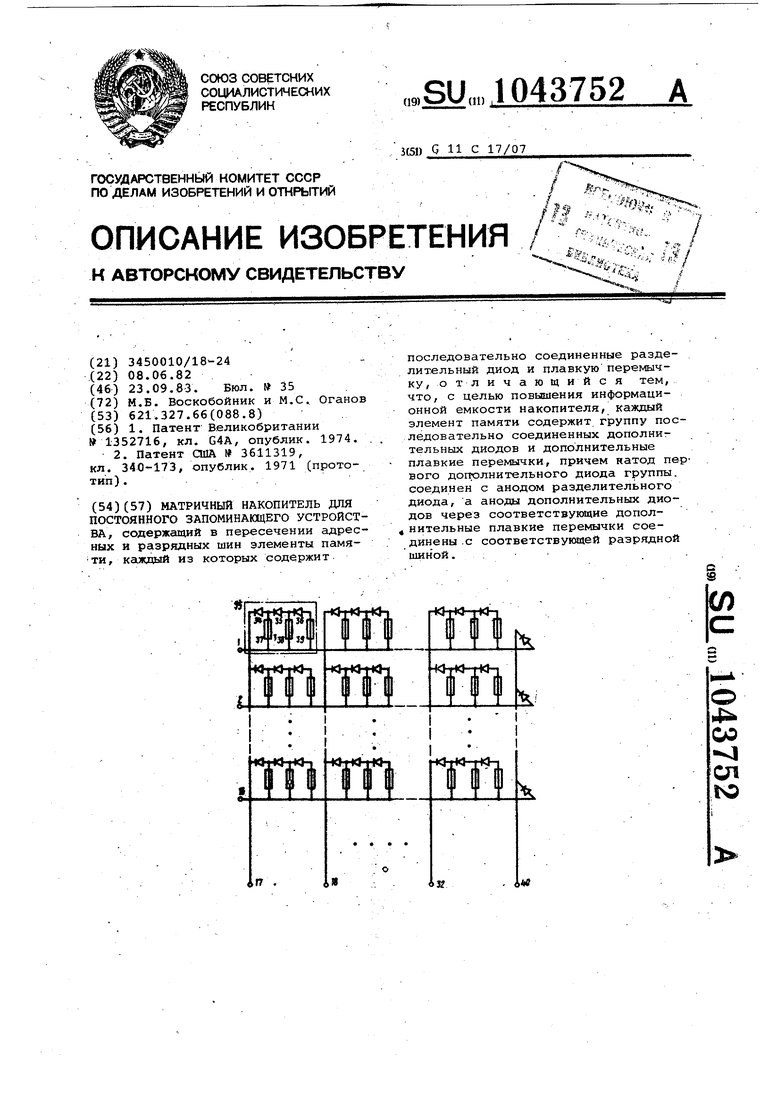

Изобретение относится к вычислительной технике и может быть ис пользовано в системах памяти вычи лительных устройств. . Известен матричный накопитель ПЗУ, содержащий адресные и разряд шины и элементы памяти. Каждый эл мент памяти содержит два навстречу включенных диода и соединен с соответствующей адресной и разряд ной шинами С 1 1Недостатком такого устройства является то, что до ввода информа ции все элементы памяти матричног накопителя находятся в непроводящем состоянии, что исключает возможность контроля электрических п раметров элементов памяти. Наиболее близким к предлагаемом по технической сущности является матричный накопитель ПЗУ, содержащий адресные и разрядные шины и элементы памяти, каждый из которых содержит диод, последовательно сое диненный с разрушаемой перемычкой С2. Недостатком такого устройства является небольшая информационная, емкость, ограниченная произведением числа адресных шин на число разрядных шин. Цель изобретения повышение ин формационной емкости матричного на копителя ПЗУ. Поставленная цель достигается тем, что в матричном накопителе дл постоянного запоминающего устройст ва ,, содержащем в пересечении адрес ных и разрядных шин элементы памяти, каждый из которых содержит пос ледовательно соединенные разделительный диод и плавкую перемычку, каждый элемент памяти содержит группу последовательно соединенных дополнительных диодов и дополнител ные плавкие , причем катод первого дополнительного диода группы соединен с анодом разделительного диода, а аноды дополнител ных диодов, через соответствуницие дополнительные плавкие перемычки соединены с соответствующей разрядной шиной. В случае, когда все перемычки включены, падение напряжения на элементе памяти определяется одним диодом, что соответствует первому состоянию элемента памяти. После разрушения первой перемычки падение напряжения на элементе памяти определяется двумя диодами, что соответствует второму состоянию элемента памяти, после разрушения второй перемычки падение напряжения ha элементе памяти определя,ется тремя диодами, что соответств ет третьему состоянию элемента памяти и т.д. После разрущения последней i-й перемычки все i диодов, содерж и ся в элементе памяти, оказываются отключенными от разрядной шины, что соответствует i+l состоянию элемента памяти. Информационная емкость такого элемента па1у1яти равна 1 бит. ,. На чертеже представлена принципиальная электричческая схема матричного накопителя ПЗУ с информационной емкостью 512 бит. Устройство представляет собой систему из шестнадцати разрядных шин 1-16 и шестнадцати адресных шин 17-32, расположенных на сапфироЬой подложке. В каждом пересечении шин размещен элемент 33 памяти, включающий три последовательно соединенных диода (разделительного 34 и дополнительных 35 и 36). Катод диода 34 соединен с адресной шиной 17, а аноды диодов 34, 35 и 36 через соответствующие плавкие перемычки (основную 37 и дополнительные 38 и 39) соединены с разрядной шиной 1. Ввод информации осуществляется j электрическим разрушением перемычки.. Выбор элемента памяти как в режиме считывания, так и в режиме ввода информации осуществляется через соответствующие адресные и разрял ные шины с помощью обычных адресных устройств. Наличие всех трех перемычек в элементе памяти соответствует первому состоянию элемента памяти. Перевод элемента памяти во второе состояние осуществляется пропуск-анием тока величиной 60-70 мА. При этом ток протекает через диод 34 и перемычку 37. Через перемычки 38 и 39 ток практически не течет из-за шунтирующего действия перемычки 37. При прохояспении . указанного тока в течении 10 с перемычка 37 разрушается. Элемент памяти переходит во второе состояние. После разрушения перемы ки 37 ток через элемент памяти падает до величины 30-35 мА из-за подключения диода 35. Этот ток недостаточен для разрушения перемычки 38. Для перевода элемента памяти в третье состояние необходимо снова пропустить через элемент пё1мяти ток величиной &0-70 мА. При этом разрушается перемычка 38. Из-за подключения диода 3 ток через элемент памяти падает до 40-45 мА, что недостаточно для разрушения перемычки 39. Для перевода элемента памяти в четвертое состояние необходимо

снова пропустить через элемент памяти ток величиной 60-70 мА, при этом перемычка 39 разрушается и все диоды оказываются отключенными от разрядной шины 1.

.При работе устройства в режиме считывания информации, содержащейся в матричном накопителе, выбирается один определенный, элемент памяти; В зависимости от состояния, в котором он находится, на шине 40 считывания появляется один иэ четырех возможных уровней напряже- ния, например при напряжении пи. тания +5 В и сопротивлении в цепи питания 2,5 кОм следующие уровни напряжения: для первого состояния 0,8 В, для второго состояния 1,6 В, для третьего состояния 2,4 В, для четвертого состояния 5,0 В. Четыре уровня напряжения соответствуют двум битам информации.

Технико-экономическая эффективность предлагаемого изобретения сшределяется увеличением информационной емкости матричного накопителя ПЗУ без увеличен 1я числа адрес-.

ных и разрядных шин.

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1982 |

|

SU1112411A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU752482A1 |

| НАКОПИТЕЛЬ ЭЛЕКТРИЧЕСКИ ПРОГРАММИРУЕМОГО ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1991 |

|

RU2028676C1 |

| Постоянное запоминающее устройство | 1985 |

|

SU1305775A1 |

| Запоминающее устройство с произвольной выборкой | 1977 |

|

SU769626A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1989 |

|

SU1669307A1 |

| ЭЛЕМЕНТ ПАМЯТИ | 1992 |

|

RU2032944C1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1988 |

|

SU1778790A1 |

| Накопитель для постоянного запоминающего устройства | 1981 |

|

SU1034073A1 |

МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА, содержащий в пересечении адресных и разрядных шин элементы памяТи, каждый из которых содержит последовательно соединенные разделительный диод и плавкуюперемычку, о тли чающий с я тем, что, с целью повышения информационной емкости накопителя, каждый элемент памяти содержит группу последовательно соединенных дополнительных диодов и дополнительные плавкие перемычки, причем катод первого доп элнительного диода группы, соединен с анодом разделительного диода, а аноды дополнительных диодов через соответствуквдие дополнительные плавкие перемычки соединены .с соответствующей разрядной шиной. ; . (Л 4; 00 сд ю

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент Великобритании №1352716, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

| , 2 | |||

| Патент США № 3611319, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Устройство станционной централизации и блокировочной сигнализации | 1915 |

|

SU1971A1 |

Авторы

Даты

1983-09-23—Публикация

1982-06-08—Подача