, / Изобретение относится к запоминающим устройствам и может быть использовано для построения блоков оперативной памяти иерархической структуры с блочным Семеном информации между уровнями памяти.

Известно устройство, содержащее основную оперативную память, полупроводниковую или на магнитных сердечниках, сверхоперативную память tO Ю

Недостаток устройства состоит в его сложности.

Наиболее близким техническим решением к предлагаемому является оперативное запоминающее устройство, со-ts держащее полупроводниковый буферный сверхоперативный накопитель и оперативный накопитель на магнитных сердечниках, включенные в каскад .

Недостаток устройства заключает- W ся в невысоком быстродействии из-за большой разницм времен обращения к полупроводниковому накопителю и к накопителю на магнитных серде чниках.

Цель изобретения - повышение быст родействия оперативного запоминающего уст ройства.

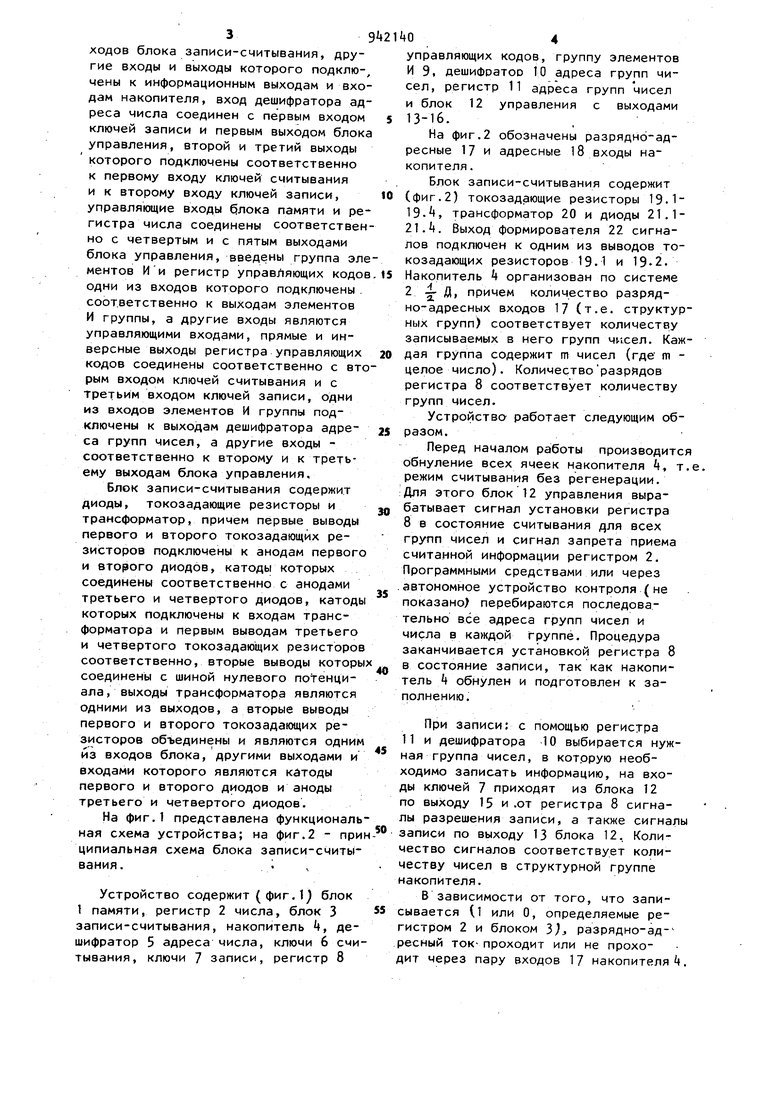

Поставленная цель достигается тем, что в оперативное запоминающее устройство, содержащее блок памяти, регистр числа, блок записи-считывания, накопитель, дешифратор адреса числа, ключи записи, ключи считываний, блок управления, дешифратор, адреса групп чисел, выходы которого подключены к входам дешифратора адреса гРУпп чисел причем выходы ключей считывани)1 и ключей записи соединены с разрядно. адресными входами накопителя, адресные входы которого подключены к одним из. выходов дешифратора адреса числа, другие выхбды которого соединены с адресными входами блока памяти, информационные входы и выходы которого подключены соответственно к одним из выхо дов и входов регистра числа, другие выходы и входы которого соединены соответственно с одними из входов и вы3ходов блока записи-считывания, другие входы и выходы которого ПОДКЛЮчены к информационным выходам и вхо дам накопителя, вход дешифратора ад реса числа соединен с первым входом ключей записи и первым выходом блока управления, второй и третий выходы которого подключены соответственно к первому входу ключей считывания и к второму входу ключей записи, управляющие входы блока памяти и ре гистра числа соединены соответствен но с четвертым и с пятым выходами блока управления, введены группа эле ментов Ии регистр управляющих кодо одни из входов которого подключены . соответственно к выходам элементов И группы, а другие входы являются управляющими входами, прямые и инверсные выходы регистра управляющих кодов соединены соответственно с вто рым входом ключей считывания и с третьим входом ключей записи, одни из входов элементов И группы подключены к выходам дешифратора адреса групп чисел, а другие входы соответственно к второму и к третьему выходам блока управления. Блок записи-считывания содержит диоды, токозадающие резисторы и трансформатор, причем первые выводы первого и второго токозадающйх резисторов подключены к анодам первого и второго диодов, катоды которых соединены соответственно с анодами третьего и четвертого диодов, катоды которых подключены к входам трансформатора и первым выводам третьего и четвертого токозадающйх резисторов соответственно, вторые выводы которы соединены с шиной нулевого по енциала, выходы трансформатора являются одними из выходов, а вторые выводы первого и второго токозадающйх резисторов объединены и являются одним из входов блока, другими выходами и входами которого являются катоды первого и второго диодов и аноды третьего и четвертого диодов, На фиг.1 представлена функциональ ная схема устройства; на фиг.2 - при ципиальная схема блока записи-считывания,ч Устройство содержит ( фиг.1) блок 1 памяти, регистр 2 числа, блок 3 записи-считывания, накопитель , дешифратор 5 адреса числа, ключи 6 счи тывания, ключи 7 записи, регистр 8 O4 управляющих кодов, труппу элементов И 9, дешифратор 10 адреса групп чисел, регистр 11 адреса групп чисел и блок 12 управления с выходами 13-16. На фиг.2 обозначены разрядно-адресные 17 и адресные 18 входы накопителя. БЛОК записи-считывания содержит С фиг.2) токозадающие резисторы 19.1 19., трансформатор 20 и диоды 21.121.. Выход формирователя 22 сигналов подключен к одним из выводов токозадающйх резисторов 19.1 и 19-2. Накопитель k организован по системе 2 Д, причем количество разрядно- адресных входов 17 (т.е. структурных групп) соответствует количеству записываемых в него групп чисел. Каждая группа содержит m чисел (где m целое число). Количестворазрядов регистра В соответствует количеству групп чисел. Устройство работает следующим образом. Перед началом работы производится обнуление всех ячеек накопителя k, т.е. режим считывания без регенерации. Для этого блок 12 управления вырабатывает сигнал установки регистра 8 в состояние считывания для всех групп чисел и сигнал запрета приема считанной информации регистром 2. Программными средствами или через автономное устройство контроля (не показано) перебираются последовательно все адреса групп чисел и числа в каждой группе. Процедура заканчивается установкой регистра 8 в состояние записи, так как накопитель k обнулен и подготовлен к заполнению. При записи; с помощью регистра 11 и дешифратора 10 выбирается нужная группа чисел, в которую необходимо записать информацию, на входы ключей 7 приходят из блока 12 по выходу 15 и .от регистра 8 сигналы разрешения записи, а также сигналы записи по выходу 13 блока 12.. Количество сигналов соответствует количеству чисел в структурной группе накопителя. В зависимости от того, что записывается (1 или О, определяемые регистром 2 и блоком 3), разрядно-адресный ток-проходит или не проходит через пару входов 17 накопителя4.

Одновременно сигналы записи подаюся и на дешифратор 5 в соответствии с кодом адреса выбранного числа.

Как при записи, так и при считывании из блока 12 по выходу 16 подаются синхросигналы с частотой повторения в vn раз меньшей частоты повторения сигналов записи или чтения, подаваемых по выходу 13.

После прохождения последнего рм-г сигнала записи синхросигнал устанавливает регистр 8 в состояние, соотвествующее готовности данной группы чисел к чтению. Если же в этой групп чисел происходит обращение снова по записи (вместо чтения), то управление от регистра 8 осуществляет запрет по входу ключей 7, а синхросигнал подтверждает состояние готовности группы чисел к считыванию, т.е при случайном неправильном обращении происходит защита информации.

Процесс считывания информации из группы чисел происходит во многом аналогично процессу записи. Однако отличительной особенностью работы накопителя Ц при считывании является то, что длительность разрядно-адресного тока определяется не длительностью сигналов, поступающих с выхода 13, а временем действия разрешающего сигнала, поступающего на ключи 6 от блока 12 по выходу .14. После установления разрядно-адресного тока на паре входов 17 (амплитуды тока на каждом входе одинаковы и определяются резисторами 19 и приложенным напряжением) подается через дешифра- . тор 5 адресный ток считывания на выбранный вход 18. От воздействия суммы двух токов переключается выбранный сердечник (если он был в соетоянии 1) и ЭДС переключения проявляется в виде разбаланса моста, образованного парой входов 17 и резисторами 19. Трансформатор 20, в клюменный в диагональ этого моста,воспринимает и передает считанный си1- нал к усилителю (не показан), с выхода которого он поступает на регистр 2.

После прохождения последнего т-го сигнала считывания синхросигнал устанавливает регистр 8 в состояние О, подготовленное соответствующим из элементов И 9 и в соответствующее по готовности данной группы ячеек накопителя А к записи.

Таким образом, в устройстве осуществляется считывание без регенерации и запись без каждого циклового обнуления, а также исключается время успокоения помех в цепи съема. Последнее объясняется тем, что при блочном считывании разрядно-адресный ток на входах 17 не выключается при переходе от адреса к адресу группы чисел, в результате чего помехи в цепях съема фактически отсутствуют. Эти свойства повышают надежность и быстродействие устройства.

Технико-экономическое преимущество предлагаемого устройства заключается в значительном повышении быстродействия устройства по сравнению с прототипом.

Формула изобретения

1. Оперативное запоминающее устройство, содержащее блок памяти, регистр числа, блок записи-считывания, накопитель , дешифратор адреса числа ключи записи, ключи считывания, бло управления, дешифратор адреса групп чисел и регистр адреса групп чисел, выходы которого подключены к входам дешифратора адреса групп чисел, причем выходы ключей считывания и ключей записи соединены с разрядно-ад ресными входами накопителя, адресные входы которого подключены к одним из выходов дешифратора адреса числа, другие выходы которого соединены с адресными входами блока памяти, информационные входы и выходы которого подключены соответственно к одним из выходов и входов регистра числа, другие выходы и входы которого соединены соответственно с одними из входов и выходов блока-записи-считывания, другие входы и выходы которого подключены к информационным выходам И входам накопителя, вход дешифратора адреса числа соединен с первым входом ключей записи и первым выходом блока управления, второй и третий выходы которого подключены соответственно к первому входу ключей считывания и к второму входу ключей записи, управляющие входы блока памяти и регистра числа соединены соответственно с четвертым и с пятым выходами блока управления, отличаю ще ее я тем, что,с целью пoвышeн fя быстродействия устройства, оно содержит группу элементов И и perMctp управляющих кодов, одни из входов которого подключены соответственйо к выходам,элементов И группы, а другие входы являются управляющими входами, Ьрймые и инверсные выходы регистра управляющих кодов соединены соответственно с вторым входом ключей считывания и с третьим входом ключей записи, одни из входов элементов И группы подключены к выходам дешифратора адреса трупп чисел, а другие входы - соответственно к второму и к TpetbeMy выходам блока управления.

2. Устройство по п.t, о т л и ч аю щ е ее я тем, что блок записисчитывания содержит диоды, токозадающйе резисторы и tpaHc0opMaTOp,причем первые выводы первого и Bfoporo токозадающих резисторов подключены к айодам первого и второго диодов, катоды которых соединены соответственно с анодами трбтёьго и четверТОГО диодов , катоды которых подключены к входам трансформатора и первым выводам третьего и четвертого токозадающих резисторов соответственноу вторые выводы котосшх соединены с шиной нулевого потенциала, выходы трансформатора являются одними из выходов, а вторые выводь первого и второго токозадающих резисторов объединены и являются одним из входов блока, другими выходами и входами которого являются катоды, первого и второго диодов и аноды третьего и Четвертого диодов.

Источники информации, пpиняtыe во внимание при экспертизе 1.Шигин А.Г. и Дерюгин А.А. Циф/ровые вычислительные машины. М.Энергия, 1975, с.97-521. : .

2. Шабалии 8.В. и др. Интегральные функциональные запоминающих уст|рюйсТвМ. Сов.радио, 19716. Ci 5т9 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1976 |

|

SU608197A1 |

| Запоминающее устройство | 1980 |

|

SU940235A1 |

| Запоминающее устройство | 1979 |

|

SU809367A1 |

| МНОГОПОЗИЦИОННАЯ МАТРИЦА УПРАВЛЕНИЯ | 1972 |

|

SU337818A1 |

| Устройство для контроля матриц памяти на цилиндрических магнитных пленках с неразрушающим считыванием информации | 1986 |

|

SU1387045A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Запоминающее устройство | 1968 |

|

SU842961A1 |

| Постоянное запоминающее устройство | 1977 |

|

SU834768A1 |

| Устройство для обмена информацией | 1979 |

|

SU849193A1 |

| Генератор псевдослучайных чисел | 1976 |

|

SU693408A1 |

-

9

Ю

тч

-f

гСр

dLjC

-f-/ :

СО

оРГШГ

фиг 2

Авторы

Даты

1982-07-07—Публикация

1980-12-05—Подача