ты памяти и согласования подключены к источнику питания, а опорный элемент - к шине нулевого потенциала. Элементы источников тока выполнены на транзисторах, коллекторы которых подключены к соответствующим адресным шинам другой группы, эмиттеры транзисторов подключены к шине нулевого потенциала, а базы - к точке соединения опорного элемента и дополнительного элемента памяти.

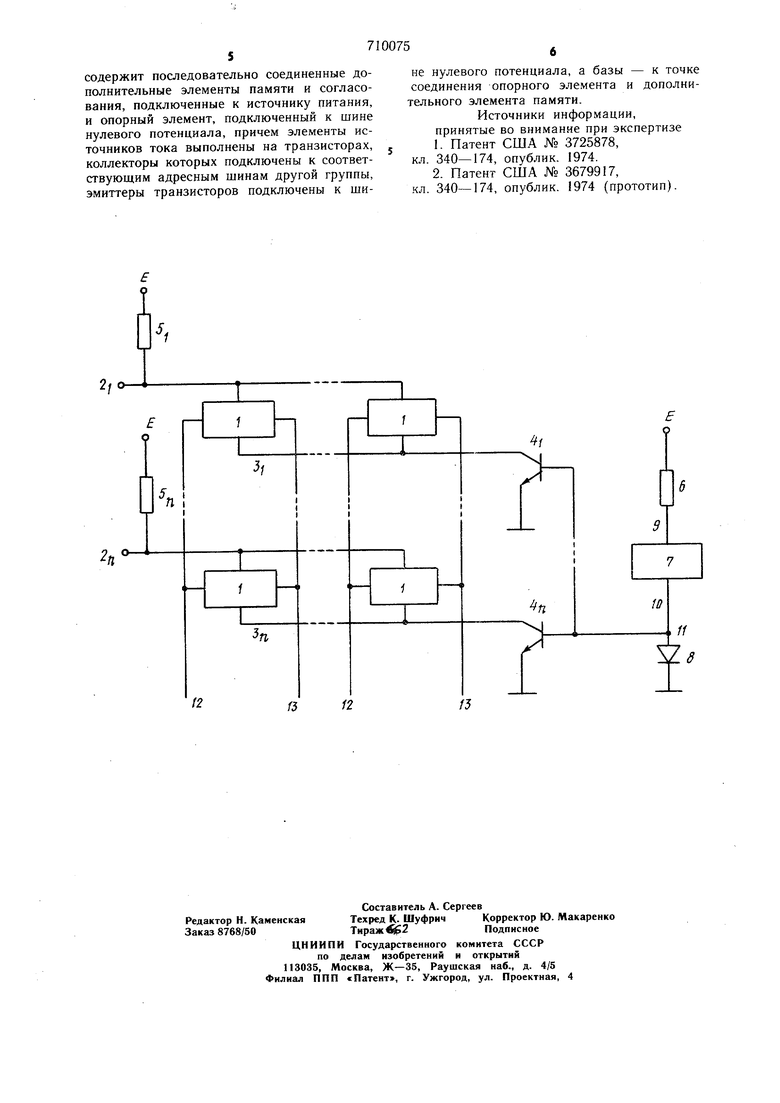

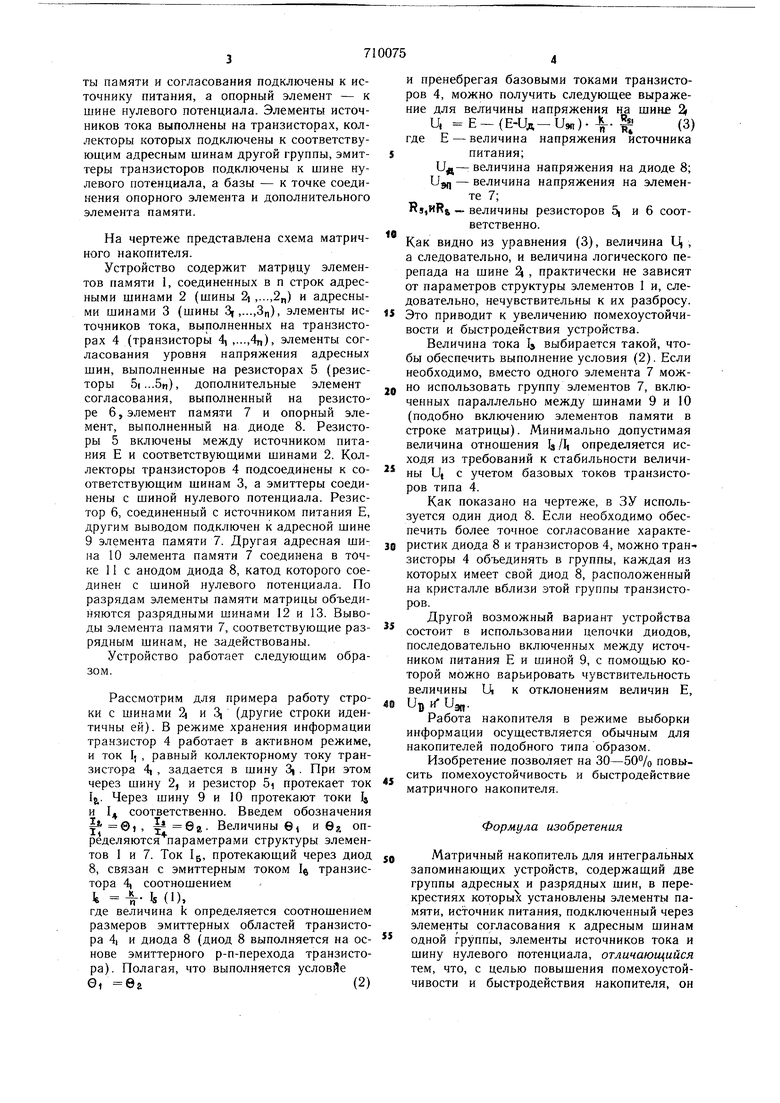

На чертеже представлена схема матричного накопителя.

Устройство содержит матрицу элементов памяти 1, соединенных в п строк адресными шинами 2 (шины 2) ,...,2„) и адресными шинами 3 (шины 3j,...,3n), элементы источников тока, выполненных на транзисторах 4 (транзисторы 4, ,...,4ц), элементы согласования уровня напряжения адресных шин, выполненные на резисторах 5 (резисторы 5|...5п), дополнительные элемент согласования, выполненный на резисторе 6,элемент памяти 7 и опорный элемент, выполненный на диоде 8. Резисторы 5 включены между источником питания Е и соответствующими шинами 2. Коллекторы транзисторов 4 подсоединены к соответствующим шинам 3, а эмиттеры соединены с шиной нулевого потенциала. Резистор 6, соединенный с источником питания Е, другим выводом подключен к адресной шине 9 элемента памяти 7. Другая адресная шина 10 элемента памяти 7 соединена в точке 1 I с анодом диода 8, катод которого соединен с шиной нулевого потенциала. По разрядам элементы памяти матрицы объединяются разрядными шинами 12 и 13. Выводы элемента памяти 7, соответствующие разрядным шинам, не задействованы.

Устройство работает следующим образом.

Рассмотрим для примера работу строки с шинами 2| и 3) (другие строки идентичны ей). В режиме хранения информации транзистор 4 работает в активном режиме, и ток Ij , равный коллекторному току транзистора 4, , задается в шину 3| . При этом через шину 2j и резистор 5i протекает ток Ij,. Через шину 9 и 10 протекают токи Jj и 1 соответственно. Введем обозначения f ©j , вг- Величины 61 и ва определяются параметрами структуры элементов 1 и 7. Ток Ig, протекаюший через диод 8, связан с эмиттерным током 1 транзистора 4, соотношением

k Is (1),

где величина k определяется соотношением размеров эмиттерных областей транзистора 4, и диода 8 (диод 8 выполняется на основе эмиттерного р-п-перехода транзистора). Полагая, что выполняется условие 01 вг(2)

и пренебрегая базовыми токами транзисторов 4, можно получить следующее выражение для величины напряжения на шине 2

Ц Е-(Е-ид-и,„).. (3)

где Е - величина напряжения источника 5питания;

величина напряжения на диоде 8;

Ujq - величина напряжения на элементе 7;

«s,fRb - величины резисторов 5| и 6 соответственно.

Как видно из уравнения (3), величина Ц, а следовательно, и величина логического перепада на щине Я , практически не зависят от параметров структуры элементов 1 и, следовательно, нечувствительны к их разбросу. Это приводит к увеличению помехоустойчивости и быстродействия устройства.

Величина тока 1з выбирается такой, чтобы обеспечить выполнение условия (2). Если необходимо, вместо одного элемента 7 можно использовать группу элементов 7, включенных параллельно между шинами 9 и 10 (подобно включению элементов памяти в строке матрицы). Минимально допустимая величина отношения Ig /I определяется исходя из требований к стабильности величн ны и, с учетом базовых токов транзисторов типа 4.

Как показано на чертеже, в ЗУ используется один диод 8. Если необходимо обеспечить более точное согласование характеристик диода 8 и транзисторов 4, можно транзисторы 4 объединять в группы, каждая из которых имеет свой диод 8, расположенный на кристалле вблизи этой группы транзисторов.

Другой возможный вариант устройства состоит в использовании цепочки диодов, последовательно включенных между источником питания Е и шиной 9, с помощью которой можно варьировать чувствительность величины Ц к отклонениям величин Е, 0 UD и UgnРабота накопителя в режиме выборки информации осуществляется обычным для накопителей подобного типа образом.

Изобретение позволяет на 30-50% повысить помехоустойчивость и быстродействие матричного накопителя.

Формула изобретения

0Матричный накопитель для интегральных

запоминающих устройств, содержащий две группы адресных и разрядных шин, в перекрестиях которых установлены элементы памяти, источник питания, подключенный через элементы согласования к адресным щинам

одной группы, элементы источников тока и шину нулевого потенциала, отличающийся тем, что, с целью повыщения помехоустойчивости и быстродействия накопителя, он

содержит последовательно соединенные дополнительные элементы памяти и согласования, подключенные к источнику питания, и опорный элемент, подключенный к шине нулевого потенциала, причем элементы источников тока выполнены на транзисторах, коллекторы которых подключены к соответствующим адресным шинам другой группы, эмиттеры транзисторов подключены к шине нулевого потенциала, а базы - к точке соединения опорного элемента и дополнительного элемента памяти.

Источники информации, принятые во внимание при экспертизе

1.Патент США № 3725878, кл. 340-174, опублик. 1974.

2.Патент США № 3679917,

кл. 340-174, опублик. 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1985 |

|

SU1256097A1 |

| Накопитель для оперативного запоминающего устройства | 1990 |

|

SU1751815A1 |

| Оперативное запоминающее устройство | 1979 |

|

SU903972A1 |

| Усилитель записи-считывания | 1986 |

|

SU1437913A1 |

| Накопитель для запоминающего устройства | 1983 |

|

SU1137537A1 |

| Запоминающее устройство | 1985 |

|

SU1305774A2 |

| Постоянное запоминающее устройство | 1982 |

|

SU1112411A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU752482A1 |

| Формирователь сигналов записи и считывания | 1983 |

|

SU1113852A1 |

| Накопитель | 1989 |

|

SU1656595A1 |

Авторы

Даты

1980-01-15—Публикация

1977-08-17—Подача