обеспечения контроля процесса преобразования. Это достигается за счет того, что процесс уравновешивания преобразуемой величины осуществляется двумя одновременно формируемыми эталонными уровнями по специальному алгоритму, а в устройство, содерж,зщее 1 енератор 1 импульсов, распределитель 2 импульсов, элемент 3 сравнения блоки 12, 15 коммутации, регистры 10, 11, введен ы логические блоки 6, 7, группы элементов И 8,9, блоки 13,14, 16,17 коммутации, преобразователи 18, 19 кода в напряжение, аналоговый вычитатель 20, блок 21 выделения модуля аналоговой величины. 4 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1270895A1 |

| Устройство преобразования амплитуды одиночного импульса | 1984 |

|

SU1241134A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1256206A1 |

| Устройство для контроля логических схем | 1986 |

|

SU1381517A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1277396A1 |

| Устройство для контроля экспоненциальных процессов | 1986 |

|

SU1310781A1 |

| Устройство для измерения уровней сигнала изображения | 1987 |

|

SU1520672A1 |

| Преобразователь перемещения в код | 1989 |

|

SU1656682A1 |

Изобретение относится к электроизмерительной и вычислительной технике- и может быть использовано для достоверного преобразования быстроизменя- юшихся во времени сигналов в цифровой код. Изобретение позволит повысить быстродействие и расширить функцио- нальные возможности устройства путем W 4i О) IND 4 фиг. f

1

Изобретение относится к электроизмерительной и вычислительной -техняке и может быть использовано для достоверного преобразования быстроизменя- гацихся во времени сигналов в цифровой код.

Цель изобретения - повышение быстродействия и расширение функцион ааь- ных возможностей путем обеспечения контроля процесса преобразования.

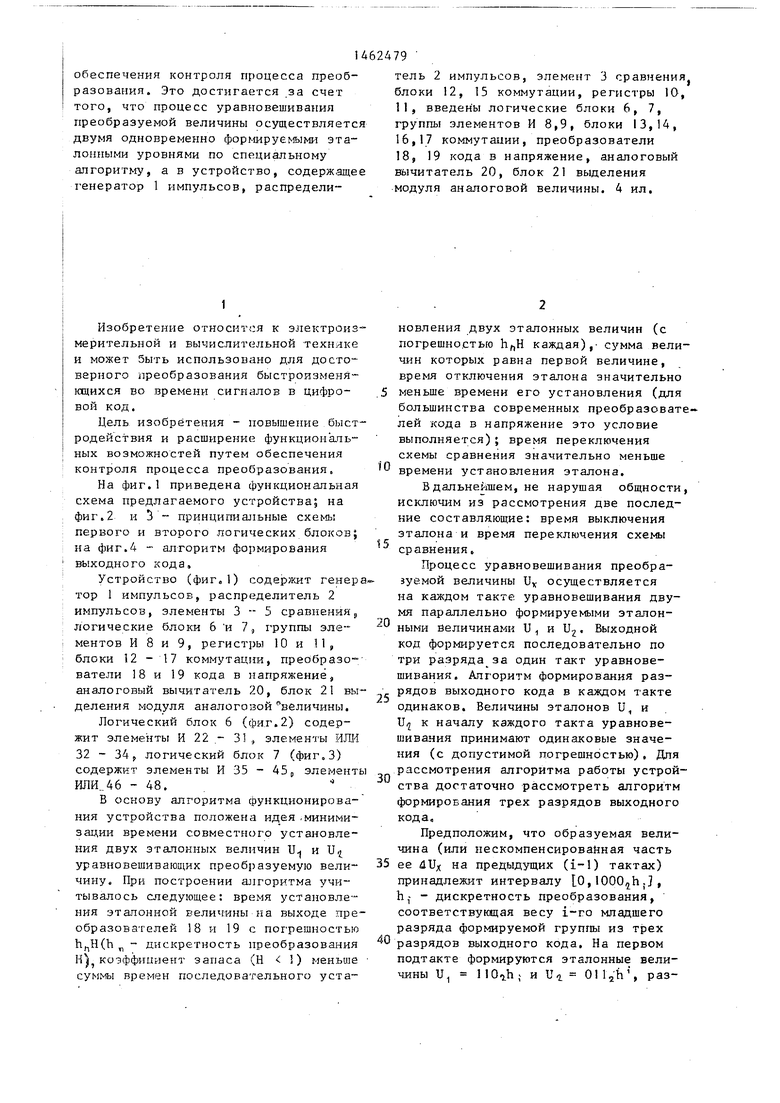

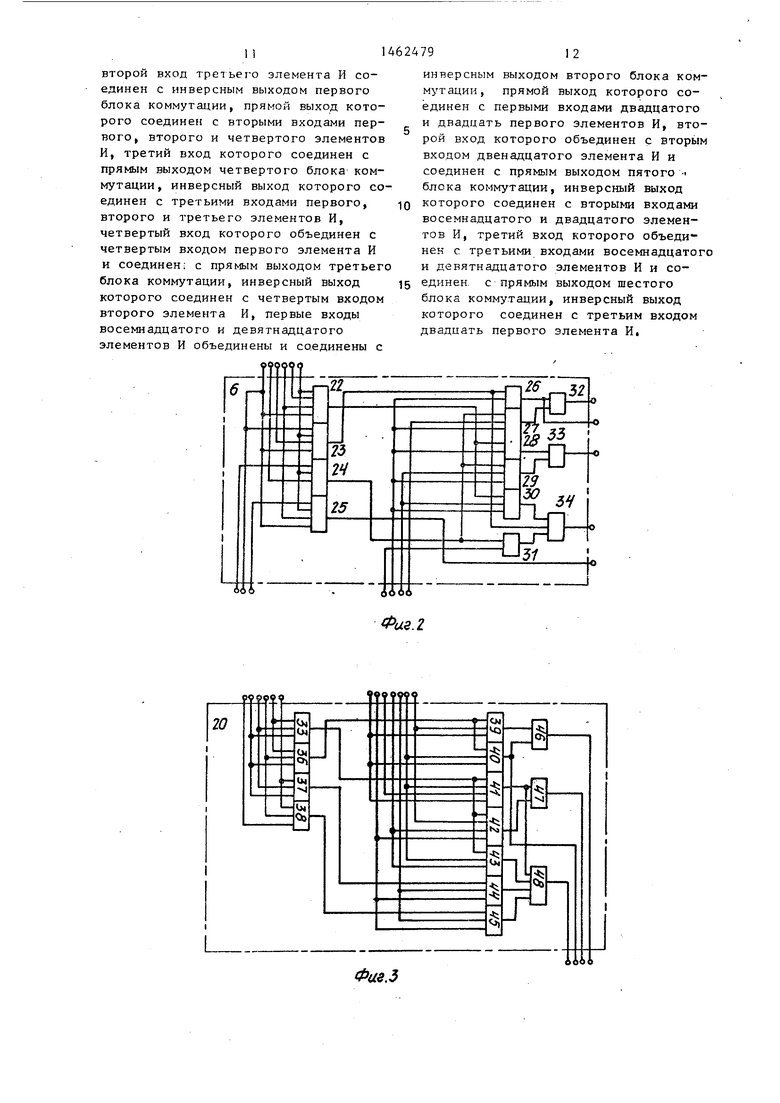

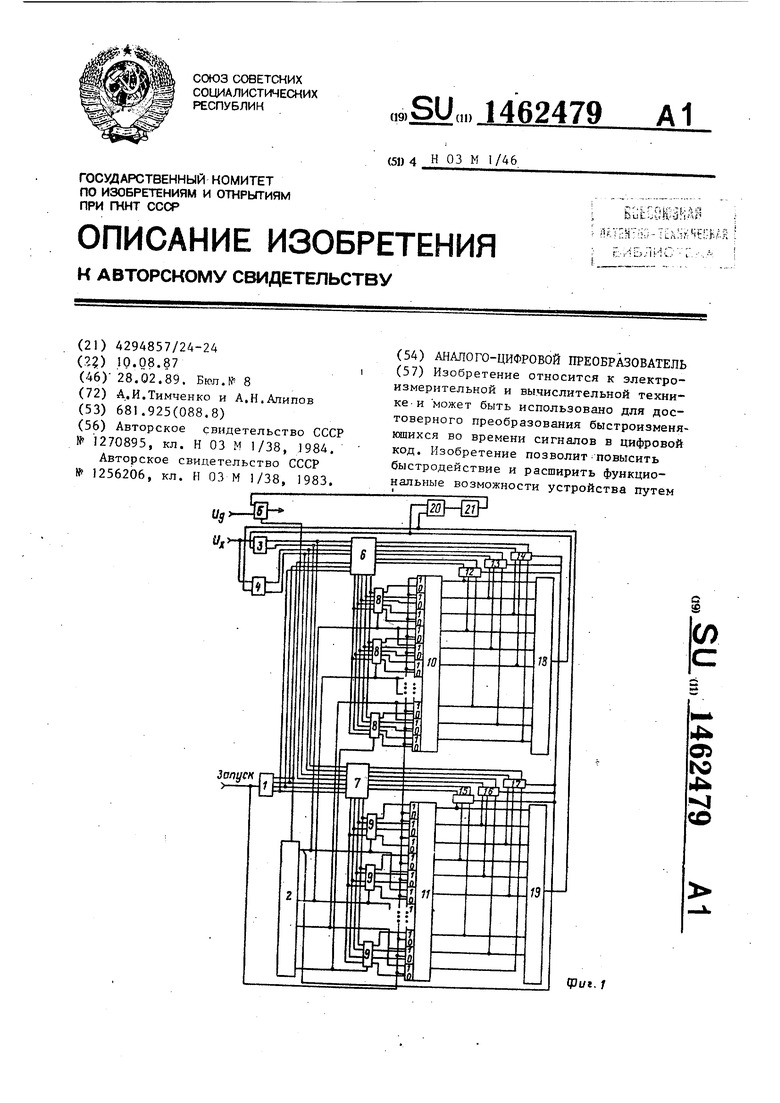

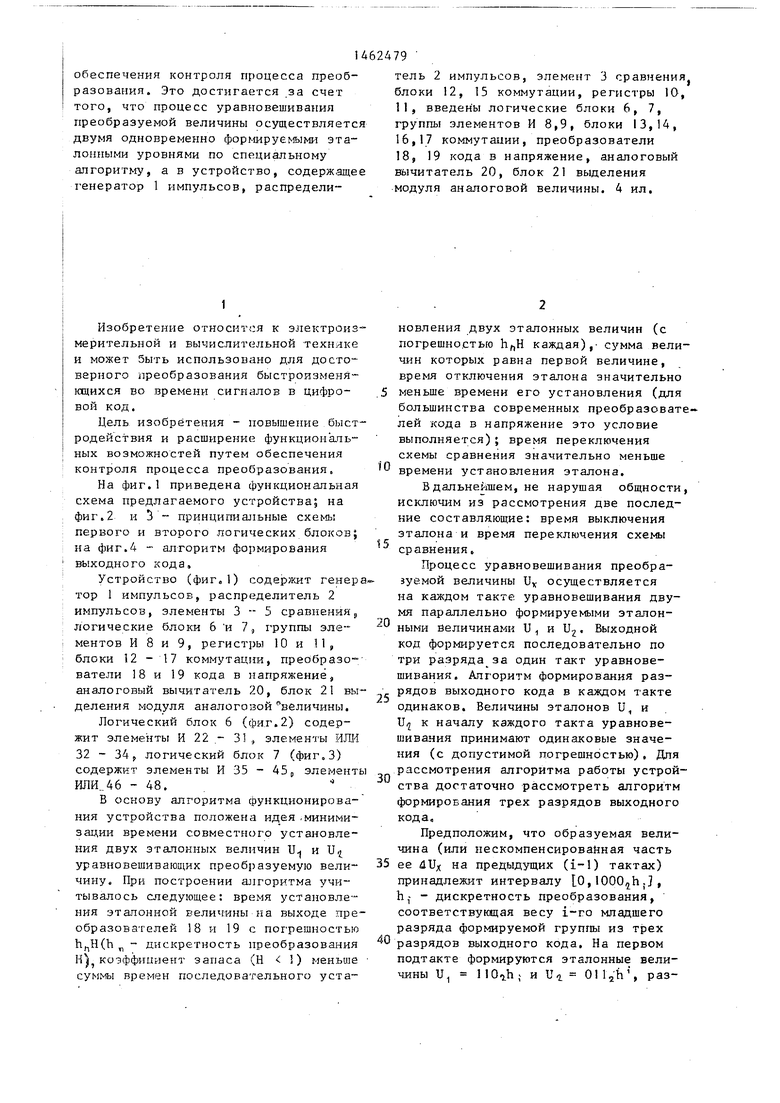

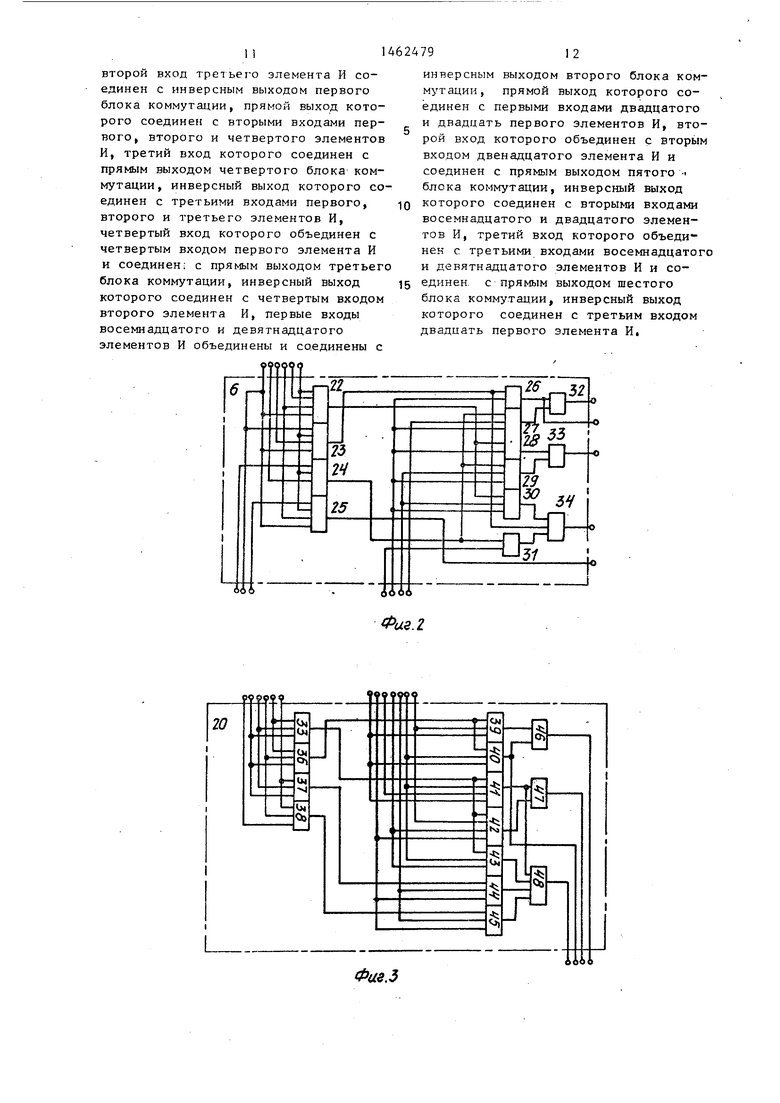

На фиг.1 приведена функциональная схема предлагаемого устройства; на фиг, 2 и 3 принципиальные cxeMia первого и второго логических блоков; на фиг.4 - алгоритм формирования выходного хода.

Устройство (фиг«1) содержит генера тор 1 импульсов, распределитель 2 импульсов, элементы 3 5 сравнения логические блоки 6 и 7, группы элементов И 8 и 9, регистры 10 и П, блоки 12 - 17 коммутации, преобразо-/ ватели 18 и 19 кода в напряжение, аналоговый вычитатель 20, блок 21 выделения модуля аналоговой величины.

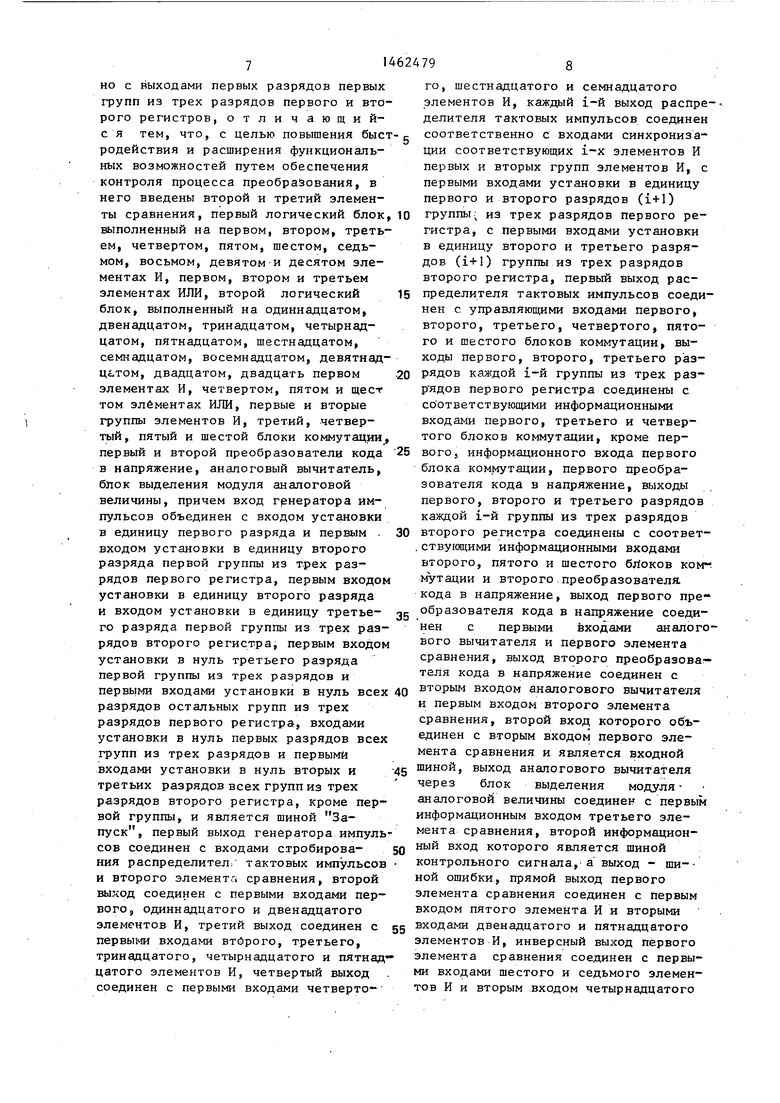

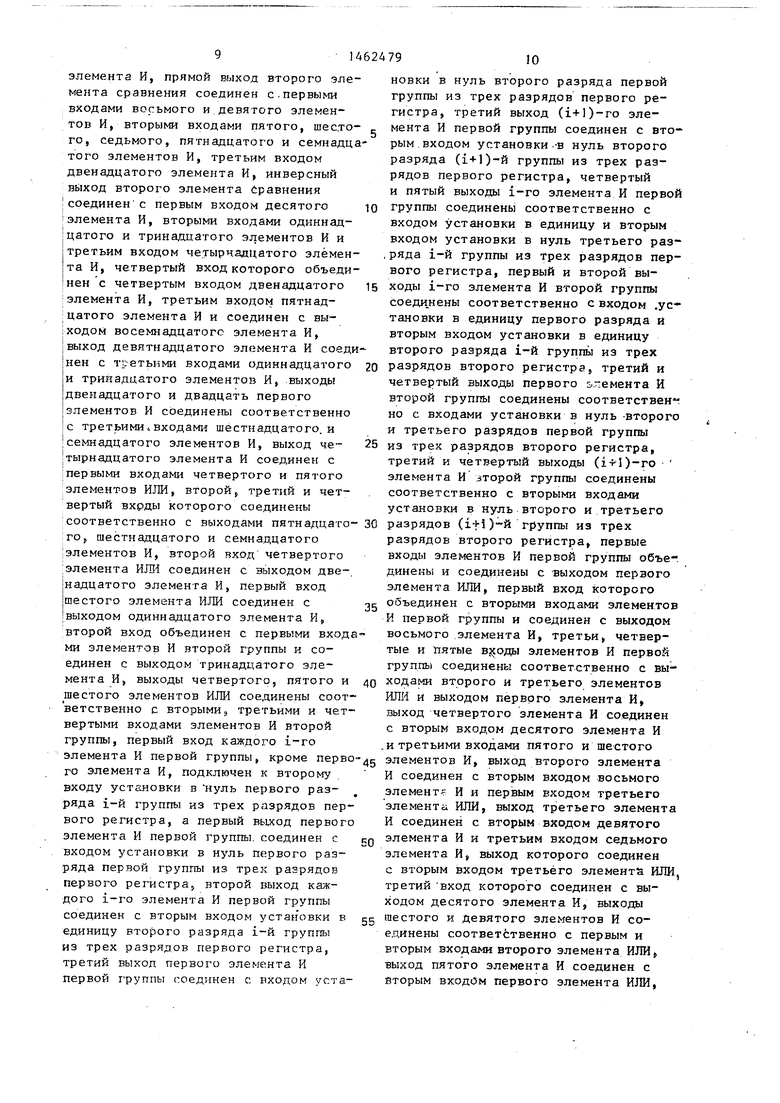

Логический блок 6 (фиг.2) содержит элементы И 22,- 3,, элементы ИЛ- 32 - 34J логический блок 7 (фиг.З) содержит элементы И 35 - 45, элементы ИЛИ.,46 - 48.

В основу алгоритма функционировакия устройства положена идея.минимизации времени совместного установления двух эталонных величин U и U,j уравновешивающих преобразуемую величину. При построении алгоритма учитывалось следующее: время установления эталонной величины на выходе преобразователей 18 и 19 с погрешностью hf,H(h - дискретность преобразова 4ия Н), коэффициент запаса (Н ) меньше cyhiNfbi времен последовательного уста

5

0

5

0

5

0

новления двух эталонных величин (с погрешностью каждая),- сумма величин которых равна первой величине, время отключения эталона значительно меньше времени его установления (для большинства современных преобразователей кода в напряжение это условие выполняется); время переключения схемы сравнения значительно меньше времени установления эталона.

В дальнейшем, не нарушая общности, исключим из рассмотрения две последние составляющие: время выключения эталона и время переключения схемы сравнения,

Процесс уравновешивания преобразуемой величины Ux осуществляется на каждом такте уравновешивания двумя параллельно формируемыми эталонными величинами U и U. Выходной код формируется последовательно по три разряда за один такт уравновешивания. Алгоритм формирования разрядов выходного кода в каждом такте одинаков. Величины эталонов U, и к началу каждого такта уравновешивания принимают одинаковые значения (с допустимой погрешностью), Для рассмотрения алгоритма работы устройства достаточно рассмотреть алгоритм формирования трех разрядов выходного кода.

Предположим, что образуемая величина (или нескомпенсировайная часть ее dUx на предыдущих (i-1) тактах) принадлежит интервалу ., h,- - дискретность преобразования, соответствугацая весу i-ro младшего разряда формируемой группы из трех разрядов выходного кода. На первом подтакте формируются эталонные величины и и U-2. Ollsh , разбивающие интервал О, ,-) на три новых интервала: О.) ,-, ,.), llO-ih;, ,-) (в дальнейшем при записи интервалов для наглядности сомножитель h будем опускать). Принадлежность преобразуемой величины и одному из выделенных интервалов определяется по состоянию двух элементов сравнения. Они выраба- ю тывают на своих выходах сигналы К ,

вом случае обе эталонные величины и, и и принимают значение Olljh,,

втором случае - значение 101

г

1Сг;

и Kj . Причем К i(,j, 1 , если U , U)( и К, (2) О - в противном случае

В том случае, когда Uy е( 1 10 lOOOi), то-для заключения U в интер-15 вал длины h( достаточно сформировать один эталон U. lll-jh,- и сравнить его с U), с тем, чтобы определить принадлежность преобразуемой величины одному из интервалов: Г ПО-,, ПЦ), 20

причем эталонная величина U, устава ливается в это значение с допустимо погрешностью гораздо раньше, чем U Поэтому в третьем подтакте U, lOl сравнивается с Ux и по результату сравнения обе эталонные величины пр нимают значение ,-, если К i и lOlih ,, если К , 0.

. -- ПО,,, 1Ц 1ПЦ, ШОО,). Вторая эталонная величина- в этом случае в уравновешивании не участвует, а сразу устанавливается в состояние U-j (из состояния 01 ЦЬ;), так как для ее 25

установления в это состояние -требуется время, определяемое временем установления старшего разряда в формируемой группе из.трех разрядов выходного кода. При этом по результату сравнения на следующем подтакте тадшие разряды двух эталонов могу,т быть выключены, если К 1.

Для случая, когда U eLOOO, ОПг) в уравновешивании принимают участие две эталонные величины. При этом формируются новые значения и, . и и т 00 ЦЬ;. Такие переходы соответствуют только выключению старшего разряда для эталона и, и второго разряда эталона U, для формируемой группы из трех разрядов выходного кода. По результатам срав- нения эталонной величины U, и U принимают одно и тй же значение из допустимой для данного диапазона: 000,

Устройство работает следующим образом.

Импульс начальной установки, поступающий по шине Запуск устанавливает в единичное состояние первый второй и третий разряды соответстве но регистров 10 и I, все остальные разряды этих регистров обнуляются-. При этом разрешается прохождение импульсов с генератора 1 на распреде литель 2 и на логические блоки 6 и 7. .

На первом выходе распределителя 2 устанавливается разрешающий сигнал с приходом импульса fp с первого выхода генератора 1, На прямых выходах 30 блоков 12 - 14 устанавливается комбинация сигналов ABC (ПО),а на их инверсных выходах - комбинация (ABC (001); на прямых выходах блоков 15 - - 17 устанавливается комбинация DEF 35 (011)5 а на их инверсных выходах - комбинация DEF (100),- При этом на выходах преобразователей 18 и 19 вырабатываются эталонные величины и, 6h,- (. ) и U,j ЗЬ;-(01ЦЬ;) 40 Они сравниваются с преобразуемой

величиной Ux элементами 3 и 4, которые вырабатывают сигналы К ,и К

на

Если к О и К О

00

Ч

010,

в последнем случае, когда U etOlk 110), преяще всего необходимо определить будет ли включен старший эталон в группе из т;.:ех разрядов дЛя на iiTopoM подтакте

Uj. Для этого

величина U принимает зна- (этот переход соответ-г/гЬ,

своих выходах, Если К О и . .(комбинация ), то это означает,

45 что Uye(6,8) (110 ,1000). Тогда

согласно алгоритму (фиг,4) с приходом импульса iJ, младший разряд группы.из трех разрядов регистра 10 через элементы 25, 31 и 34 и блок 8 установитSQ ся в единичное состояние, в группе из трех разрядов будет сформирована комбинация ABC (111),, одновременно в единичное состояние установится старший разряд в группе из трех разэталонная

чение 100

также только выключению второ- 55 регистра 1 1 и через элементы

го ра..ряда группы) -и сравнивается с36, 39 и 46 и блок 9 будет сформирои. По результату сравнения опреде-вана комбинация DEF (111), Импульс С,

ляется: UxetOIl-;, 100) (К, 1)не изменит состояния разрядов группы

или ,j,, 110) (к 1 0), В пер-из трех разрядов регистров 10, II.

вом случае обе эталонные величины и, и и принимают значение Olljh,,

втором случае - значение 101

г

причем эталонная величина U, уставав- ливается в это значение с допустимой погрешностью гораздо раньше, чем U , Поэтому в третьем подтакте U, lOlh сравнивается с Ux и по результату сравнения обе эталонные величины при нимают значение ,-, если К i и lOlih ,, если К , 0.

15 20

25

я

Устройство работает следующим образом.

Импульс начальной установки, поступающий по шине Запуск устанавливает в единичное состояние первый, второй и третий разряды соответственно регистров 10 и I, все остальные разряды этих регистров обнуляются-. При этом разрешается прохождение импульсов с генератора 1 на распреде- литель 2 и на логические блоки 6 и 7. .

На первом выходе распределителя 2 устанавливается разрешающий сигнал с приходом импульса fp с первого выхода генератора 1, На прямых выходах 30 блоков 12 - 14 устанавливается комбинация сигналов ABC (ПО),а на их инверсных выходах - комбинация (ABC (001); на прямых выходах блоков 15 - - 17 устанавливается комбинация DEF 35 (011)5 а на их инверсных выходах - комбинация DEF (100),- При этом на выходах преобразователей 18 и 19 вырабатываются эталонные величины и, 6h,- (. ) и U,j ЗЬ;-(01ЦЬ;). 40 Они сравниваются с преобразуемой

величиной Ux элементами 3 и 4, которые вырабатывают сигналы К ,и К

на

Если к О и К О

своих выходах, Если К О и . .(комбинация ), то это означает,

45 что Uye(6,8) (110 ,1000). Тогда

согласно алгоритму (фиг,4) с приходом импульса iJ, младший разряд группы.из трех разрядов регистра 10 через элементы 25, 31 и 34 и блок 8 установитQ ся в единичное состояние, в группе из трех разрядов будет сформирована комбинация ABC (111),, одновременно в единичное состояние установится старший разряд в группе из трех раз5 регистра 1 1 и через элементы

; Если на выходе элемента 13 к моменту прихода импульса з сформируется сигнал К О, то группы из трех разрядов регистров 10, 11 состояния не изменят. Если же К , 1, то будут выключены младшие разряды в этих группах через элементы 24, 27, 44 и 48. В группах из трех разрядов регистров 6 и 7 будут сформированы коды.ABC (110) и DEF (110).

В том случае, когда до прихода импульса С на выходах элементов 3,4 присутствуют сигналы К 1 и К О, то это означает принадлежность U,f подинтервалу 1.3,6) (01 Ij, 110)). С приходом импульса С., через элементы 25, 30, 33 и блок 9 в нулевое состояние установится второй разряд ф.ормируемой группы из трех разрядов регистра 6, в ней будет сформирована комбинация ABC (100), группа из трех разрядов регистра 11 состояния не изменит. По сигналу. (

надлежит подинтервалу 0,3)Г002,, 01 Ц)). С приходом импульса f, в группе из трех разрядов регистра 10 старший разряд устанавливается в нулевое состояние через элементы 25, 27 и 32, а в группе из трех разрядов регистра.П в нулевое состояние устанавливается второй разряд через эле10 менты 36 и 40. В группах из трех разрядов устанавливаются комбинации ABC (010) и DEF (001). По,импульсу С в группах из трех разрядов устанавливается комбинация 000, если

15 Kj О, при этом второй разряд в первой группе из трех разрядов включается через элементы 22, 28 и 33, а третий разряд во второй - через элементы 35, 4 и 47. Когда К ., 1 и

20

К,

О, то по импульсу t разряды

-2

второй группы из трех разрядов состояния не изменят, а в первой группе из трех разрядов выключится второй разряд через элементы 22, 29 и 33

если к этому моменту V. 1, состоя- 25 и выключается младший разряд через ние разрядов группы из трех разрядов элементы 22, 30 и 34. Если же К, регистра 11 не изменяется, а в группе - импульс 2,, не изменяет состоя- из трех разрядов регистра 10 выключит- иия разрядов первой группы из трех ся старший разряд через элементы разрядов, во второй группе из трех 23, 26 и 32 и блок 8, второй и третий 30 разрядов включается второй разряд разряды этой группы из трех разрядов через элементы 35, 41 и 47 и выклю- устанавливаются в единичное состояние через элементы 23, 26, 4, 23 и 34„ а

также блок 8. В группе из трех раз- рядов регистров 10 и 11 установится комбинация ABC (Oil) и DEF (Oil), При этом третий импульс з состояния группы из грех разрядов регистров . 10 и 11 не изменит.

Для случая, когда К., О, с приходом импульса группах из трех разрядов регистров 10 и 11 устанавливается комбинация ABC, DEF (101), Младший разряд группы из трех разрядов регистра 10 включается через элементы 23 и 34, старший разряд группы из трех разрядов регистра 11 включается через элементы 36, 40 и 46, второй разряд этой же Группы

35

чается третий разряд через элементы 35, 41 и 48.

Сигналы с выходов преобразователей 18 и 19 поступают на вход аналогового вычитателя 20, который формирует их разность. Далее сигнал поступает на вход блока 21. Последний формирует сигнал ошибки X, который элементом 5

4Q сравнивается с допустимой Uq. В том случае, когда сигнал на выходе блока 21 превышает 11, то на выходе элемента 5 с приходом импульса Dp вырабатывается сигнал ошибки. По появлению

4g этого сигнала можно судить о возникновении сбоев, отказов в работе устройства, а также о превышении инструментальных погрешностей допустимого уровня в процессе эксплуатации уствыключается через элемен.ты 36 и 40. 50 .

Формула изобретения Аналого-цифровой преобразователь.

Импульс (. з не изменит состояния разрядов групп из трех разрядов регистров 10 и 11, когда К О, если же К 1, то выключаются младшие разряды в этих группах из трех раз- 55 °Д Ржащий генератор импульсов, рас- рядов соответственно через элементы пределитель импульсов, первый эле- 24 и элементы 37, 44 и 48.мент сравнения, первый и второй блоки

В том случае, когда до прихода коммутации, первые информационные импульса i, К , К л , то U при- входы которых соединены соответствен624796

надлежит подинтервалу 0,3)Г002,, 01 Ц)). С приходом импульса f, в группе из трех разрядов регистра 10 старший разряд устанавливается в нулевое состояние через элементы 25, 27 и 32, а в группе из трех разрядов регистра.П в нулевое состояние устанавливается второй разряд через эле10 менты 36 и 40. В группах из трех разрядов устанавливаются комбинации ABC (010) и DEF (001). По,импульсу С в группах из трех разрядов устанавливается комбинация 000, если

15 Kj О, при этом второй разряд в первой группе из трех разрядов включается через элементы 22, 28 и 33, а третий разряд во второй - через элементы 35, 4 и 47. Когда К ., 1 и

20

К,

О, то по импульсу t разряды

второй группы из трех разрядов состояния не изменят, а в первой группе из трех разрядов выключится второй разряд через элементы 22, 29 и 33

и выключается младший разряд через элементы 22, 30 и 34. Если же К, - импульс 2,, не изменяет состоя- иия разрядов первой группы из трех разрядов, во второй группе из трех разрядов включается второй разряд через элементы 35, 41 и 47 и выклю-

чается третий разряд через элементы 35, 41 и 48.

Сигналы с выходов преобразователей 18 и 19 поступают на вход аналогового вычитателя 20, который формирует их разность. Далее сигнал поступает на вход блока 21. Последний формирует сигнал ошибки X, который элементом 5

сравнивается с допустимой Uq. В том случае, когда сигнал на выходе блока 21 превышает 11, то на выходе элемента 5 с приходом импульса Dp вырабатывается сигнал ошибки. По появлению

этого сигнала можно судить о возникновении сбоев, отказов в работе устройства, а также о превышении инструментальных погрешностей допустимого уровня в процессе эксплуатации устФормула изобретения Аналого-цифровой преобразователь.

°Д Ржащий генератор импульсов, рас- пределитель импульсов, первый эле- мент сравнения, первый и второй блоки

но с выходами первых разрядов первых групп из трех разрядов первого и второго регистров, отли чающийся тем, что, с целью повышения быст родействия и расширения функциональных возможностей путем обеспечения контроля процесса преобразования, в него введены второй и третий элементы сравнения, первый логический блок выполненный на первом, втором, третьем, четвертом, пятом, шестом, седьмом, восьмом, девятом и десятом элементах И, первом, втором и третьем элементах ИЛИ, второй логический

блок, выполненный на одиннадцатом, двенадцатом, тринадцатом, четырнадцатом, пятнадцатом, шестнадцатом, семнадцатом, восемнадцатом, девятнадцатом, двадцатом, двадцать первом элементах И, четвертом, пятом и щест том элементах ИЛИ, первые и вторые группы элементов И, третий, .четвертый, пятый и шестой блоки коммутации, первый и второй преобразователи кода в напряжение, аналоговый вычитатель, блок выделения модуля аналоговой величины, причем вход генератора импульсов объединен с входом установки в единицу первого разряда и первым . входом установки в единицу второго разряда первой группы из трех разрядов первого регистра, первым входом установки в единицу второго разряда и входом установки в единицу третье- го разряда первой группы из трех разрядов второго регистра, первым входом установки в нуль третьего разряда первой группы из трех разрядов и первыми входами установки в нуль всех разрядов остальных групп из трех разрядов первого регистра, входами установки в нуль первых разрядов всех групп из трех разрядов и первыми входами установки в нуль вторых и третьих разрядов всех групп из трех разрядов второго регистра, кроме первой группы, и является шиной Запуск, первый выход генератора импульсов соединен с входами стробирова- НИН распределител; тактовых импульсов и второго элемента сравнения, второй выход соединен с первыми входами первого, одиннадцатого и двенадцатого элементов И, третий выход соединен с первы1чи входами втйрого, третьего, тринадцатого, четырнадцатого и пятнад цатого элементов И, четвертый выход соединен с первыми входами четверто-

го, шестнадцатого и семнадцатого элементов И, каждый i-й выход распределителя тактовых импульсов соединен соответственно с входами синхронизации соответствуюших i-x элементов И первых и вторых групп элементов И, с первыми входами установки в единицу первого и второго разрядов (i+1) группы: из трех разрядов первого регистра, с первыми входами установки в единицу второго и третьего разрядов (i+1) группы из трех разрядов второго регистра, первый выход распределителя тактовых импульсов соединен с управляющими входами первого, второго, третьего, четвертого, пятого и шестого блоков коммутации, выходы первого, второго, третьего pias- рядов каждой i-й группы из трех раз- р ядов первого регистра соединены с соответствующими информационными входами первого, третьего и четвертого блоков коммутации, кроме первого, информационного входа первого блока ком,мутации, первого преобразователя кода в напряжение, первого, второго и третьего разрядов каждой i-й группы из трех разрядов второго регистра соединены с соответ . ствукнцими информационными входами второго, пятого и шестого блоков ком мутации и второго.преобразователя кода в напряжение, выход первого преобразователя кода в напряжение соединен с первыми входами аналогового вычитателя и первого элемента сравнения, выход второго преобразоваг теля кода в напряжение соединен с вторым входом аналогового вычитателя и первым входом второго элемента сравнения, второй вход которого объединен с вторым входом первого элемента сравнения и является входной шиной, выход аналогового вычитателя через блок выделения модуля аналоговой величины соединен с первым информационным входом третьего элемента сравнения, второй информационный вход которого является шиной контрольного сигнала, а выход - ши- ной ошибки, прямой выход первого элемента сравнения соединен с первым входом пятого элемента И и вторыми входами двенадцатого и пятнадцатого элементов И, инверсный выход первого элемента сравнения соединен с первыми входами шестого и седьмого элементов И и вторым входом четырнадцатого

элемента И, прямой выход второго элемента сравнения соединен с.первыми входами восьмого и девятого элементов И, вторыми входами пятого, шестого, седьмого, пятнадцатого и семнадцатого элементов И, третьим входом двенадцатого элемента И, инверсный выход второго элемента Сравнения I соединен с первым входом десятого ю I элемента И, вторыми входами одинндд- |цатого и тринадцатого элементов И и третьим входом четырнадцатого элемента И, четвертый вход которого объеди- : нен с четвертым входом двенадцатого 15 :элемента И, третьим входом пятнад- :цатого элемента И и соединен с вы- Iходом восемнадцатого элемента И, I выход девятнадцатого элемента И соеди- 1нен с третьими входами одиннадцатого 20 и тринадцатого элементов И, выходы двенадцатого и двадцать первого Iэлементов И соединены соответственно |с третьими входами шестнадцатого, и семнадцатого элементов И, выход че- 25 :тырнадцатого элемента И соединен с ;первыми входами четвертого и пятого элементов ШШ, второй, третий и четвертый вхрды которого соединены соответственно с выходами пятнадцато- 30 го, шестнадцатого и семнадцатого ;элементов И, второй вход четвертого ;элемента ИЛИ соединен с выходом две- |надцатого элемента И, первый вход jmecToro элемента ИЛИ соединен с Б ВЫХОДОМ одиннадцатого элемента И, второй вход объединен с первыми входами элементов И второй группы и соединен с выходом тринадцатого элемента И, выходы четвертого, пятого и 40 шестого элементов ИЛИ соединены соответственно с вторыми, третьими и четвертыми входами элементов И второй группы, первый вход каждого i-ro элемента И первой группы, кроме перво- с го элемента и, подключен к второму входу установки в нуль первого разряда i-й группы из трех разрядов первого регистра, а первый вьLxoд первого элемента И первой группы, соединен с кг входом установки в нуль первого разряда первой группы из трех разрядов первого регистра, второй выход каждого i-ro элемента И первой группы соединен с вторым входом устан овки в ее единицу второго разряда i-й группы из трех разрядов первого регистра, третий выход первого элеме-.нта И первой группы соединен с входом уста1А6247910

новки в нуль второго разряда первой группы из трех разрядов первого регистра, третий выход (1+1)-го элемента И первой группы соединен с вторым, входом установки .-в нуль второго разряда (i+l)-й группы из трех разрядов первого регистра, четвертый и пятый выходы -го элемента И первой группы соединены соответственно с входом установки в единицу и вторым входом установки в нуль третьего раз- ,ряда 1-й группы из трех разрядов первого регистра, первый и второй выходы i-ro элемента И второй группы соеди нены соответственно с входом .ус тановки в единицу первого разряда и вторым входом установки в единицу второго разряда 1-й группы из трех разрядов второго регистра, третий и четвертый выходы первого элемента И второй группы соединены соответствен г но с входами установки в нуль -второго и третьего разрядов первой группы из трех разрядов второго регистра, третий и четверть й выходы ( )-го элемента И зторой группы сое.динены соответственно с вторыми входами установки в нуль второго и третьего разрядов (ifl)й группы из трех разрядов второго регистра, первые входы элементов И первой группы объег динекы и соединены с -выходом первого элемента ИЛИ, первый вход которого объединен с вторыми входами элементов И первой группы и соединен с выходом восьмого элемента И, третьи, четвертые и Пятые элементов И первой группь соединены соответственно с вы-- ходами второго и третьего элементов ИЛИ и выходом первого элемента И, выход четвертого злемента И со.единен с вторым входом десятого элемента И .и третьими входами пятого и шестого элементов И, выход второго элемента И соединен с вторым входом восьмого элемент И и первым входом третьего элемента ИЛИ, выход третьего элемента И соединен с вторым входом девятого элемента И и третьим входом седьмого элемента И, выход которого соединен с вторым входом третьего элемента ИЛИ третий вход которого соединен с выходом десятого элемента И, выходы гаестого и девятого элементов И соединены соответственно с первым и вторым входами второго элемента ИЛИ, выход пятого элемента И соединен с вторым входом первого элемента ИЛИ,

второй вход Tpeibero элемента И соединен с инверсным выходом первого блока коммутации, прямой выход которого соединен с вторыми входами первого, второго и четвертого элементов И, третий вход которого соединен с прямым выходом четвертого блока коммутации, инверсный выход которого соединен с третьими входами первого, второго и третьего элементов И, четвертый вход которого объединен с четвертым входом первого элемента И и соединен; с прямым выходом третьег блока коммутации, инверсный выход которого соединен с четвертым входом второго элемента И, первые входы восемнадцатого и девятнадцатого элементов И объединены и соединены с

инверсным выходом второго блока коммутации, прямой выход которого соединен с первыми входами двадцатого и двадцать первого элементов И, второй вход которого объединен с вторым входом двенадцатого элемента И и соединен с прямым выходом пятого блока коммутации, инверсный выход

которого соединен с вторыми входами восемнадцатого и двадцатого элементов И, третий вход которого объединен с третьими входами восемнадцатого и девятнадцатого элементов И и соединен с прямым выходом шестого блока коммутации, инверсный выход которого соединен с третьим входом двадцать первого элемента И,

из.2

Фиг.д

| Аналого-цифровой преобразователь | 1984 |

|

SU1270895A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1256206A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-02-28—Публикация

1987-08-10—Подача