(54) ИМПУЛЬСНЫЙ РЕГУЛЯТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регулирования уровня воды на участке канала | 1990 |

|

SU1781674A1 |

| Импульсный регулятор уровня воды в канале | 1985 |

|

SU1288655A1 |

| Адаптивный импульсный регулятор для нестационарных объектов с запаздыванием | 1981 |

|

SU993207A1 |

| Устройство для регулирования уровня воды на участке канала | 1986 |

|

SU1418407A1 |

| Система экстремального регулирования | 1982 |

|

SU1068890A1 |

| Устройство для регулирования скорости двигателя | 1981 |

|

SU970331A2 |

| Многоканальный регулятор температуры | 1982 |

|

SU1091139A1 |

| Импульсный регулятор | 1983 |

|

SU1117585A1 |

| Устройство для регулирования уровня воды в канале | 1986 |

|

SU1348788A1 |

| Импульсный регулятор | 1982 |

|

SU1105859A1 |

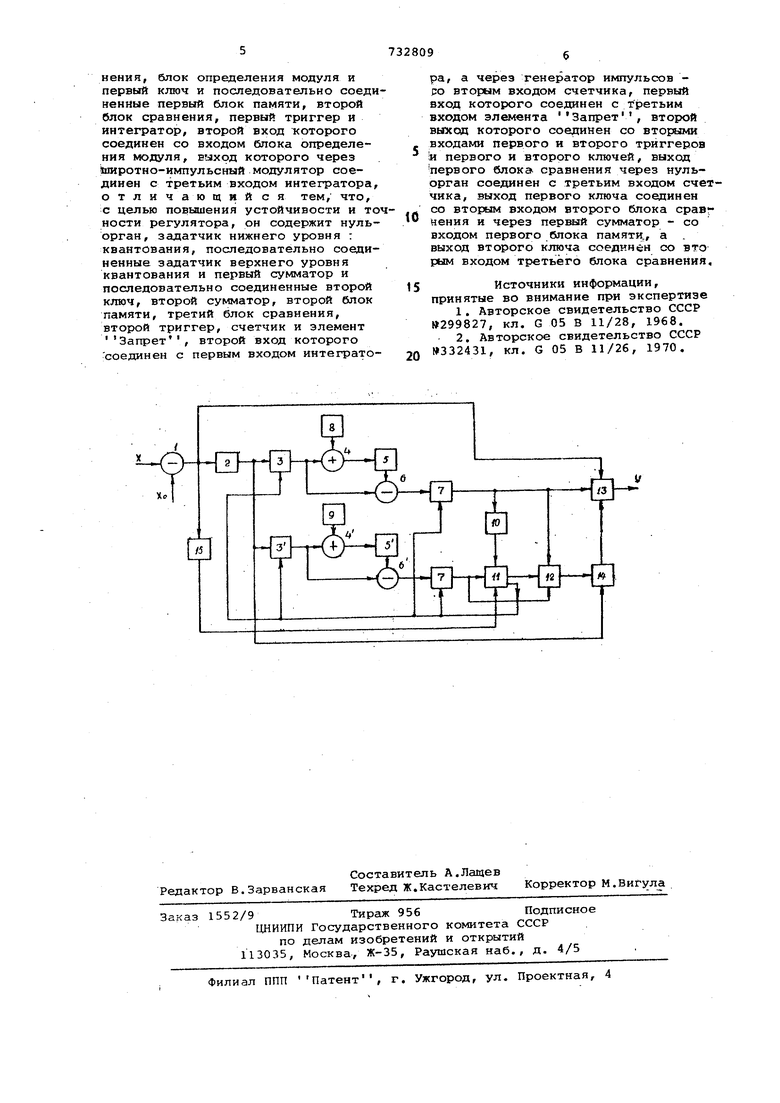

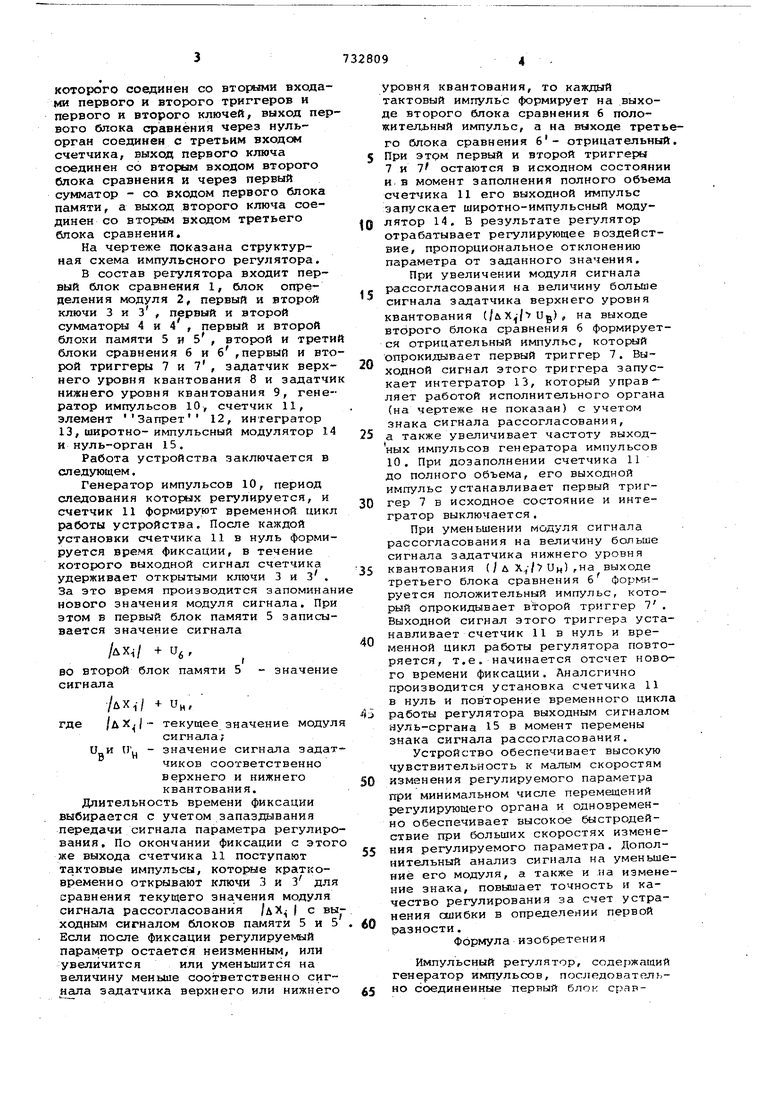

Изобретение относится к техни е автоматического регулирования объек тов, обладающих большими емкостями или распределенными параметрами в различных областях промышленности, например в объектах химической промышленности, мелиорации и др. Известны устройства импульсного автоматического регулирования объек тов, обладающих запаздыванием, содержащие блоки квантования сигнала регулируемого параметра по времени каналы выделения первой разности, широтно-импульсные модуляторы форми рования управляющего воздействия Известные устройства не обеспечи вают высокого качества регулирования для объектов с большими емкостями в широком диапазоне интенсивности возмущаемых воздействий. Наиболее близким по технической сущности к предлагаемому является импульсный регулятор, содержащий генератор импульсов, последователь но соединенные первый блок сравнения, блок определения модуля и пер ключ и последовательно соединенные первый блок памяти, второй блок сравнения, первый триггер и интегр тор, второй вход которого соединен со входом блока определения модуля, выход которого через широтно-импульсный модулятор соединен с третьим входом интегратора 2. Цель изобретения - повышение точности и устойчивости и обеспечение высокого качества регулирования, повышение над жности и достоверности технологического оборудования для объектов с большими емкостями при широком диапазоне интенсивностей возмущающих воздействий. Поставленная цель достигается тем, что регулятор содержит нульорган, задатчик нижнего УРОВНЯ квантования, последовательно соединенные задатчик верхнего уровня квантования и первый сумматор и последовательно соединенные второй ключ, второй сумматор, второй блок памяти, третий блок сравнения, второй триггер, счетчик и элемент Запрет, второй вход которого соединен с первым входом интегратора, а через генератор импульсов - со входом счетчика, первый вход которого соединен с третьим входом эл.емента Запрет, второй выход которого соединен со вторыми входа ми первого и второго триггеров и первого и второго ключей, выход пер вого езлока сравнения через нульорган соединен с третьим входом счетчика, выход первого ключа соединен со вторым входом второго блока сравнения и через первый сумматор - со входом первого блока памяти, а выход второго ключа соединен со вторым входом третьего блока сравнения. На чертеже показана структурная схема импульсного регулятора, В состав регулятора входит первый блок сравнения 1, блок определения модуля 2, первый и второй ключи 3 и з , первый и второй сумматоры 4 и 4 , первый и второй блоки памяти 5 и 5 , второй и трет блоки сравнения б и б ,первый и вт рой триггеры 7 и 7, эадатчик верх него уровня квантования 8 и задатч нижнего уровня квантования 9, гене ратор импульсов 10, счетчик 11, элемент Запрет 12, интегратор 13, широтно-импульсный модулятор 1 и нуль-орган 15. Работа устройства заключается в следующем, Генератор импульсов 10, период следования которых регулируется, и счетчик 11 формируют временной цик работы устройства. После каждой установки счетчика 11 в нуль форми руется время фиксации, в течение которого выходной сигнал счетчика удерживает открытыми ключи 3 и з . За это время производится запомина нового значения модуля сигнала. Пр этом в первый блок памяти 5 записы вается значение сигнала + и во второй блок памяти 5 - значени сигнала /uXi/ + UH, где текущее значение модул сигнала; и„и Пц - значение сигнала зада чиков соответственно верхнего и нижнего квантования. Длительность времени фиксации выбирается с учетом запаздывания передачи сигнала параметра регулир вания. По окончании фиксации с этог же выхода счетчика 11 поступают тактовые импульсы, которые кратковременно открывают ключи 3 и З для сравнения текущего значения модуля сигнала рассогласования /дХ | с вы ходным сигналом блоков памяти 5 и 5 Если после фиксации регулируемый параметр остается неизменным, или увеличится или уменьшится на величину меньше соответственно сигНсша задатчика верхнего или нижнего уровня квантования, то каждый тактовый импульс формирует на выходе второго блока сравнения 6 положительный импульс, а на выходе третьего блока сравнения 6- отрицательный. При этрм первый и второй триггеры 7 и 7 остаются в исходном состоянии и в момент заполнения полного объема счетчика 11 его выходной импульс запускает широтно-импульсный модулятор 14, В результате регулятор отрабатывает регулирующее воздействие, пропорциональное отклонению параметра от заданного значения. При увеличении модуля сигнала рассогласования на величину больше сигнала задатчика верхнего уровня квантования (/лХ;,-/ Ug) , на выходе второго блока сравнения 6 формируется отрицательный импульс, который опрокидывает первый триггер 7. Выходной сигнал этого триггера запускает интегратор 13, который управляет работой исполнительного органа {на чертеже не показан) с учетом знака сигнала рассогласования, а также увеличивает частоту выходных импульсов генератора импульсов 10, При дозаполнении счетчика 11 до полного объема, его выходной импульс устанавливает первый триггер 7 в исходное состояние и интегратор выключается, При уменьшении модуля сигнала рассогласования на величину больше сигнала задатчика нижнего уровня квантования (/д Ху/ Оц) ,на выходе третьего блока сравнения б формируется положительный импульс, который опрокидывает второй триггер Т , Выходной сигнал этого триггера устанавливает счетчик 11 в нуль и временной цикл работы регулятора повторяется, т,е, начинается отсчет нового времени фиксации. Аналогично производится установка счетчика 11 в нуль и повторение временного цикла работы регулятора выходным сигналом яуль-сргана 15 в момент перемены знака сигнала рассогласования. Устройство обеспечивает высокую чувствительность к мешым скоростям изменения регулируемого параметра при минимальном числе перемещений регулирующего органа и одновременно обеспечивает высокое быстродействие при больших скоростях изменения регулируемого параметра. Дополнительный анализ сигнала на уменьшение его модуля, а также и на изменение знака, повышает точность и качество регулирования за счет устранения сшибки в определении первой разности. Формула изобретения Импульсный регулятор, содержащий генератор импульсов, последовател.ьно соединенные первый блок срарнения, блок определения модуля и первый ключ и последовательно соединенные первый блок памяти, второй блок сравнения, первый триггер и интегратор, второй вход которого соединен со входом блока определения модуля, выход которого через Ьшротно-импульсный модулятор соединен с третьим входом интегратора, отличающийся тем, что, с целью повышения устойчивости и тоности регулятора, он содержит нульорган, задатчик нижнего уровня : квантования, последовательно соединенные задатчик верхнего уровня квантования и первый сумматор и последовательно соединенные второй ключ, второй сумматор, второй блок памяти, третий блок сравнения, второй триггер, счетчик и элемент Запрет, второй вход которого соединен с первым входом интегратора, а через генератор импульсов ро вторым входом счетчика, первый вход которого соединен с третьим входом элемента Запрет, второй выход которого соединен со вторыми ,. входами первого и второго триггеров и первого и второго ключей, выход первого блок сравнения через нульОРган соединен с третьим входом счетчика, выход первого ключа соединен .. со вторым входом второго блока сравйения и через первый сумматор - со входом первого блока памяти, а выход второго ключа соединен со вто рым входом третьего блока сравнения,

5Источники информации,

принятые во внимание при экспертизе

2,Авторское свидетельство СССР 0 №332431, кл. G 05 В 11/26, 1970.

Авторы

Даты

1980-05-05—Публикация

1977-10-14—Подача