содержит Re-триггер, последовательно соединенные элементы И и ИЛИ и последовательно соединенные первый ключ, интегратор и второй ключ, управлякщим входом подключенный к четвертому управлянмцему входу блока памяти, а выходом - к сигнальному выходу блока памятиt сигнальный вход которого подключен к сигнальному входу первого ключа, управляющим входом подключенного к первому входу элемента И и к прямому выходу RS-триггера R-входом подключенного к первому управляющему входу блока памяти, а инверсным выходом - к информационному выходу блока памяти, пятым управляющим входом подключенного к первому Iвходу элемента ИЛИ, -а вторым управляющим входом - ко второму входу элемента И, выходом подключенного ко второму входу элемента ИЛИ, выходом подключенного к управляющему входу интегратора.

3. Регулятор по т. 1 и2, отличающийся тем, что широтно-импульсньм-модулятор содержит элемент ИЛИ, первый и второй RS -триггеры и последовательно соединенные сумматор, интегратор и релейный элемент, выходом соединенный с R -входами первого и второго RS -триггеров и с вторым информационным выходом широтно-импульсного модулятора, первым и вторым сигнальным входами соединенного с 5 -входами RS -триггеров, первым и вторым управляющими входами - с вторым и третьим входами сумматора, первым информационным выходом - с выходом элемента ИЛИ, первым входом сумматора и управляющим входом интегратора.

а первым и вторым сиг- нальными выходами - с выходами соответственно первого и второго RJ-триггеров и с первым и вторьш входами элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсный регулятор | 1983 |

|

SU1117585A1 |

| Импульсный регулятор | 1984 |

|

SU1238025A1 |

| Импульсный регулятор | 1982 |

|

SU1101787A1 |

| Импульсный регулятор | 1984 |

|

SU1251025A1 |

| Частотно-импульсный регулятор | 1985 |

|

SU1278806A1 |

| Импульсный регулятор | 1984 |

|

SU1170426A1 |

| Импульсно-релейный регулятор | 1984 |

|

SU1228072A1 |

| Частотно-импульсный регулятор | 1984 |

|

SU1238028A1 |

| Компенсационно-параметрический импульсный стабилизатор постоянного напряжения | 1987 |

|

SU1437845A1 |

| Частотно-импульсный регулятор | 1987 |

|

SU1444709A1 |

1. ИМПУЛЬСНЫЙ РЕГУЛЯТОР, содержащий первьм и второй усилители мощности, выходами подключенные к первому и второму входам исполнительного механизма, первый, второй и третий одновибраторы и последовательно соединенные предварительный усилитель и интегратор, управляющим входом подключенный к выходу первого одновибратора, а выходом - ко входам первого и второго релейных блоков, отличающийся тем, что, с целью повышения точности регулятора, в нем дополнительно установлены третий, и четвертый релейные блоки, первый, второй и третий элементы И, R5 триггер, первьй и второй блоки , счетчик импульсови ииротно-импульсный модулятор, первым и вторым тактовьми входами подключенный к выходам соответственно первого и второго дэелейных блоков, первым и вторым управляющими входами - к сигнальным выходам соответственно первого и второго блоков памяти, первым и вторым сигнальными выходами - ко входам соответственно первого и второго усилителей мощности, первым информационным выходом - к выходу первого одновибратора и первому входу первого элемента И, а вторым информационным выходом - к первому входу второго элемента И, выход усилителя подключен к сигнальным входам первого и второго блоков памяти, через последовательно соединенные третий релейный блок и второй одновибратор - к первому входу третьего элемента И, а 9 через последовательно соединенные четвертый релейный блок и третий одновибратор - к первому управляющему с входу первого блока и к 5-входу Р5-триггера, выходом подключенного ко второму входу третьего элемента И, выходом подключенного к первому управлякнцему входу второго блока памяти, выход первого одновибратора подключен ко вторым управляющим входам пер 01 вого и второго блоков памяти, а через 00 ел счетчик импульсов - к третьим управj-ляющим входам первого и второго бло ков памяти и к R -входу R5 -триггера, информационный выход первого блоКа памяти подключен ко вторым входам первого и второго элементов И, информационный выход второго блока памяти подключен к третьим входам первого и второго элементов И, выходы которых подключены соответственно к четвертым и пятым входам первого и второго блоков памяти. 2. Регулятор по п. 1, отличающийся тем, что блок памяти

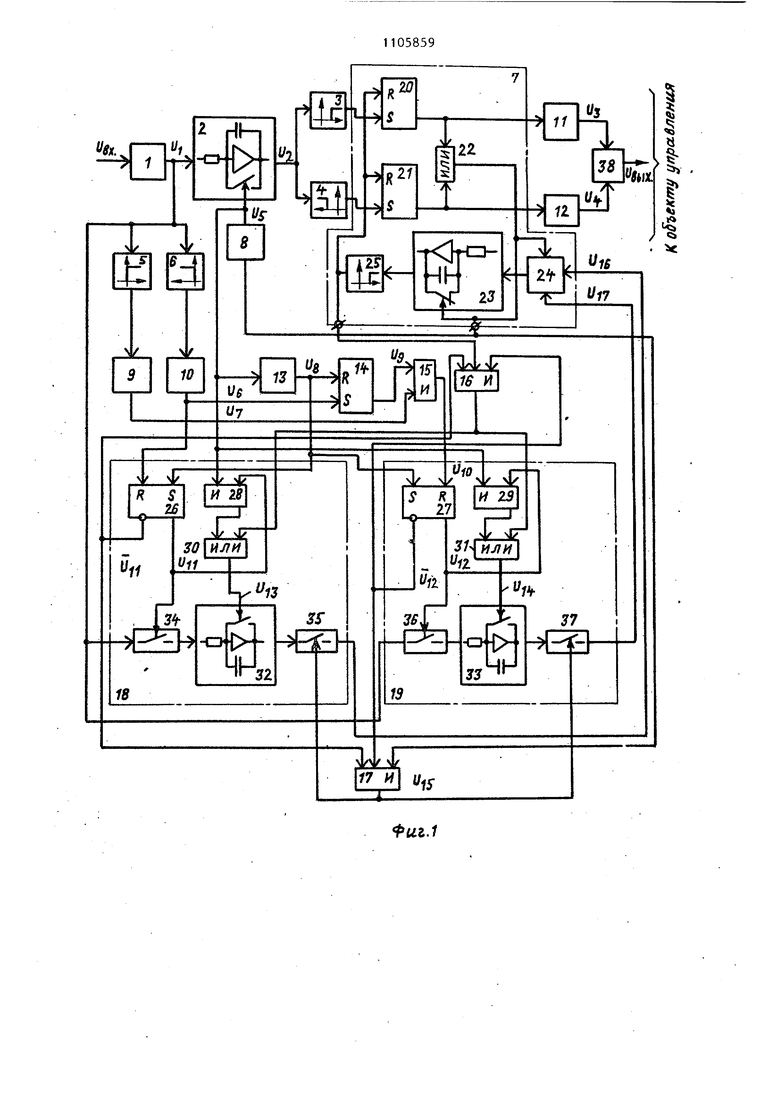

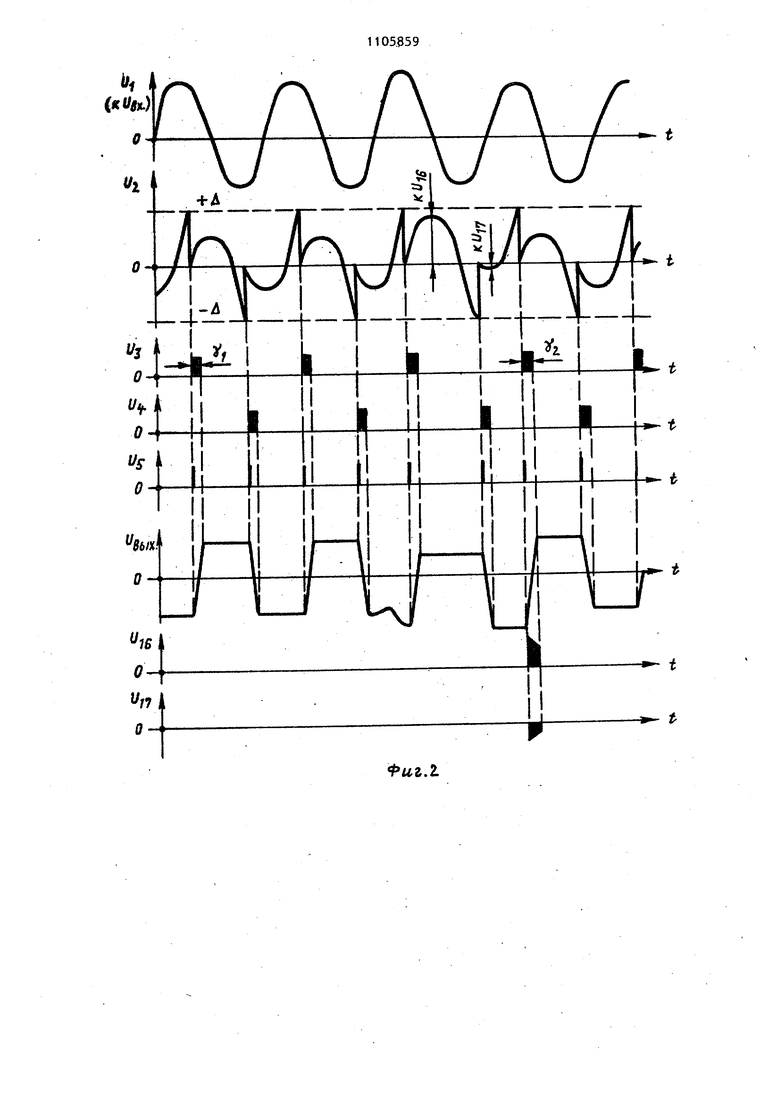

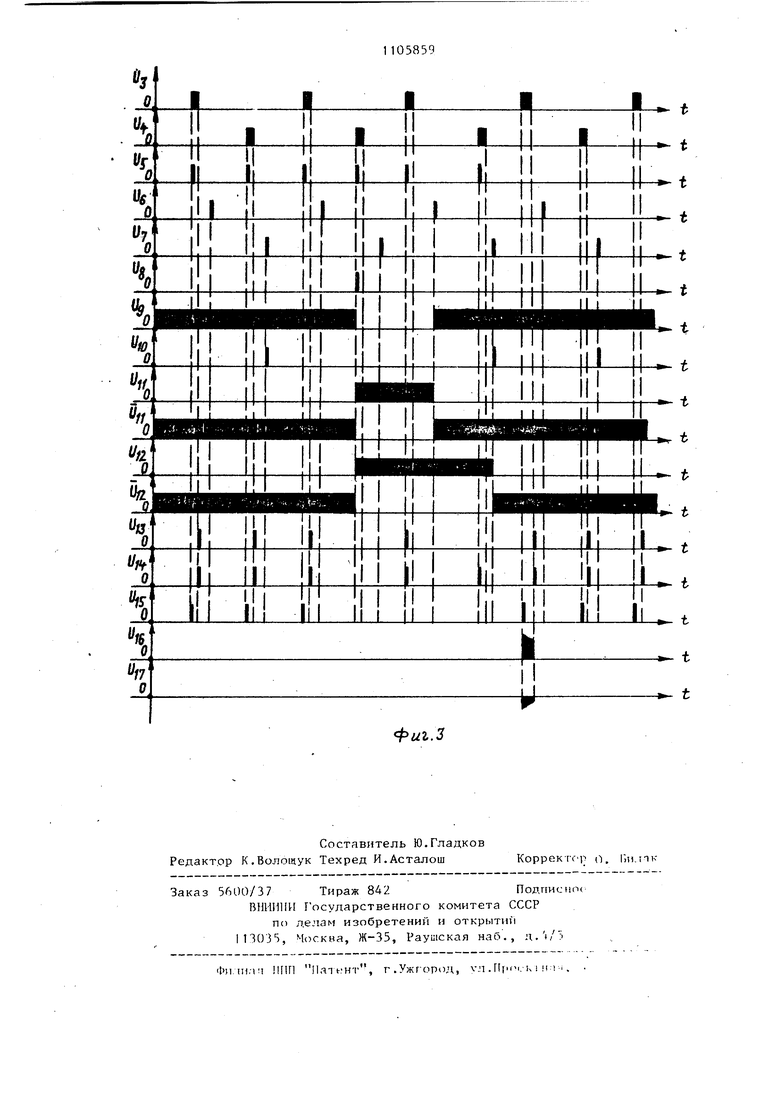

Изобретение относится к автоматическим импульсным регуляторам, в которых выходной сигнал является прерывной функцией отклонения входного скгцала от заданной величины, и может .быть применено в системах автоматического управления различных процессов в теплоэнергетике и химии при использовании в качестве исполнитель ных устройств исполнительных механиз мов постоянной скорости в случае, ес ли объект управления обладает фильтрующими свойствами. - Известен импульсньй регулятор, содержащий первьш сумматор, подключенный первым входом к выходу задатчика, вторым входом - к выходу датчи ка регулируемой величины и к выходу дифференциатора, а выходом через iпоследовательно соединенные устрой ства усилитель, интегратор, трехпози ционньй релейный блок и второй сумма тор - к усилителю мощности, блок задержки и ключ, сигнальным входом под ключенный к выходу дифференциатора, управляющим входом - к выходу трехпо зиционного релейного блока и к входу блока задержки, а выходом - ко второму входу второго сумматора, и выход блока задержки соединен с управляющим входом интегратора 1 . Известен также импульсный регулятор, содержащий последовательно соединенные предварительный усилитель, интегратор, усилитель мощноети,трехпозиционный релейный блок и реле времени, выходом подключенное к управляющему входу интегратора 2. Недостатком указанных регуляторов является их низкая точность. Наиболее близким по технической сущности к предлагаемому является импульсный регулятор, содержащий элемент ИЛИ и третий одновибратор, а также последовательно соединенные предварительный усилитель и интегратор, выходом соединенньй через последовательно соединенные первый релейньш блок, первый одновибратор и первьй усилитель мощности - с вторым входом исполнительного механизма, входы элемента ИЛИ подключены к выходам первого и второго одновибраторов, а выход через третий одновибратор к управляющему входу интегратора 3 J Недостатком известного регулятора является его низкая точность. Цель изобретения - повышение точности регулятора.. Поставленная цель достигается тем, что в импульсном регуляторе, содержа:щем первый и второй усилители мощности, выходами подключенные к первому и второму входам исполнительного механизма, первый, второй и третий одновибраторы и последовательно соединенные предварительньм усилитель и интегратор, управляющим входом подключенный к выходу первого одновибратора, а выходом - ко входам первого и второго релейных блоков, дополнительно установлены третий и четвер тый релейные блоки, первый, второй и третий элементы И, R5 -триггер,первый и второй блоки памяти, счетчик импульсов и широтно-импульсный модулятор, первым и вторым тактовыми входами подключенный к выходам соответственно первого и второго релейных блоков, первым и вторым управляющими входами - к сигнальным выходам соответственно первого и второго блоков памяти, первым и вторым сигнальными выходами - ко входам соответственно первого и второго усилителей мощности, первым информационны выходом - к выходу первого одновибратора и первому входу первого элемента И, а вторым информационным выходом - к первому входу второго элемента И, выход усилителя подключен к сигнальным входам первого и второго блоков .памяти, через последовательно соединенные третий релейный блок и второй одновибратор - к первому входу третьего элемента И, а через последовательно соединенные четверты релейный блок и третий одновибратор к первому управляющему входу первого блока памяти и к S-входу R5-триггера, выходом подключенного ко второму входу третьего элемента И, выходом подключенного к первому управляющему входу второго блока памяти, выход первого одновибратора подключен ко вторым управляющим входам первого и второго блоков памяти,а через счетчик импульсов - к третьим управляющим входа первого и второго блоков памяти и к R входу Д -триггера, информационный выход первого блока памяти подключен ко 1 594 вторым входам первого и второго элементов К, информационньй выходвторого блока памяти подключен к третьим входам первого -и второго элементов И, выходы которых подключены соответственно к четвертым и пятым входам первого и второго блоков памяти. Причем, блок памяти содержит RS-триггер и последорательно соединеиные элементы И и ИЛИ и последовательно соединенные первый ключ, интегратор и второй ключ, управляющим входом подключенный к четвертому управляющему входу блока памяти, а выходом - к сигнальному выходу блока памяти, сигнальный вход которого подключен к сигнальному входу первого ключа, управляющим входом подключенного к первому входу элемента Н и прямому выходу RS -триггера, R-входом подключенного к первому управляющему входу блока памяти, 5 -входом к третьему управляющему входу блока памяти,а инверсным выходом - к информационному выходу блока памяти, пятым управляющим входом подключенного к первому входу элемента ИЛИ, а вторым управляющим входом - ко второму входу элемента И, выходом подключенного ко второму входу элемента ИЛИ, выходом подключенного к управляющему входу интегратора. Кроме того, щиротно-импульсный модулятор содержит элемент ИЛИ, первый и второй RS -триггеры и последовательно соединенные сумматор, интегратор и релейный элемент, выходом соединенный с R -входами первого и второго R5 -триггеров и с вторым информационным выходом широтно-импульсного модулятора, первым и вторым сигнальными входами соединенного с 5-входами ЦЗ-триггеров, первым и вторым управляющим выходами - с вторым и третьим входами сумматора, первым информационным вЫходом - с выходом элемента ИЖ, первым входом сумматора и управляющим входом интегратора, а первым и вторым сигнальными выходамис выходами соответственно первого и второго RS -триггеров и с первым и вторым входами элемента ШШ. На фиг.1 представлена функциональная схема импульсного регулятора; на фиг.2 и 3 - экраны выходных напряже- НИИ основных блоков регулятора. Импульсный регулятор содержит предварительньй усилитель 1, интегратор 2, первый, второй, третий и четвертьш релейные блоки 3-6, широтноимпульсньй модулятор 7, первый, второй и третий одновибраторы 8-10, первый и второй усилители мощности 11 и 12, счетчик импульсов 13, RS -тригге 14, третий, второй и первый элементы И 15-17, блоки памяти 18 и 19.

Широтно-импульсный модулятор 8 содержит первьм и второй RS -триггеры 20 и 21, элемент ИЛИ 22, интегратор 23, сумматор 24 и релейный элемент 25.

Блоки памяти 18 и 19 включают в себя соответственно R5 -триггеры 26 и 27, элементы И 28 и 29, элементы ИЛИ 30 и 31, интеграторы 32 и 33, первьш и второй ключи 34, 35 и 36, 37. Б процессе регулирования.управляющее воздействие на объект первый и второй ключи 34 и 35 регулирования формируется исполнительным механизмом постоянной скорости 38.

Кроме того, на фиг.1, 2, 3 приняты обозначения: Ug - входное напряжение импульсного регулятора, U

и. выходное напряжение предварительного усилителя 1, Uo - выходное напряжени интегратора -2, U- и - выходные напряжения соответственно первого и второго усилителей мощности 11 и 12, Ug-jU, U-, - выходные напряжения соответственно первого, второго, третьего одновибраторов 8-10 , Ug - входное напряжение счетчика импульсов 13

Ug - выходное напряжение R5 -триггера 14, U-iQ- выходнс е напряжение . третьего элемента И 15, U., , U выходные напряжения на прямом и инверсном выходах R5 -триггера 26,( Cii2 выходные напряжения на прямом .и инверсном выходах R5 -триггера 27 и.- . выходные напряжения соответственно элементов ИЛИ 30 и 31, и,„ - выходное напряжение первого элемента И 17, U ( выходные напряжения на сигнальных выходах соответственно первого и второго блоков памяти 18 и 19, (Jo., выходное напряс Ь1 л

жение импульсного регулятора.

Регулятор работает следующим образом.

На вход предварительного усилител 1 поступает напряжение Ug , равное разности между заданным и дейдтвительным значениями регулируемого параметра. С выхода предварительного усилителя 1 напряжение U zkUgjj где 1с - коэффициент усиления предварительного усилителя 1, поступает на вход интегратора 2. С выхода интегратора 2 напряжение Uj поступает на входы первого и второго релейных блоков 3 и 4. При достижении напряжением на выходе интегратора 2 величины порога срабатывания одного из релейных блоков 3 или 4 последний срабатывает, подавая ступенчатое напряжение на один из тактовых входов широтно-импульсного модулятора входом 7. При этом на соответствующем выходе широтно-импульсного модулятора 7 и на выходе одного из усилителей мощности 11 (или 12) формируется импульс управляющего напряжение U (или U ), поступающего на один из входов исполнительного механизма 38. Длительность у импульса управляющего напряжения определяется настройкой элементов широтно-импульсного модулятора 7, а также величиной и полярностью напряжений и и на его управляющих входах. В случае, если напряжения и, и и отсутствуют или взаимно компенсируются в сумматоре 24 широтно-импульсного модулятора 7, длительность импульсов управляющего напряжения определяется только параметрами широтно-импульсного модулятора 7 коэффициентами передачи сумматора 24, интегратора 23 и порогом срабатывания релейного элемента 25. При поступлении напряжения на один из тактовых входов широтно-импульсного модулятора 7 происходит переключение соответствующего R5 -триггера 20 (или 21). При этом через элемент ИЛИ 22 и сумматор 24 напряжение поступает на вход интегратора 23. Одновременно с выхода элемента ИЛИ 22 напряжение поступает на управляющий вход интегратора 23, разрешая процесс интегрирования, и на первый информационный выход широтноимпульсного модулятора 7, подключенный ко входу первого одновибратора 8. Первый одновибратор 8 срабатывает по переднему фронту кусочно-постоянного напряжения на первом информационном выходе широтно-импульсного модулятора 7, формируя короткий импульс управляющего .напряжения, поступающий на управляющий вход интегратора 8 и осуществляющий сброс интегратора 8 до нулевого уровня. Одновременно напряжение Ug с выхода первого одновибратора 8 поступает на вторые управляющие входы блоков памяти 18 и 19, а также на вход счетчика импульсов 13. Счетчик импульсов 13 предназначен для выдачи импульса управляющего напряжение при поступлении на его вход заданного количества импульсов. Тем самым обеспечивается формирование корректирующего напряжения с заданным периодом следования импульсов. В течение периода интегрирования интегратора 23 широтно-импульсного модулятора 7 на выходе регулятора сохраняется импульс управляющего напряжение. При достижении напряжением на выходе интегратора 23 величины, превьшающей порог срабатывания релейного элемента 25, последний срабатывает, возвращая. R5 -триггеры 20 и 21 широтно-импульсного мо-. дулятора 7 в исходное состояние. В дальнейшем описанный процесс повторя ется и на выходе регулятора формируется частотно-модулированная последовательность импульсов управляющего напряжения, частота следования которых определяется величиной напряжения (Jg на входе регулятора, а знак выходного напряжения и, регулятора определяете знаком напряжения Ug) на его входе. При отработке управляющего или возмущающего воздействия импульсньм регулятором в соста ве системы автоматического регулирования в ней устанавливается автоколе бательньш процесс с произвольной сте пенью несимметрии на вькоде исполнительного механизма 38. При отключени корректирующих элементов регулятора величина-предельногоотклонения ВЫХОДНОГО напряжения U на выходе исполнительного механизма 38 равна реакции последнего на один импульс управляющего напряжения. Корректирующими элементами регулятора являются все блоки, принимающие участие в формировании корректирующих напряжеНИИ .-и и , поступающих на управляющие входы широтно-импульсного модулятора 7 и соответственно на входы сумматора 24 щиротно-импульсного модулятора 7. Корректирующие напряжения U, U формируются таки образом, что длительность их импульсов изменяется, обеспечивая в систем автоматического регулирования периодический процесс с заданными парамет рами, в рассматриваемом частном случае обеспечивается симметричное пери одическое, напряжение Ugjjix на выходе исполнительного механизгга 38 с мини- мальньми отклонениями напряжения ВЫл ° заданного значения. Формирование корректирующих напряжений , U основывается на том, что симметричному автоколебательному напряжению на выходе исполнительного механизма 38 при фильтрующих свойствах участка системы автоматического регулирования между выходом исполнительного механизма 38 и входом импульсного регулятора соответствует симметричный процесс изменения напряжения на выходе интегратора 2, а несимметричному автоколебательному напряжению U, на выОЫХ ходе исполнительного механизма 38 несимметричный процесс изменения напряжения на выходе интегратора 2, причем чем больше по абсолютной величине максимальное отрицательное отклонение напряжения У на выходе исполнительного механизма 38.превышает его максимальное положительное отклонение, тем больше по абсолютной величине значение напряжения U2 на выходе интегратора 2 в момент изменения производной напряжения U2 с положительного значения на отрицательное, чем значение этого же напряжения при последующем изменении знака производной напряжения ,U2 Работа указанных корректирующих элементов импульсного регулятора осуществляется следующим образом. Напряжение с выхода предварительного усилителя 1 и одновременно с поступлением на вход интегратора 2 поступает на входы первого и второго блоков памяти 18 и 19 и третьего и четвертого релейных блоков 5 и 6. После формирования на выходе импульсного регулятора определенного количества импульсов на выходе счетчика импульсов 13 появляется импульсное напряжение Ug , осуществляющее переключение R5 -триггера 14, что приводит к пропаданию напряжения на его выходе и поступающее на третьи управляющие входы блоков памяти 18 и 19, служащие для формирования управляющих напряжений И 16 и 17 и соединенные с S-входами RS -триггеров 26 и 27. При переключении R5 -триггеров 26 и 27 напряжения с их выходов поступают на управляющие входы ключей 34 и 36 и на первые входы элементов И 28 и 29. При этом напряжения на выходах интеграторов 32 и 33 с заданньв коэффициентом масштабирования повторяют напряжение (J2 на выходе интегратора 91 2. При изменении полярности напряжения на выходе усилителя 1 с положительной на отрицательную, что соотве ствует изменению знака производной напряжения U,j на выходе интегратора 2 с положительного на отрицательный, происходит срабатывание четвертого релейного блока 6 и запуск третьего одновибратора 10 по переднему фронту напряжения на выходе третьего релейного блока 6. Напряжение с выхода третьего одновибратора 10 осуществляет переключение RS -триггера 26 первого блока памяти t8, отключая его вход, и переключение RS -триггер 14, подготавливая дальнейшую работу регулятора. Таким образом на выходе интегратора 32 сохраняется значение напряжения U, , пропорциональное значению напряжения U выходе ин тегратора 2 в момент изменения знака производной последнего с положительного на отрицательное значение. При последующем изменении знака напряжения и на выходе усилителя 1 происходит аналогичное срабатывание третьего релейного блока 5, второго одновибратора 9 и переключение R5-триггера 27 второго блока памяти 1 при поступлении напряжения с выхода третьего элемента И 15, на всех входах которого в этот момент присутствуют напряжения. В этот момент на вы ходе интегратора 33 сохраняется значение напряжения U , пропорциональное значению напряжения U на выходе интегратора 2 в момент измене ния знака производной последнего с 9 отрицательного на положительное значение. При начале очередного импульса напряжения управления, что фиксируется возникновением напряжения на выходе первого элемента И 17, сигнальные выходы блоков памяти 18 и 19 оказьшаются подключенными к управляющим входам широтно-импульсного модулятора 7, корректируя тем самым длительность импульса напряжения И.,... на выьыхходе регулятора. В момент окончания импульса напряжения управления, что фиксируется появлением напряжения на выходе второго элемента И 16, на всех входах которого в этот момент присутствуют напряжения происходит обнуление интеграторов 32 и 33 блоков памяти 18 и 19. Дальнейшая работа регулятора повторяется при очередном поступлении импульса напряжения с выхода счетчика импульсов 13. Таким образом в регуляторе создается периодически действующий внутренний контур регулирования, обеспечивающий оптимальные для данной системы автоматического регулирования параметры периодического режима. Необходимые параметры автоколебательного режима могут быть установлены за счет соответствующих коэффициентов усиления интеграторов 33 и 32 блоков памяти 18 и 19 и коэффициентов усиления по входам сумматора 24 широтно-импульсного модулятора 7. Таким образом, точность предложенного регулятора повышается в 2 раза по сравнению с известным.

.l

фиг.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Импульсный регулятор | 1981 |

|

SU1004969A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| и Чеховой Ю.И | |||

| Нелинейные системы с частотно- и широтно-импульсной модуляцией | |||

| Киев, Техника, 1970, с | |||

| Устройство для усиления микрофонного тока с применением самоиндукции | 1920 |

|

SU42A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Моделирование систем автоматического регулирования с интегральной частотно-импульсной модуляцией | |||

| - В кн.: Известия Ленинградского электротехнического института, вып | |||

| Горный компас | 0 |

|

SU81A1 |

| Ленинград, 1969 , с | |||

| Индукционная катушка | 1920 |

|

SU187A1 |

Авторы

Даты

1984-07-30—Публикация

1982-10-29—Подача