вертым управляющим входом - к четвертому управляющему входу второго блока памяти, И-входам пербого, второго и третьего 1Ч5-триггеров и выходу первого элемента И, вторым входом подключенного к выходу первого одновибратора, выход второго одновибратора соединен с S-входом второго RSтриггера, вход третьего одновибратора соединен с выходом -четвертого релейного блока, а выход - с вторым входом второго элемента И, второй вход элемента ИЛИ подключен к выходу третьего релейного блока, а выход - к управляющему входу ключа, сигнальным входом подключенного к выходу предварительного усилителя и входу фильтра.

2. Регулятор по п. 1, отличающийся тем, что блок памяти содержит элемент И и последовательно соединенные первый ключ, усилитель, запоминающий элемент и второй ключ, выходом подключенный к выходу блока памяти, сигнальный вход, первый, второй, третий и четвертьш управляющие входы которого пЪдключены соответственно к сигнальному и управляющему входам первого ключа, управляющему входу второго ключа, первому и второму входам элемента И, выходом подключенного к управляющему входу запоминающего элемента.

3. Регулятор по пп, 1 и 2, о тличающийся тем, что широтно-импульсный модулятор содержит первьй и второй RS-триггеры и последовательно соединенные элемент ИЛИ, сумматор, интегратор и релейный элемент, выходом соединенный с R -входами первого и второго RS-триггеров, 5-входами подключенных соответственно к первому и второму сигнальным входам широтно-импульсного модулятора, первым и вторым управляющими в одами подключенного к второму и третьему входам сумматора, а первым |И вторым сигнальными вькодами - к выходам соответственно первого и второго Р5-триггеров и соответственно первому и второму входам элемента ИЛИ, а информационным выходом - к выходу элемента ИЛИ и управляющему йходу интегратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсный регулятор | 1982 |

|

SU1105859A1 |

| Импульсный регулятор | 1984 |

|

SU1238025A1 |

| Импульсный регулятор | 1982 |

|

SU1101787A1 |

| Частотно-импульсный регулятор | 1985 |

|

SU1278806A1 |

| Импульсный регулятор | 1984 |

|

SU1251025A1 |

| Частотно-импульсный регулятор | 1984 |

|

SU1238028A1 |

| Импульсный регулятор | 1984 |

|

SU1170426A1 |

| Частотно-импульсный регулятор | 1987 |

|

SU1444709A1 |

| Импульсно-релейный регулятор | 1984 |

|

SU1228072A1 |

| Датчик разности фаз | 1980 |

|

SU962817A1 |

1. ИМПУЛЬСНЫЙ РЕГУЛЯТОР, содержащий первый и рторой усилители мощности, выходами подключенные к первому и второму входам исполнительного механизма, первый, второй и третий одновибраторы, элемент ИЛИ и последовательно -соединенные предварительный усилитель и интегратор,управляницим входом подключенный к выходу первого одновибратора, а выходом - к входам первого и второго релейных блоков, отличающийс я тем, что, с целью повышения точности регулятора, в него введены широтно-импульсн1)1й модулятор, первый и второй блоки памяти, последовательно соединенные первый R5-триггер и первый элемент.И, последовательно соединенные фильтр и третий релейный блок, последовательно соединенные второй Р5-триггер, второй элемент И,третий ftS-триггер и третий элемент И, последовательно соединенные ключ, четвертый релейный блок, первый элемент НЕ и четвертый элемент И, последовательно соединенные дифференциатор, пятьш релейный блок, второй элемент НЕ и пятый элемент И, вторым входом подключенный к выходу третьего R5триггера и второму входу четвертого элемента И третьим входом - к выходу первого элемента НЕ и входу третьего одновибратора, а выходом - к первому управляющему входу второго блока памяти, вторым управляющим входом подключенного к выходу четвертого элемента И, второму управляющему входу первого блока памяти и 5 -входу перI вого RS-триггера, сигнальным входом к выходу ключа, входу дифференциатора и сигнальному входу первого блока памяти, а выходом - к второму управляющему входу ШИРОТНО-ИМПУЛЬСНОГО МО- j-j дулятора, первым управляющим входом подключенного к выходу первого блока памяти, первым и вторым сигнальными входами - к выходам соответственно VI первого и второго релейных блоков, сд первым и вторым сигнальными выхода00 ми - к входам соответственно первого и второго усилителей мощности, а инсд формационным выходом - к входу первого одновибратора и третьему входу четвертого элемента И, четвертым входом подключенного к выходу пятого релейного блока и второму входу третьего элемента И, выходом подключенного к первому управляющему входу первого блока памяти, третьим управляющим входом подключенного к выходу первого RS-триггера, третьему управляющему входу второго блока памяти и первому входу элемента ИЛИ, а чет

Изобретение относится к автоматическим импульсным регуляторам, в которых выходной сигнал является прерывной функцией отклонения входного сигнала от заданной величины, и может быть применено в системах автоматического управления объектами с малой инерционностью при использовании в качестве исполнительных устройств исполнительных механизмов постоянной скорости, например, в установках для приготовления смеси жидкостей заданной температуры путем изменения концентрации компонентов смеси из двух жидкостей с различной температурой.

Известен импульсный регулятор, содержащий первый сумматор, подршю™ ченный первым входом к выходу задатчика, вторым входом - к выходу датчика регулируемой величины и входу дифференциатора, а выходом через последовательно соединенные усилитель интегратор, трехпозиционный релейньп блок и второй сумматор - к усилителю

мощности, блок задержки и ключ, сигнальным входом подключенный к выходу дифференциатора, управляющим входом к выходу трехпозиционного релейного блока и входу блока задержки, а выходом - к второму входу второго сумматора, выход блока задержки соединен с управляющим входом интегратора и.

Известен импульсный регулятор, содержащий последовательно соединенные предварительный усилитель, интегратор, усилитель мощности, трехпозиционный релейный блок и реле времени, выходом подключенное к управляющему входу интегратора 2.

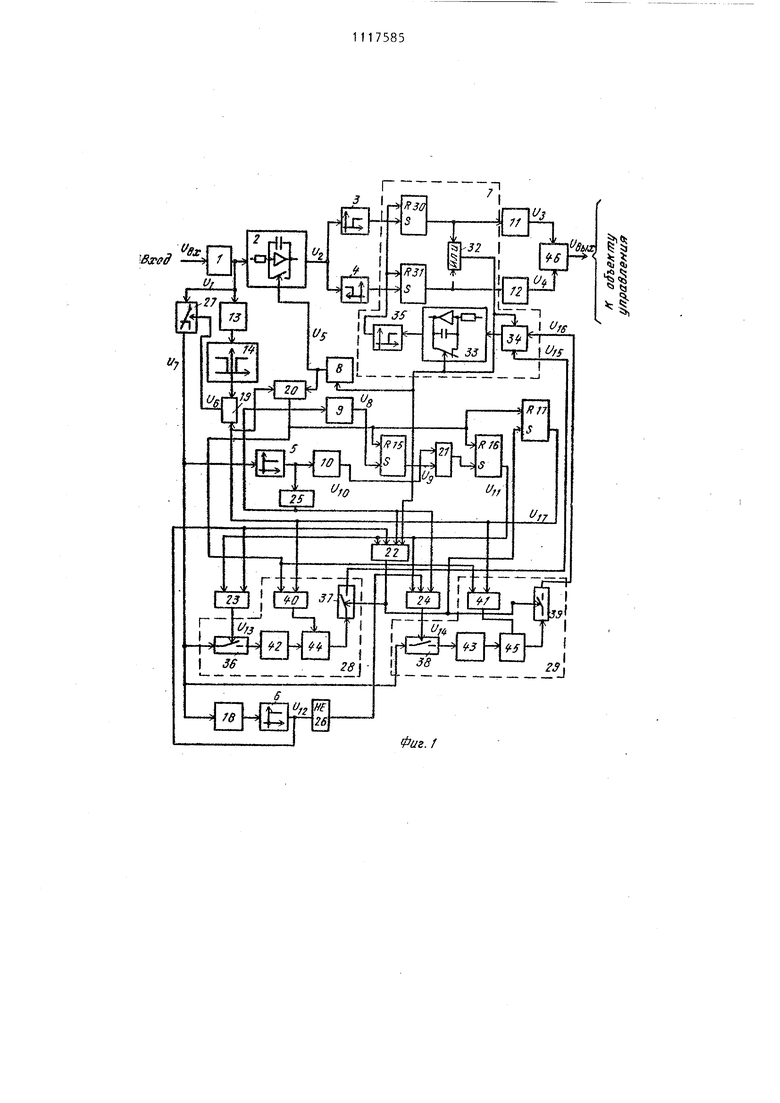

Наиболее близким к изобретению по технической сущности является импульсный регулятор, содержащий элемент ИЛИ, третий одновибратор и последовательно соединенные предварительный усилитель напряжения и интегратор, выходом соединенный через последовательно соединенные первый 3 релейный блок, первый одновибратор и первый усилитель мощности с первым входом исполнительного механизма, а через последовательно соединенные второй релейный блок, второй одновиб ратор и второй усилитель мощности с вторым входом исполнительного меха низма, входы элемента ИЛИ подключены к выходам первого и второго одновибраторов, а выход через третий одновибратор - к управляющему входу интегратора L3 . Недостатком известных устройств является их низкая точность. , Цель изобретения повьшение точности регулятора. Поставленная цель достигается тем, что в импульсньй регулятор, содержащий первый и второй усилители мощности, выходами подключенные к первому и второму входам-исполнитель ного механизма, первый, второй и тре тий одновибраторы, элемент ИЛИ и последовательно соединенные предварительный усилитель и интегратор, управляющим входом подключенный к вы ходу первого одновибратора, а выходом - к входам первого и второго релейных блоков, введены шнротно-импульсный модулятор, первый и второй блоки памяти, последовательно соединенные первый R5-триггер и первый элемент И, последовательно соединенные фильтр и третий релейный блок, последовательно соединенные второй R5 триггер, второй элемент И, третийRSтриггер и третий элемент И,последова тельно соединенные ключ, четвертый релейный блок, первый элемент НЕ и четвертый элемент И, последовательно соед1 ненные дифференциатор, пятый релейный блок, второй элемент НЕ и пятый элемент И, вторым входом подключенньй к выходу третьего RS-триггера и к второму входу четвертого элемента И, третьим входом - к вькоду первого элемента НЕ и входу третьего одновиб ратора, а выходом - к первому управляющему входу второго блока памяти, вторым управляющим входом подключенного к выходу четвертого элемента И, второму управляющему входу первого блока памяти и 5-входу первого RS триггера, сигнальным входом - к выходу ключа, вхбду дифференциатора и сигнальному входу первого блока памя ти, а выходом - к второму управляюще му входу широтно-импульсного модуля85тора, первым управляюп1им входом подключенного к выходу первого блока памяти, первым и вторым сигнальными входами - к выходам соответственно первого и второго релейных блоков, первьм и вторым сигнальными выходами к входам соответственно первого и второго усилителей мощности, а информационным выходом - к входу первого одновибратора и третьему входу четвертого элемента И, четвертым входом подключенного к выходу пятого релейного блока и второму входу третьего элемента И, выходом подключенного к первому управляющему входу первого блока памяти, третьим управляюищм входом подключенного к вхо выходу первого RS-триггера, третьему управляющему входу второго блока памяти, и первому входу элемента ИЛИ, а четвертым управляющим входом - к четвертому управляющему входу второго блока памяти, R-входам первого, второго и третьего Rs-триггеров и выходу первого элемента И, вторым входом подключенного к выходу первого одновибратора, выход второго одновибратора соединен с S-входом второго В5-триггера, вход третьего одновибратора соединен с выходом четвертого релейного блока, а выход - с вторым входом второго элемента И, второй вход элемента ИЛИ подключен к выходу третьего релейного блока, а выход к управляющему входу ключа, сигнальным входом подключенного к выходу предварительного усилителя и входу фильтра. При этом каждый блок памяти содержит элемент И и последовательно соединенные первый ключ, усилитель, запоминающий элемент и второй ключ, выходом подключенный к выходу блока памяти, сигнальный вход, первый, второй, третий и четвертый управляющие входы которого подключены соответственно к сигнальному и управляющему входам первого ключа, управляющему входу второго ключа, первому и второму входам элемента И, выходом подключенного к управляющему входу запоминающего элемента. Кроме того, широтно-импульсный модулятор содержит первый и второй R5-тpиггepы и последовательно соединенные элемент ИЛИ, сумматор, интегратор и релейный элемент, выходом соединенный с R-входами первого и 511 второго RS-TpHrrepoB, 5-входами подключенных соответственно к первом и второму сигнальным входам широтноимпульсного модулятора, первым и вторым управляющими входами подключенного к второму и третьему входам сумматора, первым и вторым сигнальны ми выходами к выходам соответствен но первого и второго RS-триггеров и соответственно первому и-второму входам элемента 1ШИ. а информационны выходом - к выходу элемента ИЛИ и управляющему входу интегратора. На фиг«1 представлена функциональ ная схема предлагаемого и импульсного регулятора на фиг,2 - эпюры выходных напряжений основных блоков регулятора при отработке внешнего воздействия j на фиг.З - эпюры выходных напряжений блоков регулятора, обеспечиваюищх формирование корректирующего воздейст вия. Регулятор содержит предварительный усилитель 1.напряжения, интегратор 2 релейные первый, второй, четвертый и пятый блоки 3-6, широтно-импульс ный модулятор 7, первый, второй и третий одновибраторы 8 10, первый второй yci-тители 11 и 12 мощности, фильтр 13, третий релейный блок 14, второй, третий и первый RS-триггеры 15 - 17, дифференциатор 18, элемент ИЛИ. 19, первый, второй, четвертый, третий и пятьй элементы И 20 - 24, первый и второй элементы НЕ 25 и 26, ключ 27, первый и второй блоки 28 и 29 памяти. Широтно-импульсный модулятор 7 включает в себя первый и второй RSтриггеры 30 и 31, элемент ШШ 32, интегратор 33, сук-матор 34 и релейны элемент 35. Блоки 28 и 29 памяти содержат соответственно ключи 36, 37 и 38, 39, элементы И 40 и 41, усилители 42 и 43 напряженияJ запоминаюпще элементы 44 и 45. В процессе регулирования исполнительный механизм 46 воздействует на объект регулирования, изменяя его положение (объект регулирования и система автоматического регулирования на фиг., 1 не показаны) , Кроме того, на схеме обозначены; 110 - входное напряжение импульсного регулятора; U., - выходное напряжение предварительного усилителя 1; U выходное напряжение интегратора 2; 56 Uj и выходные напряжения соответственно первого и второго зсилителей 11 и 12 мощности; Ug- - выходное напряжение первого одновибратора 8| Ur - выходное напряжение элемента ИЛИ| Uf выходное напряжение ключа 27; Ug выходное напряжение второго одновибратора 9;; Uc. выходное напряжение второго R5 Tpnrrepa 15| -jo выходное напряжение трет.ьего одновибратора 10; выходное напряжение третьего Rs-триггера 16; .3 выходное напряжение пятого релейного блока 6г и,,- и Ц выходные напрялсения соотвётстрзенно третьего и пятого элементов И 23 и 24; U и и - выходные напряжения первого и второго блоков 28 и 29 памяти; Цт выходное напряжение первого Я5 триггера 17. Фильтр 13 служит для выделения низкочастотной составляющей выходного напряжения U предварительного усилителя 1 и в частном случае может быть реализован с помощью инерционного звена. Третий рапейный блок 14, имеющий двухпозиционную характеристику, может быть реализован с помощью параллельного соединения двух цепей, содержащих несимметричные однополярные релейные элементы, на входе одного из которых установлен инвертор, Запоминаюксие элементы 44 и 45 блоков 28 и 29 памяти могут быть реализованы с помощью параллельного соединен.ия конденсатора и ключа при соединении одной обкладки конденсатора с входом и выходом элемента, другой обкладки - с общей пшной элемента, а управляющего входа ключа с управ.гшющим входом элемента. Регулятор работает следующим образом,, На вход усилителя t поступает напряжение Ug,,, разное разности между заданньм и действительным значениями регулируемого параметра. С выхода усщ1ителя 1 напряжение U Ug k поступает на вход интегратора 2, с выхода которого напряжение О поступает на входы релейных блоков 3 и 4, При достижении напряжением U на выходе интегратора 2 величины порога срабатывания л одного из релейных блоков 3 (или 4) последний срабатывает, подавая ступенчатое напряжение на один из сигнальных входов широтноимпульсного модулятора 7. При этом на соответствующем выходе широтно-импульсного модулятора 7 и на выходе одного из усилителей 11 (или 12) мощности формируется импульс управляющего напряжение (J, (или l-) поступающего на один из входов исполнительного механизма 46. Длительность импульса управляемого напряжения U,,,onpeделяется настройкой широтно-импульсного модулятора 7, а также величиной и полярностью корректирующих напряжений и и, на управляющих входах широтно-импульсного модулятора 7, , поступающих с выходов первого и второго блоков 28 и 29 памяти. В если напряжения U Ць отсутствуют или взаимно компенсируются в сумматоре 34 широтно-импульсного модулятора 7, длительность импульсов напряжения на его выходе постоянна и определяется параметрами широтно-импульсного модулятора 7: коэффициентами передачи сумматора 34 и интегратора 33 и порогом срабатывания релейного элемента 35. При поступлении напряжения на один из сигнальных входов широтно-импульсного модулятора 7 происходит переключение соответствующего R5 -триггера 30 (или 31). При этом через элемент ИЛИ 32 и сумматор 34 напряжение поступает на вход интегратора 33 и на его управляющий вход, разрешая тем самым процесс интегрирования. Когда напряжение на выходе интегратора 33 достигает величины, достаточной для срабатывания релейного элемента 35, последний срабатывает, осуществляя переключение te-триггеров 30 и 31 в исходное .состояние. Таким образом, длительность импульса управляющего напряжения определяется величиной напряжения, поступающего на вход интегратора 33 и, соответственно, величиной и полярностью напряжении на входах сумматора 34. В момент начала импульса управляющего напряжения на информационном i выходе широтно-импульсного модулятор а 7 появляется напряжение, поступающее на вход одновибратора 8 и вызывающе© его срабатьшание по переднему фронту импульса напряжения. Импульс напряже- ния Uj с выхода одновибратора 8 поступает на управляюпщй вход интегратора 2, осуществляя его обнуление. В дальнейшем цикл повторяется, и на ;выходе регулятора формируется частотно-модуяиррванное напряжение, частота которого определяется величиной сигнала рассогласования, а знак знаком напряжения рассогласования Ugjf . После отработки регулятором управляющего или возмущающего воздействия в системе автоматического регулирования, которая содержит данный импульсный регулятор, устанавливается периодический автоколебательный процесс, причем предельная величина отклонения регулируемого параметра от заданного значения зависит от начальных условий в системе автоматического регулирования и в общем случае может быть равной реакции объекта регулирования на один импульс выходного напряжения Ug регулятора. Благодаря наличию корректирующих напряжений и и (J , в импульсном регуляторе в процессе регулирования происходит постоянный контроль параметров автоколебательного процесса в системе автоматического регулирования и приведение указанного автоколебательного процесса к симметричному при которо м обеспечивается максимальная точность системы автоматического регулирования при отклонении регулируемого параметра, не превьшающих реакции объекта регулирования на уменьшенный вдвое импульс управляющего напряжения Ug, . Работа элементов регулятора, формирующих корректирующие напряжение Ц, и и, , осуществляется следующим образом. С выхода предварительного усилителя 1 усиленное напряжение одновременно с поступлением на вход интегратора 2 поступает на вход фильтра 13, служащего для выделения постоянной составляющей напряжения Ц, и на сигнальный вход нормально замкнутого ключа 27. В случае, если постоянная составляющая напряжения и отсутствует или находится в допустимых пределах, на управляющий вход ключа 27 напряжение с выхода третьего релейного блока 14 через элемент ИЛИ 19 не поступает и ключ 27 находится в замкнутом состоянии. . , тсутствие постоянной составляющей напряжения U- свидетельствует об окончании отработки управляющего или возмущающего воздействия системы автоматического регулирования. С выхода ключа 27 напряжение поступает на входы четвертого релейного блока 5, дифференциатора 18 и ключей 36 и 38 блоков 28 и 29 памяти. Формирова9ние корректирующих напряжений U и и начинается в момент, когда напряжение и на выходе усилителя 1 имеет отрицательное значение, В этом случае на выходе элемента НЕ 25 формируется напряжение U , поступающее на вход первого одновибратора 9, что вызывает срабатывание последнего по переднему фронту импульса напряжения и переключение импульсом напряжения,, формируемым первым одновибратором 9, второго IRS Триггера 15. Невозможность возникновения напряжения на вы ходе элемента НЕ 25 до поступления напряжения с ключа 27 может быть организована, например, соответствующим управлением цепей питания блоков импульсного регулятора. Напряжение UQ с выхода второго RS-триггера 15 .поступает на один из входов второго элемента И 21, на другой вход которо го поступает импульсное напряжение с выхода третьего одновибратора 10 при изменении полярности напряжения U2 на входе интегратора 2 отрицатель ной на положительную, так как при этом происходит срабатывание четвертого релейного блока 5 и запуск третьего одновибратора 10 по переднему фронту ступенчатого напряжения с выхода четвертого релейного блока 5. Поскольку в этот момент времени t (фиг.2 и 3) производная входного напряжения и00 имеет положительное зна чение, напряжение Ц, с выхода пятог релейного блока 6 поступает на первы вход третьего элемента И 23, на второй вход которого поступает напряжение и„ с выхода третьего RS-триггера 16, находящегося во включенном состоянии. Напряжением U с выхода третьего элемента И 23 производится включение ключа 36 первого блока 28 памяти. Напряжение {J с выхода усилител я 1 проходит, таким образом, че рез ключи 27 и 36, усиливается усилителем 42 и поступает на вход запоминающего элемента 44 первого блока 28 памяти. Запоминающий элемент 44 служит для запоминания величины и полярности напряжения с выхода усилителя 42 и фиксирования его при отключенном входе первого блока 28 памяти. Вмомент i (фиг.2 и 3) изменения знака производной входного напряжения U-. или в момент равенств нулю производной напряжения Ug происходит обратное переключение пя8510того релейного блока Ь„ При этом происходит отключение первого блока 28 памяти от входного напряжения и подготовка цепей включения второго блока 29 памяти благодаря поступлению напряжения с выхода второго элемента НЕ 26 на один из входов пятого элемента И 24, В этот период времени на запоминающем элементе 44 первого блока 28 памяти сохраняется напряжение, пропорциональное максимальному значению напряжения Ugj положительной полярности на входе импульсного регулятора. При последующем изменении полярности напряжения на входе импульсного регулятора происходит аналогичное подключение входного напряжения к второму блоку 29 памяти благодаря формированию напряжения Ц на выходе первого элемента НЕ 25 в Момент времени t, (фиг. 2 и 3). Отключение второго блока 29 памяти от входного напряжения Ug осуществляется в момент времени ±(фнг,2 и 3) при очередном изменении полярности производной входного напряжения Ug , т.е. тогда, когда производная входного напряжения и„ становится положительной. На выходе запоминающего элемента 45 второго блока 29 памяти сохраняется напряжение, пропорциональное значению входного напряжения Ugv импульсного регулятора в момент достижения им максимального отрицательного значения. Б момент возникновения на выходе регулятора очередного импульса управляющего напряжения Ug.Cs предельном случае, когда объект регулирования полностью не имеет инерционности, этот момент совпадает с моментом t, изменения знака производной входного напряжения Ug, что определяется появлением переднего фронта импульса напряжения на входе одновибратора 8 и соответственно на одном из входов элемента И 22, происходит формирование напряжения на выходе последнего и включение ключей 37 и 39 блоков 28 и 29 памяти. Таким образом, выходы запоминающих элементов 44 и 45 блоков 28 и 29 памяти оказываются подключенными через ключи 37.и 39 к входам сумматора 34 пшротно-импульсного модулятора 7, вызывая в зависимости от настройки широтно-импульсного модуятора 7 увеличение или уменьшение лительности очередного импульса управляющего напряжения a,, Изменени коэффициентов усиления усилителей 42 и A3 обеспечивает уменьшение импульса напряжения ( заданную величину в слзгчае, е.сли по абсолютной величине максимальное значение положительного напряжения на входе импульсного регулятора меньше, чем отрицательное, и увеличение в противоположном случае. Одновременно с запоминанием напряжения в элементах 44 и 45 происходит переключение первого Re-триггера 17, напряжение L) с выхода которого поступает на первые входы элементов И 40 и 41 блоков 28 и 29 памяти, подготавливая к вклю чению цепь управления соответствующе го запоминающего элемента 44 (или 45), на первый вход элемента И 20, подготавливая цепи перевода регулятора в исходное состояние, и через элемент ИЛИ 19 на зтравляющий вход ключа 27, отключая блоки формировани корректирующих напряжений 0, и Ц от входного напряжения LL. При очередком импульсе управляющего напряжения (Jg,;,- ц, момент времени { (фиг. 2 и 3), благодаря поступлению импульса напряжения с выхода первого одновибратора 8 на второй вход первого элемента И 20. напряжение с выхода последнего осуществляет обратное переключение R -триггеров 15 - 17, возвращая тем самым регулятор в исходное состояние. Дальнейшая работа регулятора происходит аналогично. Таким образом, в предлагаемом регуляторе обеспечивается постоянный контроль и регулирование начальных условий автоколебательного процесса управления в системе автоматического регулирования, что в свою очередь обеспечивает минимально возможную величину отклонения регулируемого параметра от заданного значения. Точность предлагаемого регулятора повьпаается в 2 раза по сравнению с известным. Фаг./ П%а:

Фи8,3

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Импульсный регулятор | 1981 |

|

SU1004969A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Нелинейные системы с частотно- и широтно-импульсной модуляцией | |||

| Киев,, Техника, 1970, с | |||

| Устройство для усиления микрофонного тока с применением самоиндукции | 1920 |

|

SU42A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Моделирование систем автоматического регулирования с интегральной частотно-импульсной модуляцией | |||

| - В кн.: Известия Ленинградского электротехнического института, вып | |||

| Горный компас | 0 |

|

SU81A1 |

| Ленинград, 1968, с | |||

| Индукционная катушка | 1920 |

|

SU187A1 |

Авторы

Даты

1984-10-07—Публикация

1983-10-29—Подача