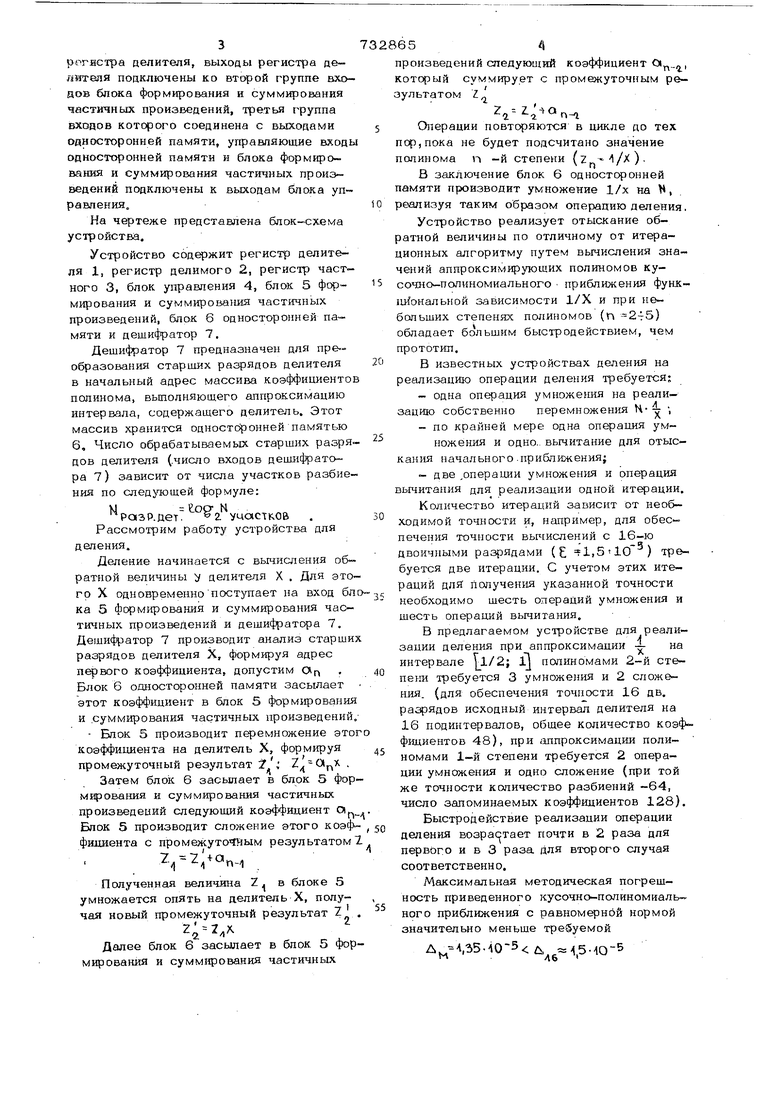

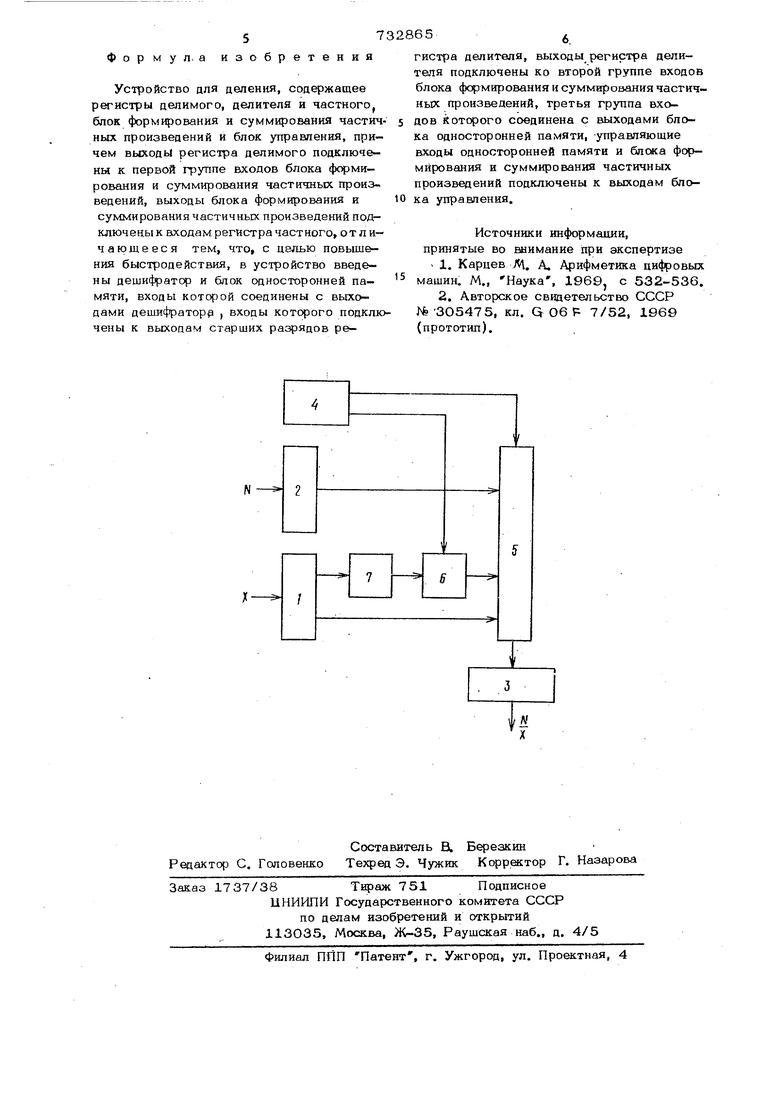

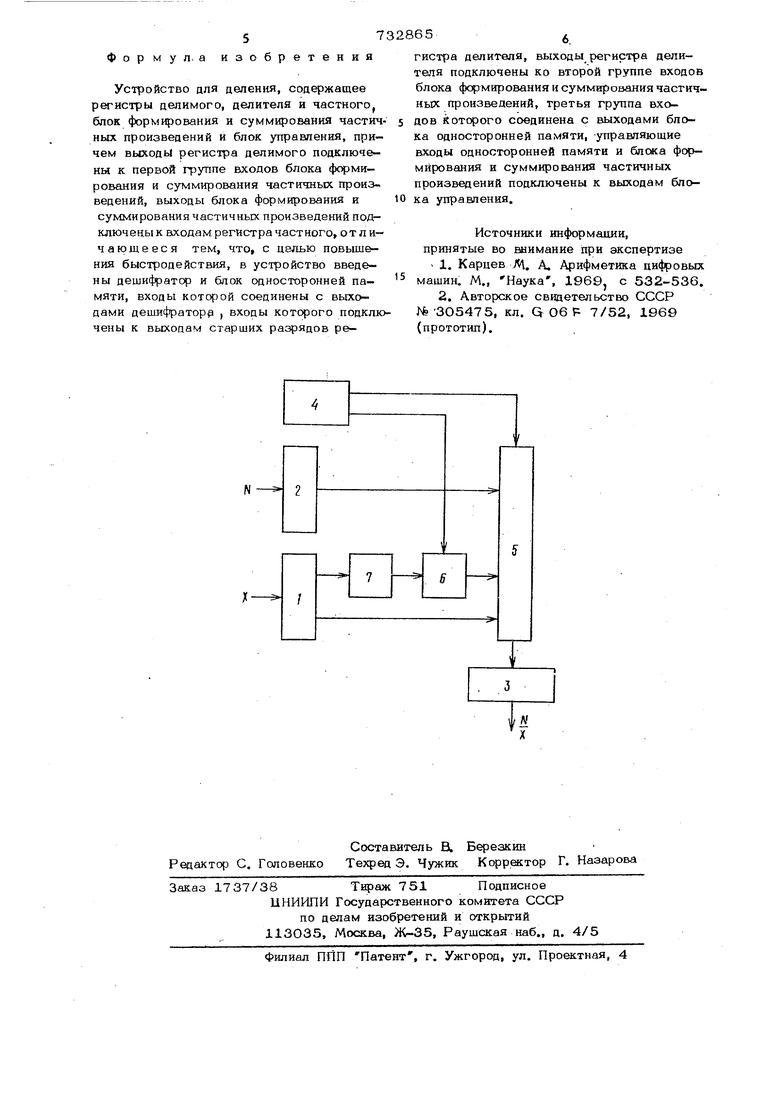

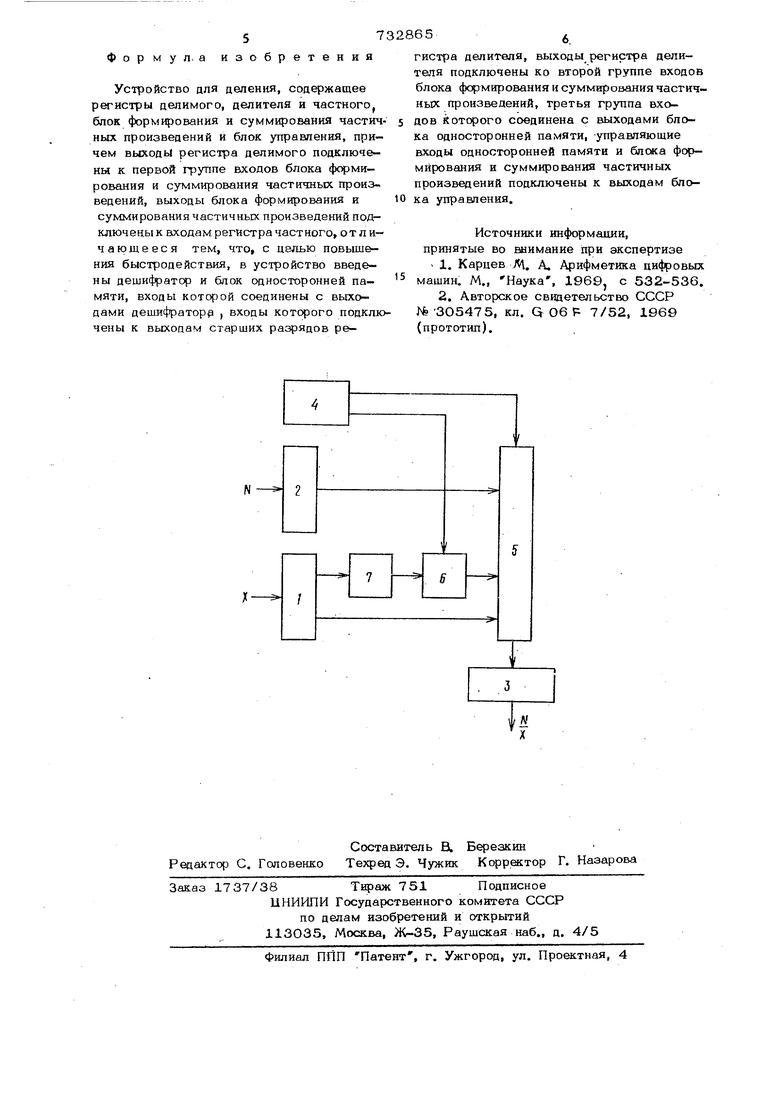

Изобретение относится к цифровой вычислительной технике и может быть использовано в арифметических устройствах цифровых машин. Известны устройства для целения, исполЕззующие итеративные методы, в состав оборудования входят входные и выходные регистры, блоки управления, дешифраторы множителя, блок-и формирования и суммирования произведений, бло ки определения начального приближения к обратной величине аргумента i , При этом на реализацию вычислений требуется значительное время, так как в каждом цикле вычислений необходимо пос ледовательное вьтолнение нескольких ите раций. Наиболее близким к изобретению явля ется устройство для деления, содержащее регистры делимого, делителя и частного блок формирования и суммирования части ных произведений, блок управления и блок нахождения начального приближения к обратной величиУ1е целителя, реализутощее операцию деления посредством умножения на обратную величину 2 , Но и такое устройство Для БЫЧИСЛ&ния обратной величины аргумента требует нескольких итераций, и е каждой итерации нужно выполнить по крайней мере два умножения. Цель изобретения - повышение быстр одействия. Для достижения поставленной цели в устройство для деления, содержащее регистры делимого, целителя и частного, блок формирования н суммирования час тичных произведений и блок управления, причем выходы регистра делимого €1одключены к первой группе взадов 6jjoKa формирования и суммирования частичных произведений, выходы блока формирования и суммирования частичных произведений подключены к входам регистра част ного, введены дешк4ратор и односторонняя память, входы которой соединены с В1 ходами дешифратора, входы которого подключены к вьисодам старших разрядов рпгнстра делителя, выходы регистра де лйтеля подключены ко второй группе вхо нов блока формирования и суммирования частичных произведений, третья группа входов которого соединена с выходами односторонней памяти, управляющие вход односторонней памяти и блока формирования и суммирования частичных произ ведений подключены к выходам блока уп равления, На чертеже представлена блок-схема устройства. Устройство содержит регистр делителя 1, регистр делимого 2, регистр част ного 3, блок управления 4, блок 5 формирования и суммироващш частичных произведений, блок 6 односторонней памяти и дешифратор 7. Дешифратор 7 предназначен для преобразования старших разрядов делителя в начальный адрес массива коэффициенто полинома, вьшолняющего аппроксимацию интервала, содержащего делитель. Этот массив хранится односторонней памятью 6. Число обрабатываемых старших разря дов делителя (.число входов деш11фрато ра 7) зависит от числа участков разбие ния по след тошей формуле: tog- N г 5 о V РазР.дет. 2. yuacTifiOB . Рассмотрим работу устройС7-ва для деления. Деление начинается с вычисления об ратной величины у делителя X . Для это гр X одновременнопосTjTiaeT на вход б ка 5 фс М фования и суммирования частичных произведений и дешифратора 7. Деши4ратор 7 производит анализ старши разрядов делителя X, формируя адрес первого коэффициента, допустим о Блок 6 односторонней памяти засылает этот коэффициент в блок 5 формировани и суммирования частичных произведений Блок 5 производит перемножение это коэффициента на делитель X, формируя промежуточный результат Z 0(pX . Затем блок 6 засылает в блок 5 фор мирования и суммирования частичных произведений следующий коэффициент О| Блок 5 производит сложение этого &оэф фициента с промежуточным результатом . Полученная величина Z в блоке 5 умножается опять на делитель X, получая новый промежуточный результат Z, 2; г,х Далее блок 6 засылает в блок 5 фор мирования и сумм рования частичных произведений следующий коэффициент , который суммирует с промежуточным результатом 2 Операции повторяются в цикле до тех пор,пока не будет подсчитано значение полинома п -и степени (z 1/Х). В заключение блок 6 односторонней памяти производит умножение 1/х на V, реализуя таким образом оперйцию деления. Устройство реализует отыскание обратной величины по отличному от итерационных алгоритму путем вычисления зна чений аппроксимирующих полиномов кусочно-полиномиального приближения функш нальной зависимости 1/Х и при небольших степенях полиномов (п -245) обладает большим быстродействием, чем прототип. В известных устройствах деления на реализацию операции деления требуется; -одна операция умножения на реализацию собственно перемножения Н- , - по крайней мере одна операция умножения и одно.- вычитание для отыскания начального .приближения; -две .операции умножения и операция вычитания для реализации одной итерации. Количество итераций зависит от необходимой точности и, например, для обеспечения точности вычислений с 16-ю двоичными разрядами ( 1,510 ) требуется две итерации. С учетом этих итераций дли получения указанной точности необходимо шесть операций умножения и шесть операций вычитания. В предлагаемом устройстве для реализации деления при аппроксимации - на интервале i/2; ij полиномами 2-й степени требуется 3 умножения и 2 сложения, (для обеспечеш1Я точности 16 дв. разрядов исходный интервал делителя на 16 подин тер ват о в, общее количество коэффициентов 48), при ;шпроксимации полиномами 1-и степени требуется 2 операции умножения и одно сложение (при той же точности колич-ество разбиений -64, число запоминаемых коэффициентов 128). Быстродействие реализации операции деления возрастает почти в 2 раза для первого и в 3 раза для второго случая соответственно. Максимальная методическая погрешность приведенного кусочно-полиномиального приближения с равномерной нормой значительно меньше требуемой ,55.10-5 л..Ю-5

Формула изобретения

Устройство для деления, содержащее регистры делимого, целителя и частного блок формирования и суммирования частичных произведений и блок управления, причем выходы регистра делимого подключены к первой группе входов блока ф рмирования и суммирования частичных произведений, выходы блока формирования и суммирования частичных произведений подключены к входам регистра частного, отличающееся тем, что, с целью повышения быстродействия, в устройство введены дешифратор и блок односторонней памяти, входы которой соединены с выходами дешифратору , входы которого подключены к выходам старших разрядов ре-

гистра делителя, выходы регистра делителя подключены ко второй группе входов блока формирования и суммирования частичных произведений, третья группа входов Которого соединена с выходами блока односторонней памяти, управляющие входы односторонней памяти и блсжа формирования и суммирования частичных произведений подключены к выходам блока управления.

Источники информации, принятые во Ы1имание при экспертизе

1. Карцев Jt. А, Арифметика цифровых машин. М., Наука, 1969, с 532-536.

2. Авторское свидетельство СССР №305475, кл. Q Об Р 7/52, 1969 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Конвейерное устройство для деления интерационного типа | 1984 |

|

SU1179321A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| УСТРОЙСТВО ДЕЛЕНИЯ И ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ | 2012 |

|

RU2510072C1 |

| Устройство для деления | 1975 |

|

SU602944A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Вычислительное устройство | 1988 |

|

SU1532917A1 |

| УСТРОЙСТВО ДЛЯ ОСНОВНОГО ДЕЛЕНИЯ МОДУЛЯРНЫХ ЧИСЕЛ | 2013 |

|

RU2559771C2 |

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018934C1 |

Авторы

Даты

1980-05-05—Публикация

1977-12-20—Подача