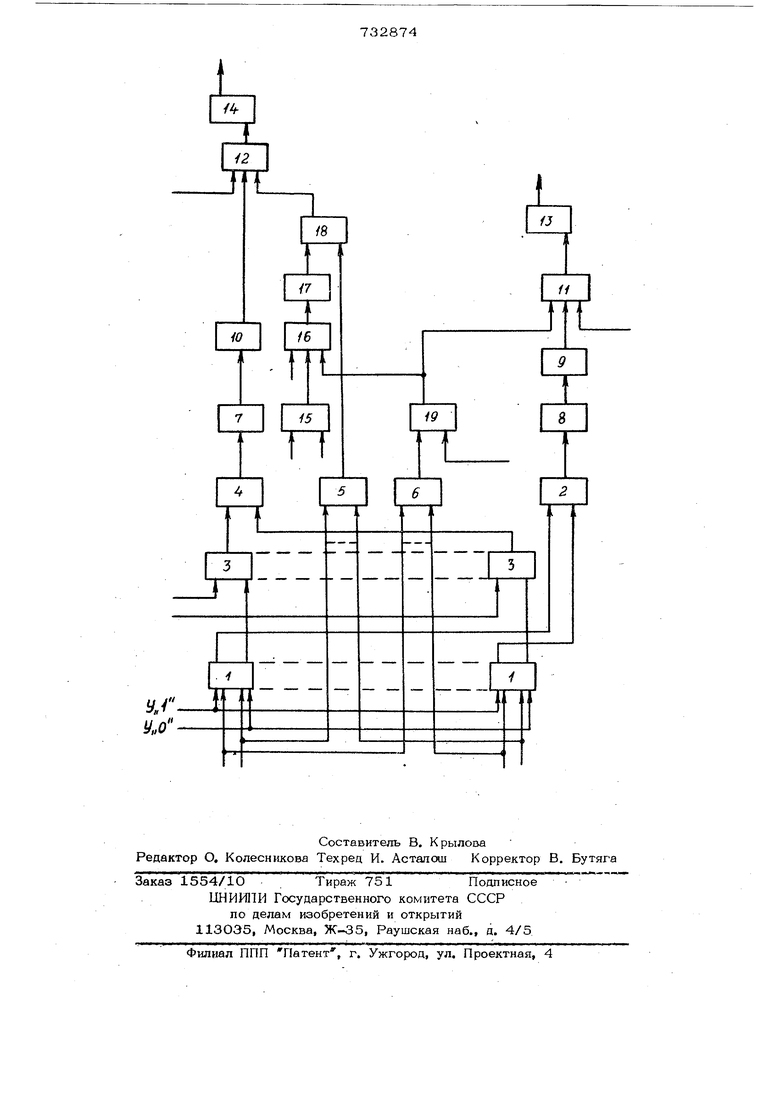

Изобретение относится к вычислительной технике и может быть использовано при проектировании цифровых устройств. Известно устройство для контроля микропрограммного автомата, содержащее элементы И, ИЛИ, НЕ, которое может быть использовано для контроля регистра fl. Недостатком указанного устройства является малая эффективность контроля работающих схем. Кроме того, в устройстве результат контроля представляется в обобщенном виде (работает или не работает устройство), без указания на конкретный вид отказа. Наиболее близким техническим к данному изобретению является устройство для контроля регистра, содержащее группу элементов И, элементы И, НЕ, триггеры, первый элемент ИЛИ; выход которого соединен с нулевым входом первого триггера, единичный выход которого соединен с первым входом первого элемента И, выход первого элемента И соединен с нулевым входом второго триггера, выход которого яшляется первым выходом устройст- ва 2. Однако данное устройство обеспечивает контроль работы лишь по совокупности заранее известных сигналов, что не всегда возможно. Кроме того, в устройстве результат контроля определяет правильную или неправильную работу без конкретизации вида неисправности. Дель изобретения - повышение эффективности контроля. Поставленная цепь достигается тем, что в устройство введены второй элемент ИЛИ и два элемента задержки, причем нулевой и единичный входы контролируемого регистра является соответственно первым и вторым входами устройства, единичные входы разрядов контролируемого регистра соединены со входами первого элемента ИЛИ, нулевые входы разрядов контролируемого регистра соединены со входами второго элемента ИЛИ выход которого соединен с нулевым входом третьего триггера, нулевые выходы разрядов контролируемого регистра соединены со входами второго элемента И, выход которого через после- яовательно соединенные первый элемент НЕ и первый элемент задержки соединен со вторым входом первого элемента И, третий вход первого элемента И является третьим входом устройства, единичный вход первого триггера является четверты входом устройства единичные выходы раз рядов контролируемого регистра соедине- ны соответственно с первыми входами эл ментов И группы, вторые входы которых являются группой входов устройства, а выходы соединены со входами третьего элемента И, выход которого через соединенные последовательно второй элемент НЕ и второй элемент задержки соединены с первым входом пятого элемента И, едини ный выход первого триггера соединен с первым входом шестого элемента И, вто- рой вход которого Соединен с единичныгу выходом четветого триггера, а третий вход является пятым входом устройства, единичный вход четвертого триггера явля ется шестым входом устройства, выход шестого элемента И через третий элемен НЕ соединен с единичным входом третьего триггера, единичный выход которого соединен со вторым входом элемента И, третий вход пятого элемента И является седьмым входом устройства, выход пятого элемента И соединен с единичным вхо дом пятого триггера, выход которого является вторым выходом y9frpoйcтвa. На чертеже приведена функциональтшя схема устройства. Схема устройства содержит регистр 1, выходы разрядов которого соединены со вхо дами элемента И 2 и через группу элементов И 3 со входами элемента И 4. Входы регистра 1 являются входами устройства и соединены со входами элементов ИЛИ 5 и ИЛИ 6. Вторые входы группы элементов И 3 являются группой входов устройства. Выходы элементов И .2 и 4 соответственно соединены с элементами НЕ 7 и 8 и далее через элементы задержки 9 и 10 с элементами И 11 и И 12. Оба элемента И 11 и 12 своими выходами соединены с триггерами 13 и 14.Кроме того, в состав устройства входит триггер 15, соединенный выходом со входом элемента И 16 и далее через элемент НЕ 17 со вхо- 55 дом триггера 18 и предназначенный для разрешения контроля по . В устройство входит также триггер 19 для разрешения контроля по О. Триггеры 18 и 19 соединены своими выходами со входами соответственно элементов И 12 и 11. Устройство работает следующим образом. Разряды контролируемого регистра 1 в произвольные моменты находятся в положении О или каждый, причем каждый разряд имеет раздельные входы по I и О, кроме того, в регистре есть общие установы и О Контроль правильности срабатывания регистра осуществляется в тот момент, когда все разряды регистра находятся одновременно в положении О, Для подключены устройства к контролируемому регистру не чаще одного раза в определенный отрезок времени используется триггер 15, на единичный вход которого поступает импульс метки времени (например О,1 Гя, если требуется производить контроль не чаще одного раза в 10 с). Единичный выход триггера 15, соединенный с одним из входов элемента И 16, после поступления метки времени позволяет проход через элемент И 16 импульса начала контроля, поступающего на вход элемента И 16, при условии, что на вход элемента И 16, соединенный с единичным выходом триггера 19, подан разрешающий сигнал, который образуется при поступлении на единичный вход триггера 19 импульса сброса перед началом контроля. Импульс начала контроля, пройдя через элемент И 16 и элемент НЕ 17, переводит в единичное состояние триггер 18. Тем самым подается разрешающий потенциал на один из входов элемента И 12. В следующий момент все разряды регистра устанавливаются в единичное состояние по обшей щине установа 1 (У 1). Если все разряды регистра правильно перешли в единичное состояние, то на выходе элемента И 4, соединенного своими входами через группу элементов И 3 с единичными выходами разрядов регистра 1, образуется потенциал, который, пройдя через элемент НЕ 7 и элемент задержки 10, поCTjnaeT на второй вход элемента И 12, после чего на вход элемента И 12 поступает анализирующий импульс, проверяющий правшьность установа регистра в 1. Если все разряды регистра 1 сработали правильно, то анализирующий импульс не проходит через элемент И 12, а если хотя бы один из разрядов регистра 1 не сработал, то анализирующий импульс проходит через элемент И 12 и переключает гер 14, на единичном вьсходе которого 573 появляется потевдиал, сообщающий о неис правности регистра при переходе от О к . Если во время контроля по на нулевой вход любого разряда регистра 1 приходит одна или более 1 по раздельным входам, то данная единица проходит через элемент ИЛИ 5 и сбрасывает триггер 18, При этом контроль прекращается и вес регистр 1 устанавливается в О по входу общего установа О. Если во время контроля регистра 1 на единичный вход любого разряда приходит одна или более единиц по раздельным входам, то данная единица не останавливает контроля, а для того, чтобы она не потерялась, длительность импульсоВ| единиц, поступающих по раздельным входам, должна быть в несколько раз больше во времени, необходимом для прекращения контроля и перевода регистра в О. Описанная проверка правильности сраб тывания регистра 1 производится при наличии на вторых входах группы элементов И 3 разрешающих потенциалов. Эта группа входов устройства может использовать ся для одновременного контроля двух регистров, если оба эти регистра одновреме но находятся в единичном состоянии. Аналогично производится контроль пра вильности срабатывания разрядов регистра 1 при переходе от к О и аналогично прекращается при поступлении импульса 1 по одному или более из раздельных единичных входов разрядов регистра 1 с помощью триггера 19, Резуль таты неправильного срабатывания разрядов регистра в 1 при переходе из в О появляются в виде сигнала на единичном выходе триггера 13 после поступ ления анализирующего импульса на вход элемента И 11, Положительный эффект от использован изобретения обусловлен наличием раздель ных узлов, контролирующих правильность срабатывания регистра по О и 1, что позволяет уточнить вид неисправности в отличие от известньк устройств. изобретения Формула Устройство для контроля регистра, содержащее группу элементов И, элементы И и НЕ, триггеры, первый элемент ИЛИ, выход которого соединен с нулевым входом первого триггера единичный выход к торого соединен с первым входом первог элемента И, выход первого элемента И 4 соединен с нулевым входом второго триггера, выход которого является первым выходом устройства, от л и чающееся тем, что, с целью повышения эффективности контроля в устройство введены второй элемент ИЛИ и два элемента задержки, причем нулевой и единичный входы контролируемого регистра являются соответственно первым и вторым входами устройства, единичные входы разрядов контролируемого регистра соединены со входами первого элемента ИЛИ, нулевые входы разрядов контролируемого регистра соединены со входами второго элемента ИЛИ, выход которого соединен с нулевым входом третьего триггера, нулевые выходы разрядов контролируемого регистра соединены со входами второго элемента И, выход которого через последовательно соединенные первый элемент НЕ и первый элемент задержки соединен со вторым входом первого элемента И, третий вход первого элемента И является третьим входом устройства, единичный вход первого триггера является четвертым входом устройства, единичные выходы разрядов контролируемого регистра соединены соответственно с первыми входами элементов И группы, вторые входы которых являются группой входов устройства, а выходы соединены со входами третьего элемента И, выход которого через соединенные последовательно второй элемент НЕ и второй элемент задержки соединены с первым входом пятого элемента И, единичный выход первого триггера соединен с первым входом шестого элемента И, второй вход которого соединен с единичным выходом четвертого триггера, а третий вход является пятым входом устройства, единичный вход четвертого триггера является шестым входом устройства, выход шестого элемента И через третий элемент НЕ соединен с единичным входом третьего триггера, единичный выход которого соединен со вторым входом пятого элемента И, третий вход пятого элемента И является седьмым входом устройства, выход пятого элема1та И соединен с единичным входом пятого триггера, выход которого является вторым выходом устройства. Источники инфомации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 357564, кл, Q 06 F 11/О8, 197О, 2,Авторское свидетельство СССР № 357563, кл. G 06 F 11/10, 1970 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема и обработки информации в многорегистровых кодах | 1982 |

|

SU1049951A1 |

| Устройство для управления ленточным перфоратором | 1981 |

|

SU970402A1 |

| Многоканальное устройство обегающего контроля | 1982 |

|

SU1087964A1 |

| Устройство для контроля срабатывания клавиш наборного поля | 1986 |

|

SU1432524A1 |

| Устройство для преобразования кодов | 1983 |

|

SU1131033A1 |

| Устройство для контроля управляющих сигналов интерфейса | 1984 |

|

SU1215111A1 |

| Устройство для контроля памяти | 1981 |

|

SU985831A1 |

| Устройство для тестовой проверки узлов контроля каналов ввода-вывода | 1979 |

|

SU922752A1 |

| Устройство для управления процессом передачи сигналов управления в иерархической автоматизированной системе управления | 1988 |

|

SU1525679A2 |

| Устройство для идентификации паролей пользователей | 1987 |

|

SU1564608A1 |

Авторы

Даты

1980-05-05—Публикация

1976-11-26—Подача