Изобретение относится к вычислительной технике и может быть использовано для оперативного контроля управляющих сигналов дискретных аппаратных интерфейсов.

Цель изобретения - повышение достоверности контроля.

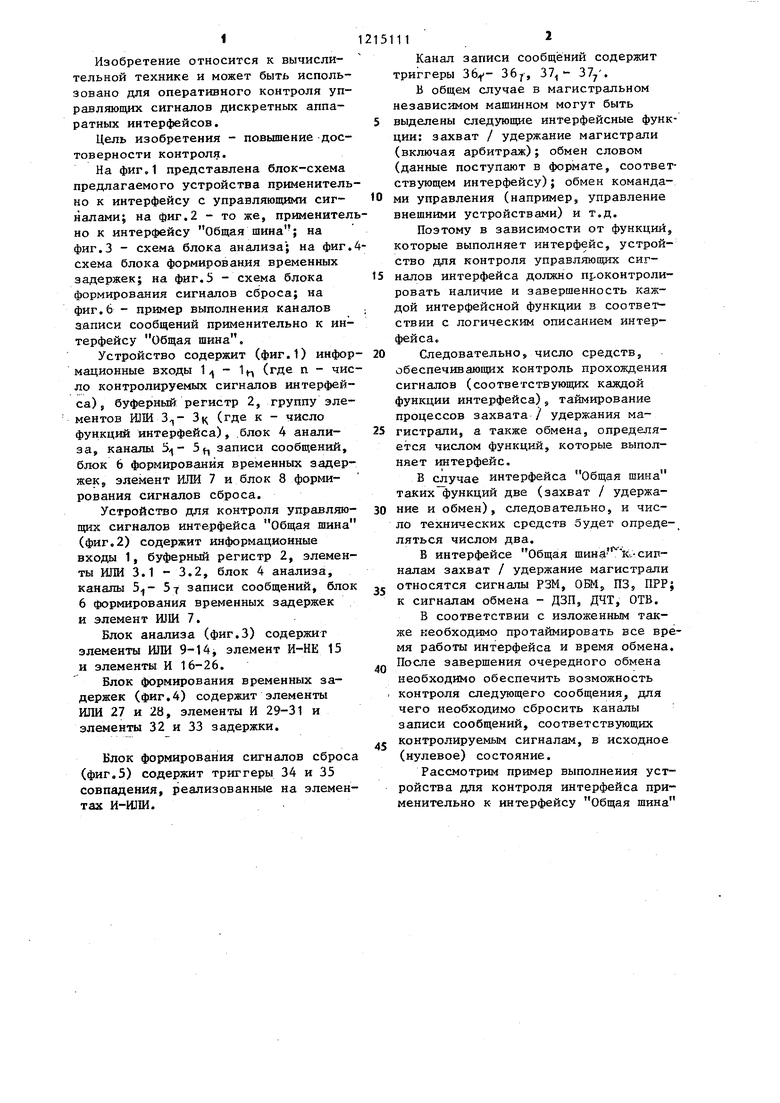

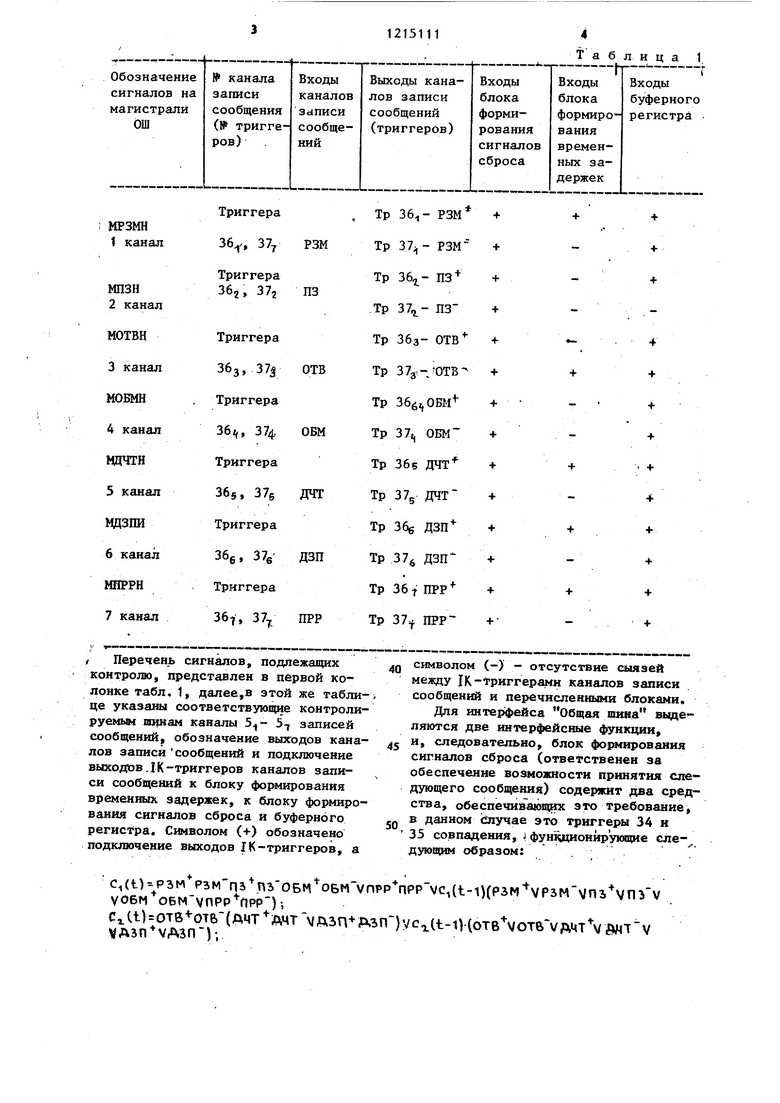

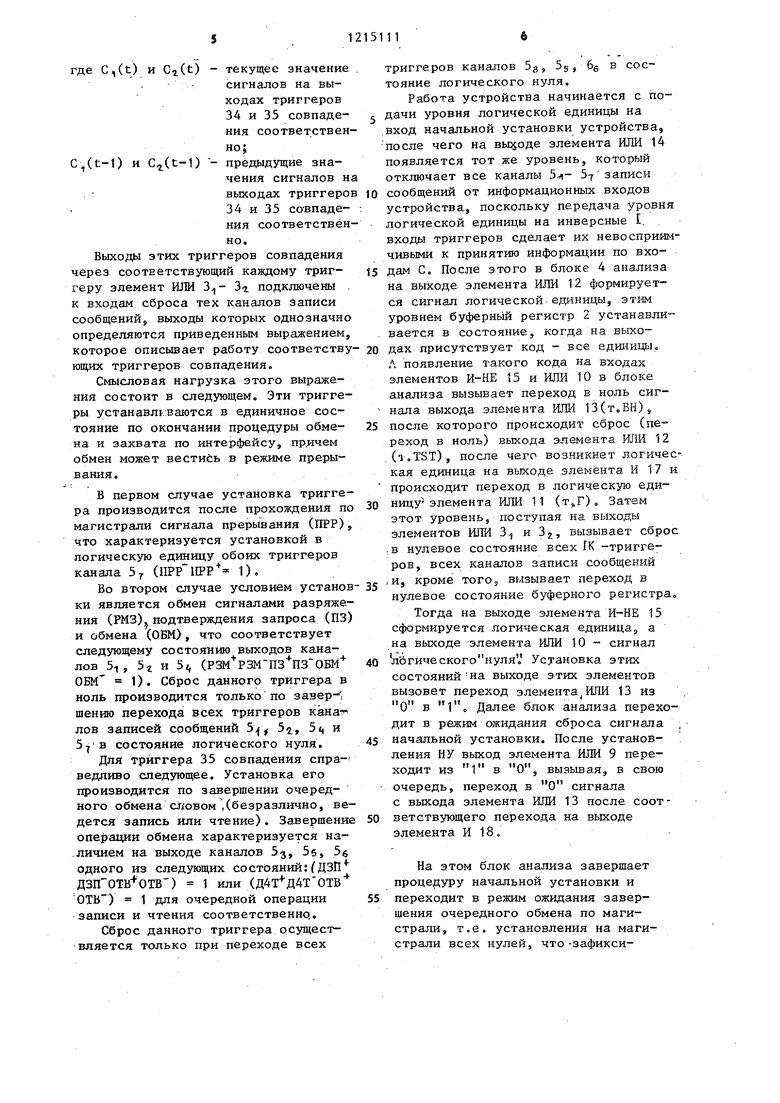

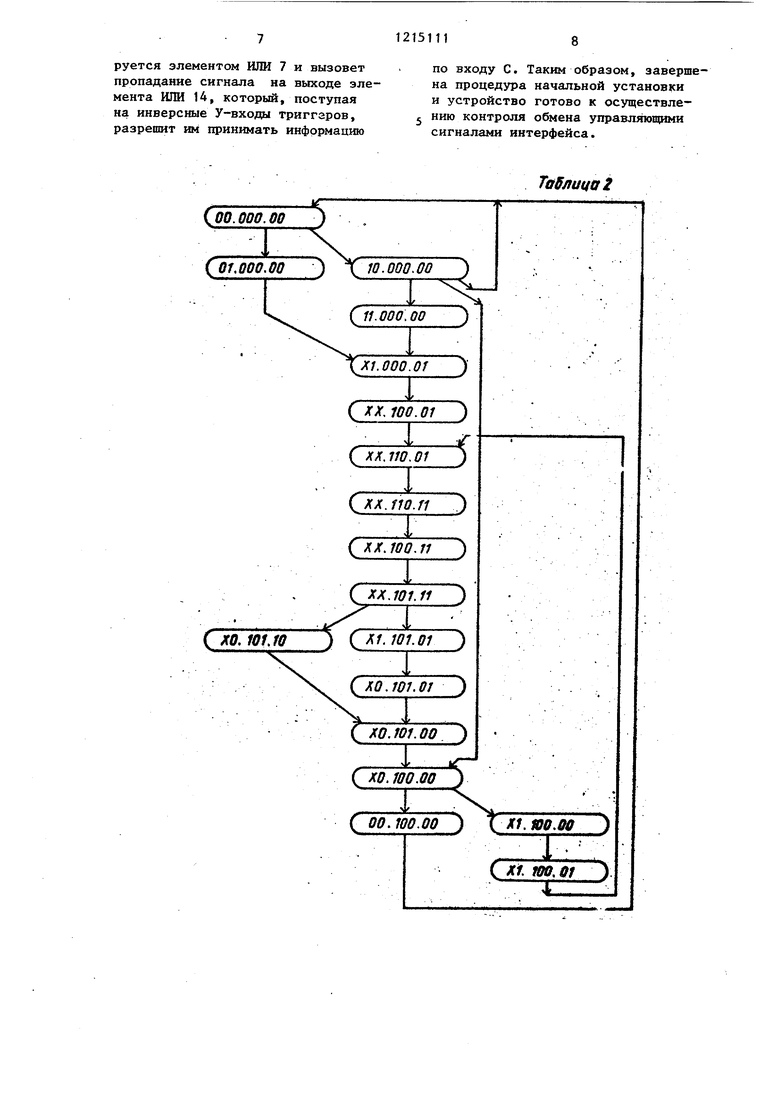

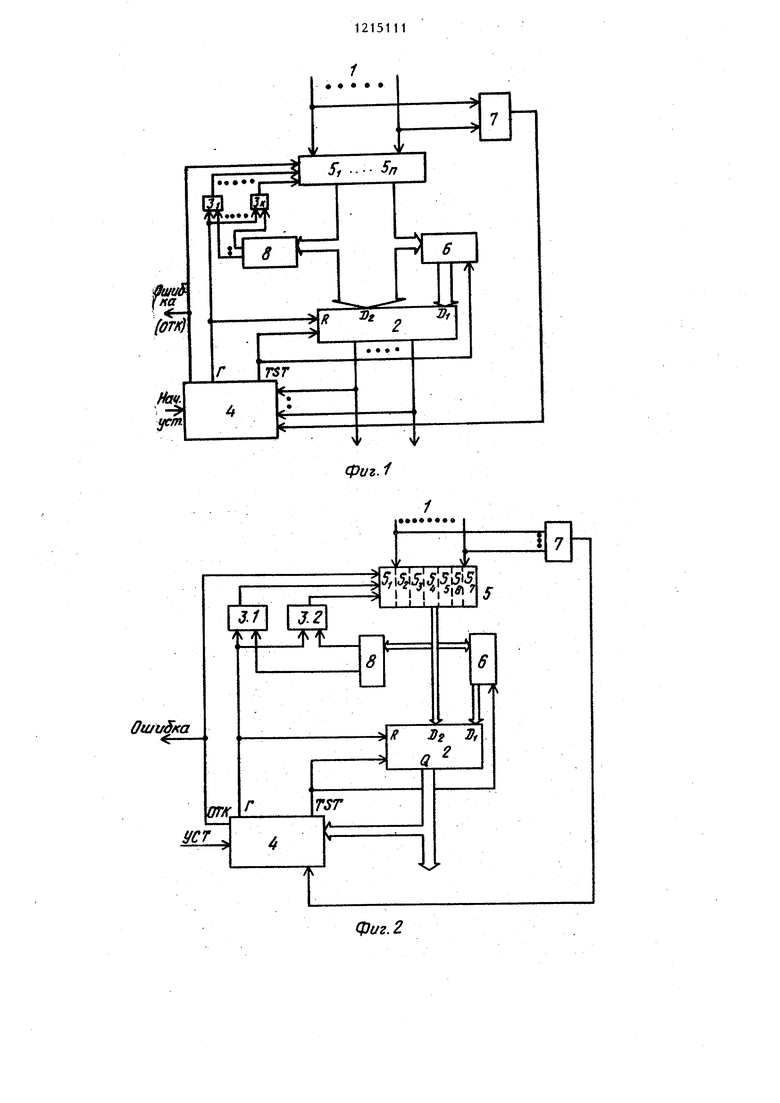

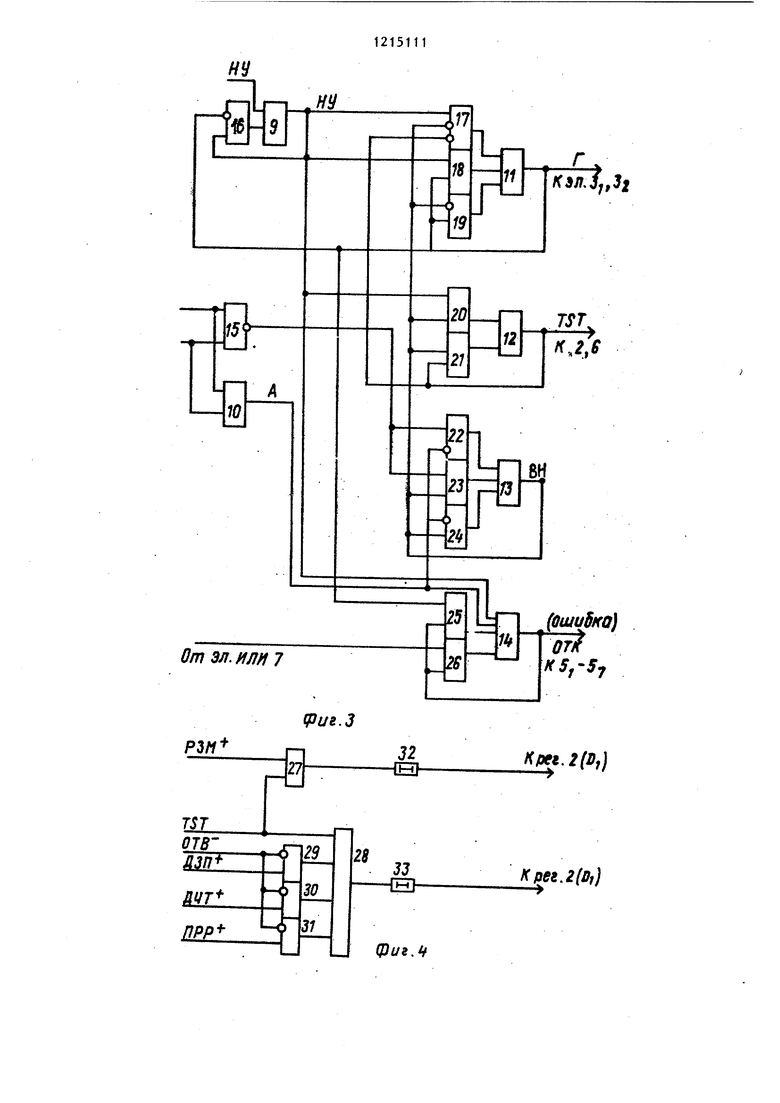

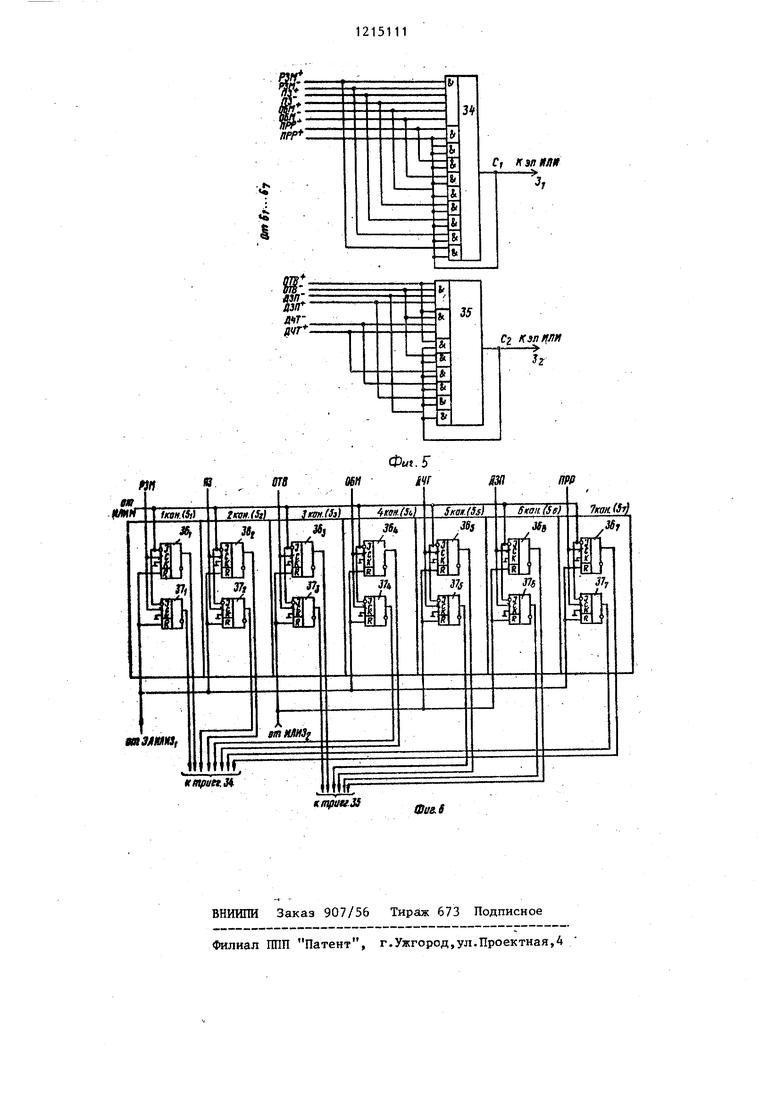

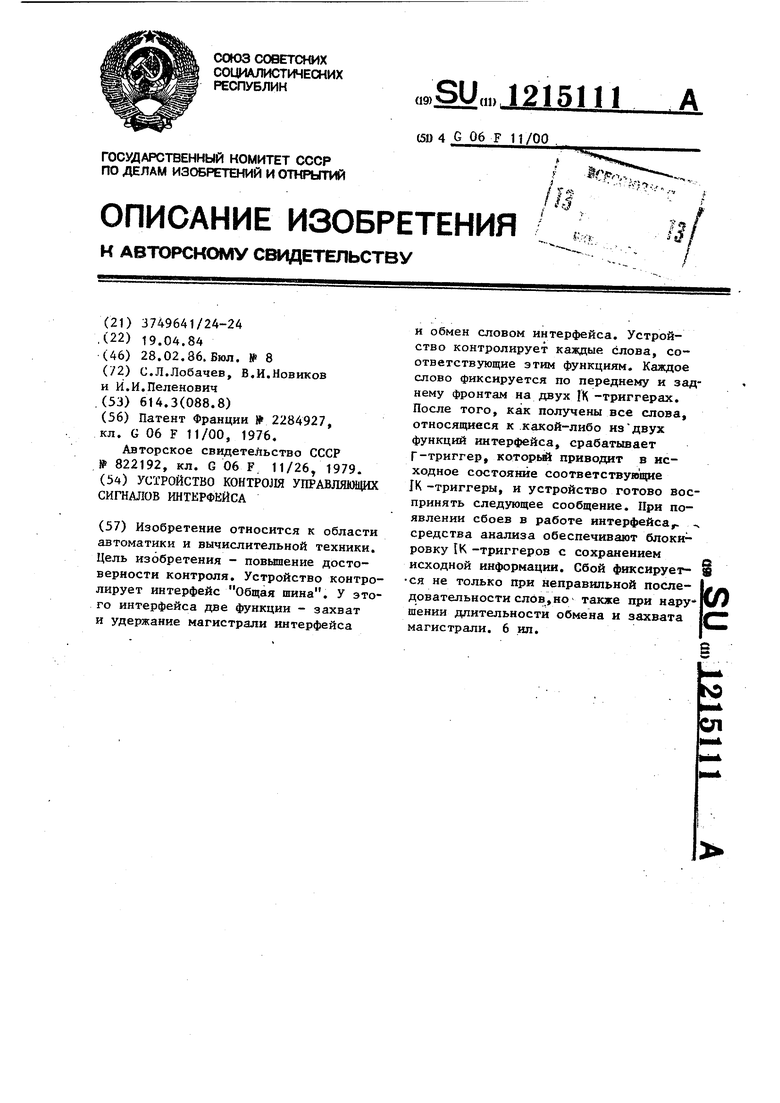

На фиг.1 представлена блок-схема предлагаемого устройства применительно к интерфейсу с управляющими сигналами; на фиг.2 - то же, применително к интерфейсу Общая на фиг.З - схема блока анализа; на фиг. схема блока формирования временных задержек; на фиг.З - схема блока формирования сигналов сброса; на фиг.6 - пример выполнения каналов записи сообщений применительно к интерфейсу Общая шина.

Устройство содержит (фиг.1) информационные входы ц - 1ц (где п - число контролируемых сигналов интерфейса) , буферный регистр 2, группу элементов ШШ 3ц (где к - число функций интерфейса), .блок 4 анализа, каналы 5-j- 5 записи сообщений, блок 6 формирования временных задержек, элемент ИЛИ 7 и блок 8 формирования сигналов сброса.

Устройство для контроля управляющих сигналов интерфейса Общая шииа (фиг,2) содержит информационные входы 1, буферный регистр 2, элементы ИЛИ 3.1 - 3.2, блок 4 анализа, каналы 5 т записи сообщений, блок 6 Зюрмирования временных задержек и элемент ИЛИ 7.

Блок анализа (фиг.З) содержит элементы ИЛИ 9-14, элемент И-НЕ 15 и элементы И 16-26.

Блок формирования временных задержек (фиг.4) содержит элементы ШШ 27 и 28, элементы И 29-31 и элементы 32 и 33 задержки.

Блок формирования сигналов сброса (фиг,5) соде;ржит триггеры 34 и 35 совпадения, реализованные на элементах И-ИЛИ.

151112

Канал записи сообщений содержит триггеры Збу- 36, .

В общем случае в магистральном независимом машинном могут быть

5 выделены следующие интерфейсные функции: захват / удержание магистрали (включая арбитраж); обмен словом (данные поступают в формате, соответствующем интерфейсу); обмен команда0 ми управления (например, управление внешними устройствами) и т.д.

Поэтому в зависимости от функций, которые выполняет интерфейс, устройство дпя контроля управляющих сиг5 налов интерфейса должно проконтролировать наличие и завершенность каждой интерфейсной функции в соответствии с логическим описанием интерфейса.

0 Следовательно, число средств, обеспечивающих контроль прохождения сигналов (соответствующих каждой функции интерфейса), таймирование процессов захвата / удержания ма5 гистрали, а также обмена, определяется числом функций, которые выполняет интерфейс,

В случае интерфейса Общая шина таких функций две (захват / удержа0 ние и обмен), следовательно, и число технических средств будет определяться числом два.

В интерфейсе Общая шина К -сип- налам захват / удержание магистрали

J относятся сигналы РЗМ, ОШ, ПЗ, ПРР; к сигналам обмена - ДЗП, ДЧТ, ОТВ.

В соответствии с изложенным также необходимо протаймировать все время работы интерфейса и время обмена. После завершения очередного обмена необходимо обеспечить возможность . контроля следующего сообщения для чего необходимо сбросить каналы записи сообщений, соответствующих

j контролируемым сигналам, в исходное (нулевое) состояние.

Рассмотрим пример выполнения устройства для контроля интерфейса применительно к интерфейсу Общая шина

0

, Перечень сигналов, подлежащих KOHTpojBo, представлен в первой колонке табл. 1, далее,в этой же таблице указаны соответствующие контролируемым шинам каналы 5-; записей сообщений, обозначение выходов каналов записи сообщений и подключение выходов.К-триггеров каналов записи сообщений к блоку формирования временных задержек, к блоку формирования сигналов сброса и буферного регистра. Символом (+) обозначено подключение выходов J К-триггеров, а

C,(t)-P3MV3M n3 n3 OBH 06M VnPP nPP VC,{t-l)(P3M VP3M Vn5 Vn3 V V06M 06M vnPP dPP )-,

(A4T A4T vA3n A3n )yc(t-lV(OTB OTe VAMT AMT V VA3n VA3n );

Таблица 1

символом (-) - отсутствие сыязей между IK-триггерами каналов записи сообщений и перечисленными блоками.

Для интерфейса Общая шина вьще ляются две интерфейсные функции, и, следовательно, блок формирования сигналов сброса (ответственен за обеспечение возможности принятия следующего сообщения) содержит два средства, обеспечивающих зто требование, в данном (Случае это триггеры 34 к 35 совпадения, Jфункционирующие еле-, дующим образом: .

где C(t) и C7.(t) - текущее значение

сигналов на выходах триггеров 34 и 35 совпаде- ния соответственно;

C;,(t-1) и C(t-l) - предыдущие значения сигналов н выходах триггеро 34 и 35 со впаде- ния соответственно.

Выходы этих триггеров совпадения через соотнетствующий каждому триг- геру элемент ШТИ Зг подключены . к входам сброса тех каналов записи сообщений, выходы которых однозначно определяются приведенным выражением, которое описывает работу соответству ющих триггеров совпадения.

Смысловая нагрузка этого выражения состоит в следующем. Эти триггеры ycтaнaвл :вaютcя в единичное состояние по окончании процедуры обме- на и захвата по интерфейсу, пр.ичем обмен может вестись в режиме прерывания.

В первом случае установка триггера производится после прохождения по магистрали сигнала прерывания (ПРР), что характеризуется установкой в логическую единицу обоих триггеров канала 5-f (ПРР 11РР 1),

Во втором случае условием уставов ки является обмен сигналами разряжения (РМЗ) подтверждения запроса (ПЗ) и обмена (ОБМ), что соответствует следующему состоянию выходов каналов 5i , 5г и 5/, (РЗМ РЗМ ПЗ ПЗ ОБМ ОБМ 1). Сброс данного триггера в ноль производится только по завер- шению перехода всех триггеров канаг лов записей сообщений S З., Зц и состояние логического нуля.

Для триггера 33 совпадения сира- ведливо следующее. Установка его производится по завершении очередного обмена CJXOBOM .(безразлично, ведется запись или чтение). Завершение операции обмена характеризуется на- .личие:м на выходе каналов 5з, Зб, 3 одного из следующих состояний:(ДЗП ) 1 или (Д4Т Д4Т ОТБ ОТВ) 1 для очередной операции записи и чтения соответственно..

Сброс данного триггера осуществляется только при переходе всех

триггеров каналов Зд, Зз, 6б в состояние логического нуля.

Работа устройства начинается с подачи уровня логической единицы на вход начальной установки устройства, после чего на элемента ИЛИ 14 появляется тот же уровень, который отключает все каналы 37 записи сообщений от информационных входов устройства, поскольку передача уровн логической единицы на инверсные L входы триггеров сделает их невосприичивыми к принятию информации по входам С. После этого в блоке 4 анализа на выходе элемента ИЛИ 12 формируется сигнал логической-единицы, этим уровнем буферньш регистр 2 устанавливается в состояние, когда на выходах присутствует код - все единицы, Л появление такого кода на входах элементов И-НЕ 13 и ИЛИ 10 в блоке анализа вызывает переход в ноль сигнала выхода элемента ИЖ (т.ВН), после которого происходит сброс (переход в ноль) выхода элемента ИЛИ 12 .(i.TST), после чего возникнет логичекая единица на выходе элемента Е 17 происходит переход в логическую единицу- элемента ИЛИ 11 (т,Г). Затем этот уровень, поступая на выходы элементов ИЛИ 3 и 3, вызывает сбро ,в нулевое состояние всех IK -триггеров, всех каналов записи сообщений ,и, кроме TorOs вызывает переход в нулевое состояние буферного регистра

Тогда на выходе элемента И-НЕ 13 сформируется логическая единица, а на выходе элемента ИЛИ 10 сигнал лЬгйческого нуля . Установка этих состояний на выходе этих элементов вызовет переход элемента ИЛИ 13 из О в Г о Далее блок анализа переходит в режим ожидания сброса сигнала начальной установки. После установления НУ выход элемента ИЖ 9 переходит из 1 в О, вызывая, в свою очередь, переход в О сигнала с выхода элемента ИЖ 13 после соответствующего перехода на выходе элемента И 18„

На этом блок анализа завершает процедуру начальной установки и переходит в режим ожидания завершения очередного обмена по магистрали, т.е. установления на магистрали всех нулей, что -зафиксируется элементом ИЛИ 7 и вызовет пропадание сигнала на выходе элемента ШШ 14, который, поступая на инверсные У-входы триггеров, разрешит им принимать информацию

(00.000.00 )

т ,

(01.000.00 j 10.000.00 )

по входу С. Таким образом, завершена процедура начальной установки и устройство готово к осуществле- нию контроля обмена управляющими сигналами интерфейса.

Твблицо2

(11. }

XI. 000. о J }

( XX, 100 01 )

zzii:

(х.т 01)

;

(XX.flOfl 3

( л/. 100.11 3

г

( XX.101.11 J

с хо. 101JO

(Л1.101.01 }

с xo.wj.

с xo.roi.oo)

с XD.JOO.QO J

с оо.юо.оо 3 с дгу.ят.ду )

i

С/у/. fjgg.r П

Диаграмма табл. 2 описывает I работу блока анализа для следующего множества точек блока анализа: А, НУ, ОТК, TST, Г, ВН, ТНУ в. данной последовательности. Символом X обозначены значения переменных из данного множества, которые безразличны в определенных состояниях представленной диаграммы. Качест- во работы соответствует ситуации 00.0000.00. Появление 1 на выходе элемента 32 задержки свидетельствует о превышении времени обмена максимально допустимого времени обмена по магистрали данного сообщения.

Появление 1 на выходе элемента 33 задержки свидетельствует о превыз Рзп прр прр обпУлмт: лзп ут$ту

Sa TSTvOBM CPi P3 ot6 OT6 (A4T A4T Vr 5n A3n )

30

Ss TSTVOT6 P3M( АЧТ ЛЧТ-ПРР-ПРР ОТ&);

S;,TST /P5Mp3M VnPP npP ,Ss элемент 32 задержки,

Sft элемент 33 задержки, i Наличие в буферном регистре хотя бы одного разряда в состоянии логической 1 приводит к установке этого уровня на выходе элемента ИЛИ 14 в блоке анализа, что вызовет отклонение устройства от шин Магистрали,, и сохранению информации об ошибке до прихода следукщего импульса начальной установки на вход элемента ШШ9.

35

менты ШШ, двенадцатый,тринадца и четырнадцатый элементы И и дв элемента задержки, блок формиро ния сигналов сброса содержит д триггера совпадения, каждый кан записи Сообщений - два триггер причем входы синхронизации перв и второго триггеров каждого кан записи сообщений соединены с со ветствующими шинами контролируем сигналов интерфейса, соеДинены входами первого элемента ИЖ и являются информационными входами устройства, входы сброса первого и второго триггеров первого, вто рого, четвертого и седьмого кана записи сообщений соединены с вых дом второго элемента.ИЛИ, входы сброса первого и второго триггер третьего, пятого и шестого канал записи сообщений соединены с вых дом третьего элемента ИЛИ, инверсные единичные входы первого и второго триггеров каждого кана записи сообщений - с выходом чет того элемента ИЛИ, выходом ошибк устройства и первыми входами пер вого и второго элемента И, нулев входы первого и второго триггеро всех каналов записи сообщений, п ключенных к шине нулевого потенц

Формула изобретена

Устройство контроля управляющих сигналов интерфейса, содержащее первый, второй и третий элементы ИЛИ и буферный регистр, причем выходы буферного регистра образуют группу информационных выходов устройства, отличающееся тем, что, с целью повьш1ения достоверности контроля, оно содержит блок формирования временных задержек, блок анализа, семь каналов записи сообщений, причем блок анализа содержит элемент И-НЕ, четвертый, пятый, шестой, седьмой, восьмой и девятый элементы ИЛИ и элементы И с первого по одиннадцатый, блок формирования временных задержек - десятый и одиннадцатый элешении максимально допустимого для интерфейса Общая шина времени на присутствии сигналов обмена на щинах интерфейса.

При возникновении сигнала (rTST) с выхода элемента ИЛИ 12 производится запуск элементов 32 и 33 задержки с целью установления разрядов буферного регистра 2 в состояние 1 в соответствии с выражениями SsjSg.

Сброс каждого разряда буферного регистра 2 происходит по сиг налам, которые формирует элемент ШШ 11 в блоке 4 анализа.

Установка каждого разряда буферного регистра 2, реализованного на Триггерах, происходит по законам:

менты ШШ, двенадцатый,тринадцатый и четырнадцатый элементы И и два элемента задержки, блок формирования сигналов сброса содержит два триггера совпадения, каждый канал записи Сообщений - два триггера, причем входы синхронизации первого и второго триггеров каждого канала записи сообщений соединены с соответствующими шинами контролируемых сигналов интерфейса, соеДинены с входами первого элемента ИЖ и являются информационными входами устройства, входы сброса первого и второго триггеров первого, второго, четвертого и седьмого каналов записи сообщений соединены с выходом второго элемента.ИЛИ, входы сброса первого и второго триггеров третьего, пятого и шестого каналов записи сообщений соединены с выходом третьего элемента ИЛИ, инверсные единичные входы первого и второго триггеров каждого канала записи сообщений - с выходом четвертого элемента ИЛИ, выходом ошибки устройства и первыми входами первого и второго элемента И, нулевые входы первого и второго триггеров всех каналов записи сообщений, подключенных к шине нулевого потенциала

устройства, выходы первого и второг триггеров первого, второго, четвертого и седьмого каналов записи сообщений соединены с информационными входами первого триггера совпадения информационные входы второго триггера совпадения соединены с выходами первого и второго триггеров третьего, пятого и каналов записи сообщений, выходы первого к второго триггеров совпадения соединены с первыми входами второго и .третьего элементов ИЛИ соответст- 1венно, выходы буферного регистра со динены с входами элемента И-НЕ и входами пятого элемента ИЛИ и образуют информационные выходы устройства, выход элемента И-НЕ соеди - нен с прямым входом третьего и первым входом четвертого элементов И, выход пятого элемента ИЛИ соединен с первым входом четвертого элемента ИЛИ и с инверсными входами третьего и пятого элемента И, выход шестого элемента ШШ соединен с вторым входом четвертого элемента И, прямым входом пятого элемента И, прямыми входами шестого и седьмого элементов И, первьм ин1версным входом восьмого элемента И и инверсным входом девятого элемента И, выход седьмого элемента ШШ соединен с входом установки буферного регистра и входом запуска блока формирования временных задержек, с вторым входом седьмого элемента И и вторым инверсным входом восьмого элемента И, выход восьмого элемента ИЛИ соединен с вторыми входами второго и третьего элементов ИЛИ, входом сброса буферного регистра, первым входом десятого элемента И, прямым входом девятого элемента И, ин- версньм входом одиннадцатого элемента И, вторым входом первого элемента И, первый вход девятого элемента ШШ соединен с входом начальной установки устройства, выход девятого элемента ШШ соединен с прямыми

входами восьмого и одиннадцатого элементов И, с вторьми входами шестого и десятого элементов И и с вторым входом четвертого элемента ШШ, второй вход второго элемента И соединен с выходам первого элемента ИЛИ, выхода первого и второго элементов И соединены с третьим 10 и четвертьм входами четвертого элемента ИЛИ, выходы третьего, четвертого и пятого элементов И соединены с входами шестого элемента ШШ, выхода шестого и седьмого элементов )5 И соединены с входами седьмого элемента ШШ, выходы восьмого, девятого и десятого элементов И соединены с входами восьмого элемента ИЛИ, выход одиннадцатого элемента И сое

20 динен с вторым входом десятого элемента ШШ, вход запуска блока формирования временных задержек соединен с первыми входами десятого и одиннадцатого элементов ИЛИ, второй

25 вход десятого элемента ШШ соединен с выходом первого триггера первого канала записи сообщения, инверсные входы двенадцатого, тринадцатого и четырнадцатого элементов И соединены

30 с выходом второго триггера третьего канала записи сообщений, вторые входы двенадцатого, тринадцатого и четырнадцатого элементов И соединены с выходами первых .триггеров пятого, шестого и седьмого каналов записи сообщений, выходы двенадцатого, тринадцатого и четырнадцатого элементов И соединены с BTOIM IM, третьим и четвертые входами одиннадQ цатого элемента ШП соответственно, выходы десятого и одиннадцатого элементов ШШ соединены соответственно через первый и второй элементы задержки с первой группой иифор мационных входов буферного регистра, вторая группа информа- ЦИО1ШЫХ входов которого соединена с выходами первых и вторых триггеров всех каналов записи сообщений.

5

5;.. 5)7 I

Щ J in

vrvk

Ошибка

I/SK

Ш1

TST

фиг.1

/

I l ffjlS

I I I

I I

R Sg Л

фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с абонентом | 1988 |

|

SU1615728A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С ВНЕШНИМ АБОНЕНТОМ | 1992 |

|

RU2084952C1 |

| Устройство для сопряжения двух ЭВМ | 1988 |

|

SU1596341A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1987 |

|

SU1439609A1 |

| Трехканальное резервированное запоминающее устройство | 1984 |

|

SU1215133A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Устройство для сопряжения канала ввода-вывода с абонентом | 1989 |

|

SU1695312A1 |

| Трехканальная резервированная микропроцессорная система | 1985 |

|

SU1378287A1 |

Изобретение относится к области автоматики и вычислительной техники. Цель изобретения - повышение достоверности контроля. Устройство контролирует интерфейс Общая шина. У этого интерфейса две функции - захват и удержание магистрали интерфейса и обмен словом интерфейса. Устройство контролирует каждые слова, соответствующие этим функциям. Каждое слово фиксируется по переднему и заднему фронтам на двух IK -триггерах. После того, как получены все слова, относящиеся к какой-либо из двух функций интерфейса, срабатывает Г-триггер, которьй приводит в исходное состояние соответствующие JK -триггеры, и устройство готово воспринять следующее сообщение. При появлении сбоев в работе интерфейса,. -s средства анализа обеспечивают блоки ровку IK -триггеров с сохранением исходной информации. Сбой фиксирует- i ся не только при неправильной последовательности слов, но также при шении длительности обмена и захвата магистрали. 6 ил.

| ПЕРЕДВИЖНОЙ ПОСТ МОЙКИ АВТОМОБИЛЕЙ | 2004 |

|

RU2284927C2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля интерфейса | 1979 |

|

SU822192A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-02-28—Публикация

1984-04-19—Подача