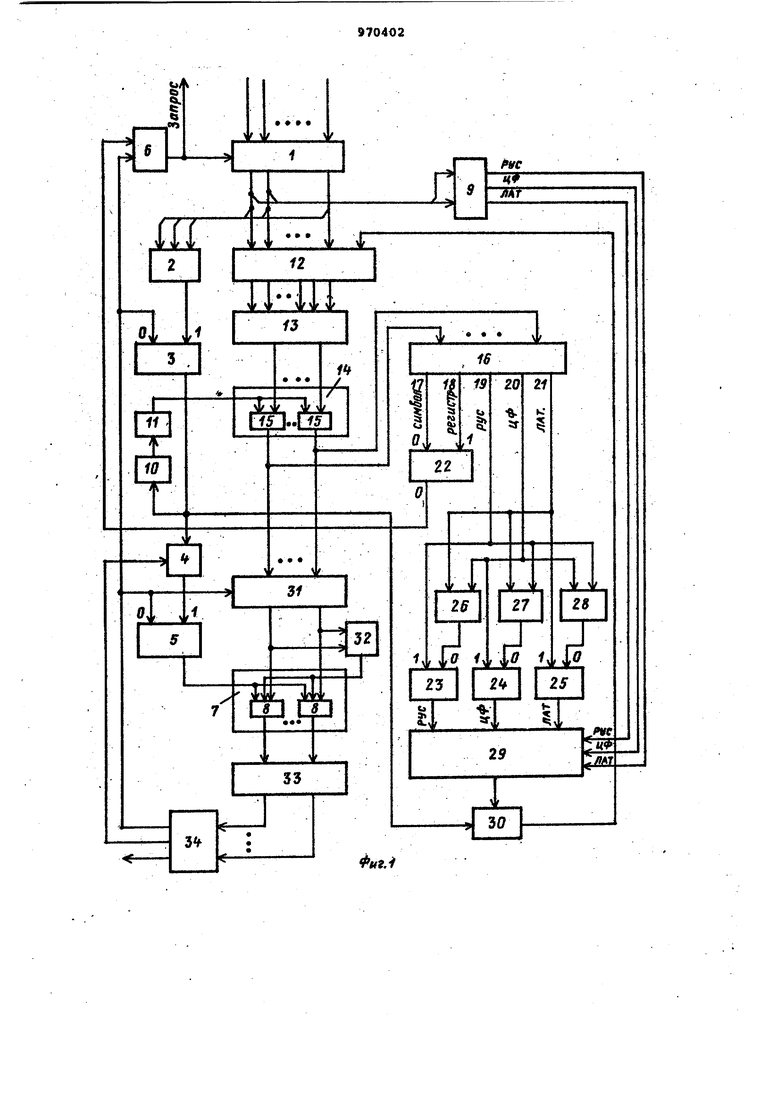

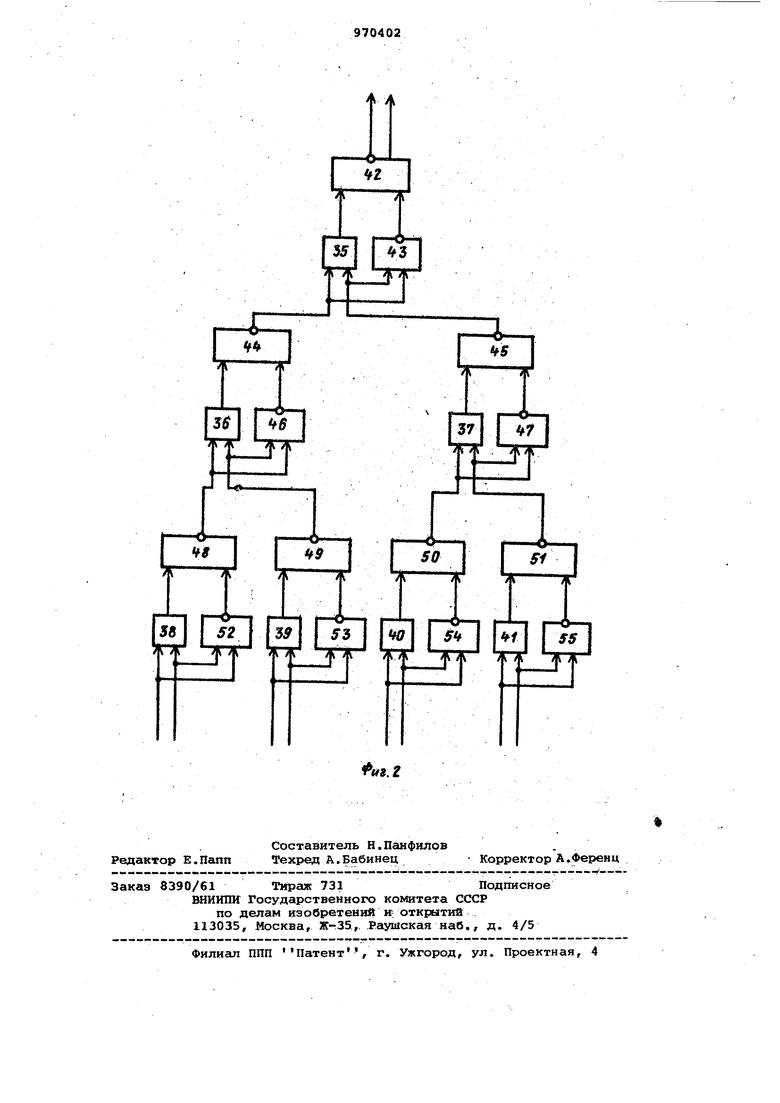

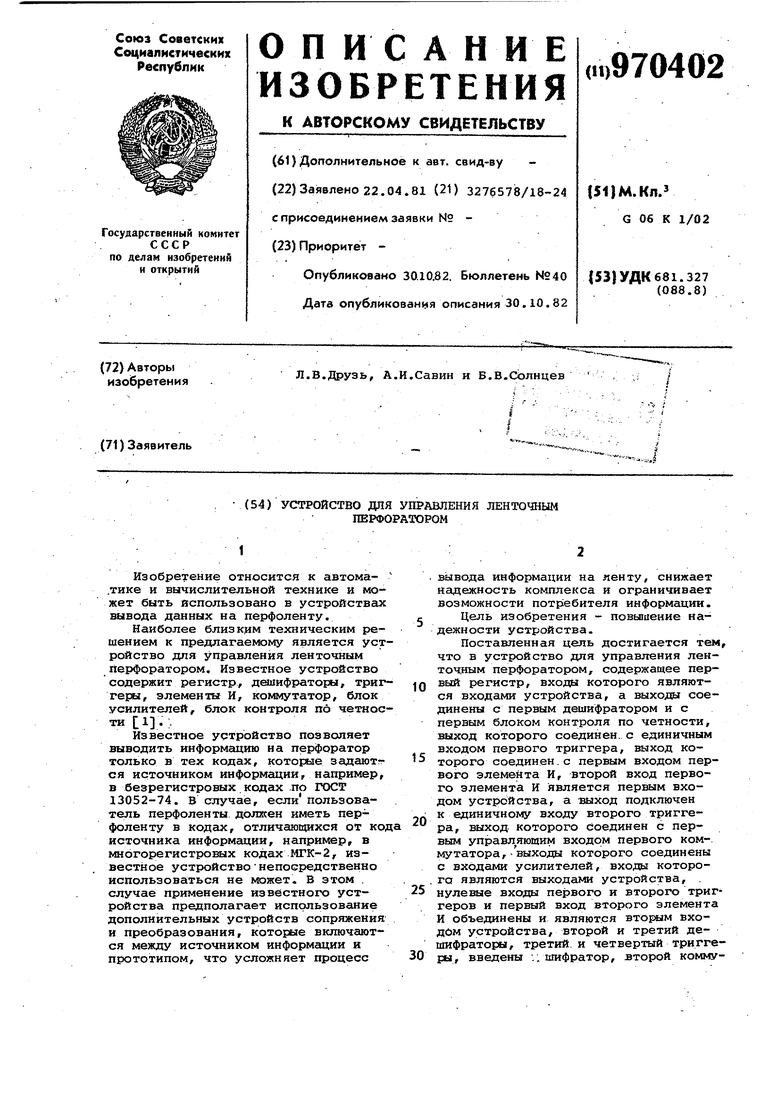

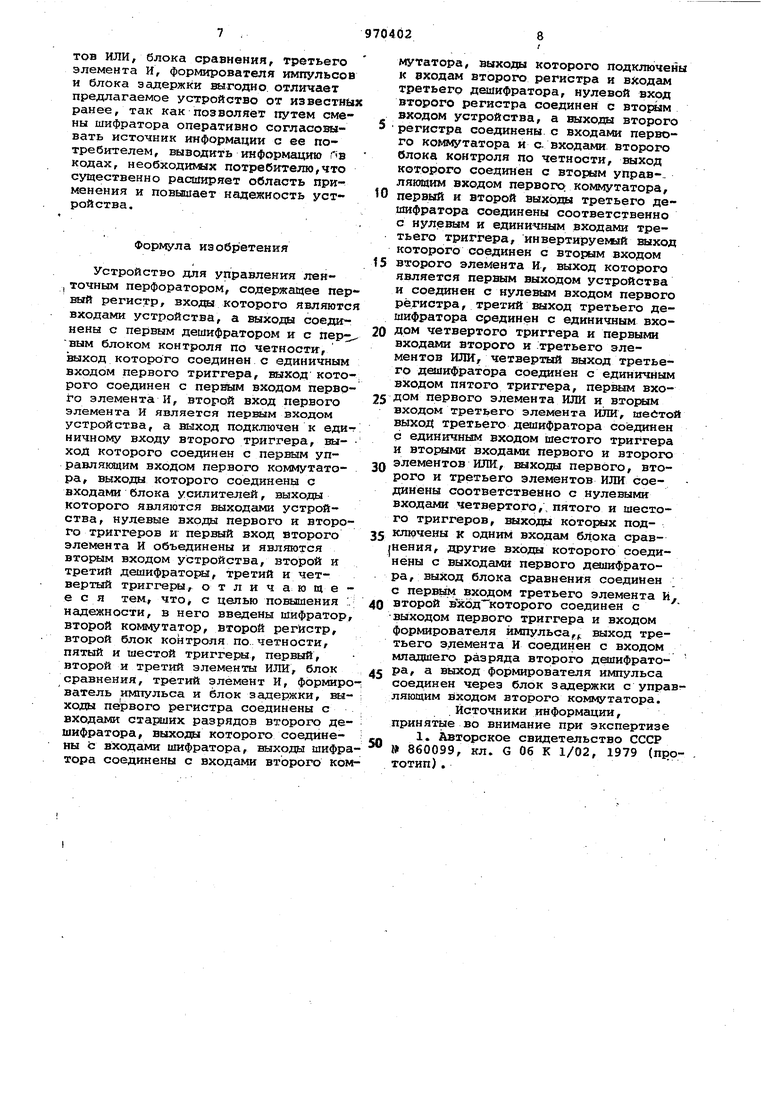

татор, второй регистр, второй блок контроля по четности пятый и шеетой тригге1«, первый, второй и третий элементы ИЛИ, блок сравнения, третий элемент И, формирователь импульса и блок задержки, выходы первого регистра соединены с входами старших разрядов второго дешифратора, выходы которого соединены с входами шифратора, выходы шифратора соединены с входами второго комм татора, выходы которого подключены к входам второго регистра и входам третьего дешифратора, нулевой вход второго регистра соединен с вторым входом устройства, а выходы второг регистра соединены с входа н первог коммутатора, и с входами второго бл ка контроля по четности, выход кото рого соединен с вторым управляющим входом первого коммутатора, первый и второй выходы третьего дешифратора соединены соответственно с нулевым и единичным входагли третьего триггера, инвертируемый выход которого соединен с вторым в содом второ го элеменх а И, выход которого является первым выходом устройства и соединен с нулевым входом первого регистра, третий выход третьего дешифратора соединен с единичным входом четвертого триггера и первыми входами второго и Tpeibero элементо ИЛИ, четвертый выход третьего дешиф тора соединен с единичным входом пятого триггера, первым входом первого элемента ИЛИ и вторым входом третьего элемента ИЛИ, шестой выход третьего дешифратора соединен с еди ничньам входом шестого триггера и вторыми входами первого и второго элементов ИЛИ, выходы первого, второго, третьего элементов ИЛИ соединены соответственно с нулевыми входами четвертого, пятого и шестого триггеров, выходы которых подключены к одним входам блока сравнени другие входы которого соединены с выходами первого дешифратора, выход блока сравнения соединен с пер вым входом третьего элемента И, второй вход которого соединен с выходом триггера и входом фор мирователя импульсов,выход третье го элемента И соединен с входом младшего разряда второго дешифрато ра, а выход формирователя импульса соединен череэ блок задержки с управляющим входом второго коммута тора. На фиг.1 приведена структурная электрическая схема устройства; на фиг.2 - функциональная схема блока контроля по четности. Устройство содержит первтлй регистр 1, первый блок 2 контроля по четности, первый триггер 3, первый элемент И 4, второй триггер 5, второй элемент И 6, первый коммутатор 7 с элементами И 8, первый дешиф- . ратор 9, формирователь 10 импульса у блок 11 задержки, второй дешифратор 12, шифратор 13, второй коммутатор 14, с элементами И 15, третий детпифратор 16 с.выходами 17-21, третий триггер 22, четвертый триггер 23, пятый триггер 24, шестой триггер 25, первый элемент ИЛИ 26, второй эле-, мент ИЛИ 27, третий элемент ИЛИ 28, блок 29 сравнения, третий элемент И 30, второй регистр 31, второй блок 32 контроля по четности,блок 33 усилителей, ленточный перфоратор 34, элементы И 35-41, элементы ШШ-НЕ 4255. Устройство работает следующим образом. Перед началом вывода информации на ленту включается перфоратор 34, который вырабатывает циклическую последовательность из трех синхроимпульсов СИ1, СИ2, СИЗ, обеспечивающих в каждом цикле запрос информации, пробивку.кода на ленте и .транспортирование ленты - сдвиг ее на один шаг. В каждом циклесинхроимпульс СИ1 обнуляет регистр 31 и триггеры 3 и 5. В исходном положении с нулевого выхода триггера 22 выдается разрешающий сигнал на второй вход элемента И б, при этом синхроимпульс СИ1 поступает через элемент. И б по шине запроса информации во внешнее устройство и обнуляет регистр 1. По запросу информации из внешнего устройства в регистр 1 поступает код символа, например, в беэрегистровом коде по ГОСТ 1305274. Рассматривается случай, когда потребитель информации использует ленту, отперфорированную в трехрегистровом ксэде МТК-2. Код входного символа из регистра 1 подается в блок 2 контроля по четности, на дешифратор 9 и на старшие разряды входов дешифратора 12. Дияифратор 9 преобразует значения шестого и седьмого разрядов входного символа по ГОСТ для определения его регистровой принадлежности, и выдает соответствующий сигнал русский тинский, цифра - на вторые входы блока 29 сравнения. Для первого входного символа предыдущий символ всегда отсутствует, триггеЕ 1 23-25 Находятся в нулевом состоянии, и, следовательно, на первых входах блока 29 сравнения нет входных сигналов. Поэтому блок сравнения не формирует выходной сигнал совпадения. В блоке контроля по четности 2 комбинация входного сигнала проверяется по четности и, при правильной четности сигналом с выхода блока 2 триггер 3 устанавливается в единичноесостояние. Потенциальный сигнал с выхода триггера 3 .подготавливает к открыванию элемент И 4, через элемент И 30 считывает.выходной сигнал блока 29 сравнения, и подается на формирователь 10 и myльca. При отсутствии илходного сигнала в блоке сравнения состояние младшего разряда кода адресного провода на входе демиф ратора 12 будет нулевым, чти соответствует .считыванию из шифратора 1 кода регистрового признака. Таким образом, на входах дешифратора 12 устанавливается код, соответствующий считыванию для данного входного символа кода регистрового признака. Декодированный дешифратором 12 сигнал с его выхода возбуждает соответствующий вход шифратора 13 и на его выходах формируется код регистрового признака, который поступает на коммутатор 14. Импульс с выхода формирователя 10 через блок 11 задержки, учитывающий время переходных процессов при сравнении регистровых признаков, считывает из коммутатора 14 код регистрового признака, который записывается в регистр 31 и подается на входы дешифратора 16. В дешифраторе 16 выходы 17 и 18 определяют соответственно шлвод из шифратора 13 или кода символа или кода регистрового признака, а выходы 19-21 формируют сигналы русский, цифра, латинский, соответствующие выведенному регистровому признаку. Таким образом, при выводе регистрового признака в дешифраторе 16 возбуждает ся выход 18 и один из выходов 19-21. При этом в единичное состояние устан вливается триггер 22, который закрывает элемент И 6, и соответствующий из триггеров 23-25, причем сигнал с одного из выходов 19-21 через соответствующие элементы ИЛИ 26-28 обнул ет соответственно два из трех тригге ров 23-25. Код регистрового признака поступает из регистра 31 на входы коммутатора 7 и блока 32 контроля по четности. При правильной четности кода блок 32 выдает сигнал, подготав ливакидий считывание этого кода из коммутатора 7. Синхроимпульсом СИ2 в данном цикле работы перфоратора 34 открывается элемент И 4 и устанавливается в единичное состояние триггер 5. Сигналом с выхода триггера 5 код регистрового признака считывается из коммутатора 7 и через блок 33. усилителей подается в перфоратор 34, где перфорируется, на ленте. Синхроим пульсом СИЗ перфоратора лента сдвига ется на один шап. В следующем цикле работы перфоратора 34 синхроимпульс СИ1 вновь обнуляет триггеры 3, 5 и регистр 31, однако не поступает на шину запроса инфоркйции и не обнуляет регистр 1, так как элемент И 6 закрыт. Поэтому по окончании действия этого импульса описанный выше процесс повторяется, так как регистр 1 сохраняет код символа, поступившего в предыдущем цикле. При этом на входах блока 29. сравнения теперь совпадают сигналы, соответствующие регистровым признакам, вследствие чего с его илхода считывается сигнал совпадения и сое.тояние младшего разряда дешифратора 12 становится единичным. В этом случае шифратор 13 формирует код символа в МТК-2, который описанным выше образом поступает через регистр 31, ком}.1утатор 7 и блок 33 усилителей на перфоратор 34. При выводе из шифратора 12 кода символа в дешифраторе 16 возбуждается только шлход 17, триггер 22 устанавливается в нулевое состояние, элемент И 6 подготавливается к открыванию в следующем цикле работы перфоратора и описанный выше процесс запроса информации и приема кода следующего символа в регистр 1 повторяется; Если регистровый признак следующего поступившего символа, определяег ой дешифратором 9, совпадает с . регистровым признаком предыдущего символа, хранящимся на одном из триггеров 23-25 блок 26 сравнения выдает сигнал совпадения и из шифратора 13 считывается код МТК-2 символа, который перфорируется на ленте перфоратора 34. Если же указанные регистровые признаки не совпадают, то, как это описано выше, сначала в одном цикле перфорируется код регистрового признака, а затем в другом цикле - код символа. В случае, если потребителю информации необходимо иметь перфоленту в кодах источника информации, производится замена шифратора 13, который для каждого входного кода содержит соответствующий код символа. В этом случае триггеры 23-25 постоянно обнулены, блок 29 сравнения постоянно выдает сигнал несовпадения, что однозначно в соответствии с кодом входного символа определяет адрес на входах шифратора 13. Дальнейшая работа устройства в этом случае аналогична описанному.выше. Введение в устройство для управления ленточным перфоратором шифратора, второго коммутатора, регистра, блока контроля по четности, пятого и шестого триггеров, трех элементов ИЛИ, блока сравнения, третьего элемента И, формирователя импульсов и блока задержки выгодно, отличает предлагаемое устройство от известны ранее, так как позволяет путем смены шифратора оперативно согласовывать источник информации с ее потребителем, выводить информацию пв кодах, необходиьых потребителю,что существенно расширяет область применения и повышает надежность устройства. Формула изобретения Устройство для управленигя лен,точным перфоратором, содержащее пер вый регистр, входы которого являютс входами устройства, а выходы соединены с первым дешифратором и с первым блоком контроля по четностк, шлход которого соединен с единичным входом первого триггера, выход кото рого соединен с первым входом перво го элемента И, второй вход первого элемента И является первым входом устройства, а выход подключен к еди ничному входу второго триггера, выход которого соединен с первым управляющим входом первого коммутатора выходы которого соединены с входами блока усилителей, выходы которого являются выходами устройства, нулевые входы первого и второ го триггеров и первый вход второго элемента И объединены и являются вторжлм входом устройства, з торой и третий дешифратора, третий и четвертый триггеры, отличающе еся тем, что с целью повышения надежности, в него введены шифратор второй коммутатор, второй регистр, второй блок контроля по., четности, пятый и шестой триггеры, первый, второй и третий элементы ШШ, блок сравнения, третий элемент И, формир ватель импульса и блок задержки, вы ходы первого регистра соединены с входами старших разрядов второго де шифратора, выходы которого соединены с входами шифратора, выходы шифр тора соединены с входами второго ко мутатора , выходы которого подключены к входам второго регистра и входам третьего дешифратора, нулевой вход второго регистра соединен с вторам входом устройства, а выходы второго регистра соединены с входами первого коммутатора и е входами второго блока контроля по четности, выход которого соединен с вторым управ-ляюшим входом первогс коммутатора, первый и второй выходы третьего дешифратора соединены соответственно с нулевым и единичным входами третьего триггера, инвертируемый выход которого соединен с вторым входом второго элемента И, выход которого является первым выходом устройства и соединен с нулевым входом первого регистра, третий выход третьего дешифратора срединен с единичным входом четвертого триггера и первыми входами второго и третьего элементов ИШГ, четвертый выход третьего дешифратора соединен с единичным входом пятого триггера, первым входом первого элемента ИЛИ и вторим входом третьего элемента ИЛИ, шейтой выход третьего дииифратора соединен с единичным входом шестого триггера и вторыми входами первого и второго элементов ИЛИ, каходы первого, второго и третьего эле ентов ИЛИ соединены соответственно с нулевыми входами четвертого, пятого и шестого триггеров, выходы KOTOJMX подключены к одним входам блока сравнения, другие входы которого соединены с выходами первого долифратора, выггод блока сравнения соединен с первш4 входом третьего элемента И, второй вход которого соединен с выходом первого триггера и входом формирователя импульса, выход третьего элемента И соединен с входом младшего разряда второго доиифратора, а выход формирователя импульса соединен через блок задержки с управг ляющим входом второго коммутатора. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 860099, кл. G Об К 1/02, 1979 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования кодов | 1983 |

|

SU1131033A1 |

| Устройство для вывода информации | 1984 |

|

SU1238090A1 |

| Устройство для приема и обработки информации в многорегистровых кодах | 1982 |

|

SU1049951A1 |

| Устройство для преобразования последовательныхМНОгОРЕгиСТРОВыХ КОдОВ B пАРАллЕльНыЕ СКОНТРОлЕМ | 1979 |

|

SU840877A1 |

| Устройство для ввода информации | 1983 |

|

SU1157545A1 |

| Устройство для управления ленточным перфоратором | 1979 |

|

SU860099A1 |

| Устройство для обмена данными | 1985 |

|

SU1297067A1 |

| Устройство для считывания информации | 1981 |

|

SU951338A1 |

| Устройство для формирования тестов | 1987 |

|

SU1444782A1 |

| Устройство для контроля памяти | 1981 |

|

SU985831A1 |

Авторы

Даты

1982-10-30—Публикация

1981-04-22—Подача