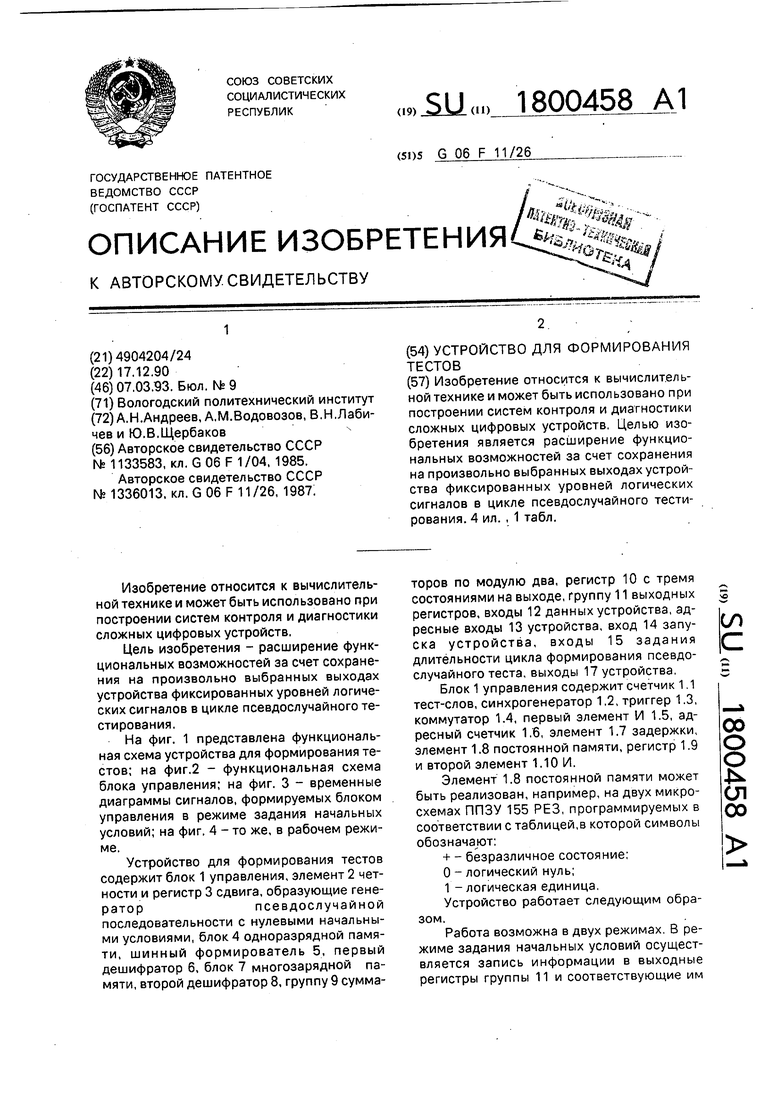

Изобретение относится к вычислительной технике и может быть использовано при построении систем контроля и диагностики сложных цифровых устройств,

Цель изобретения - расширение функциональных возможностей за счет сохранения на произвольно выбранных выходах устройства фиксированных уровней логических сигналов в цикле псевдослучайного тестирования.

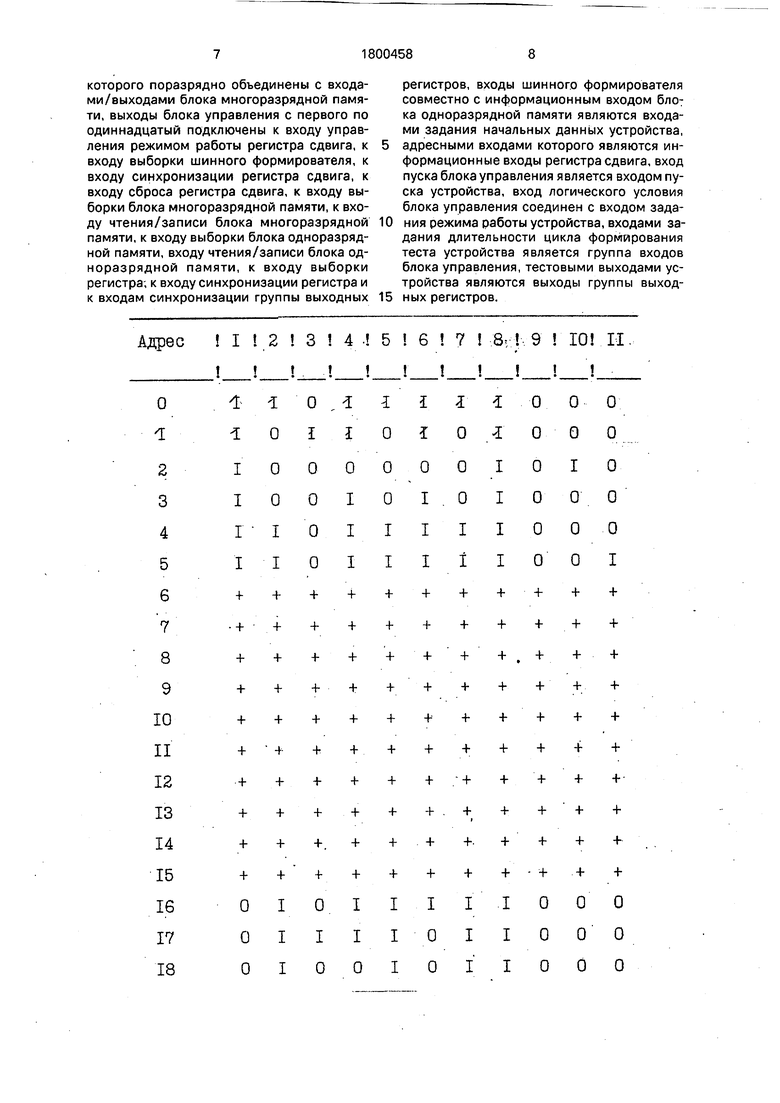

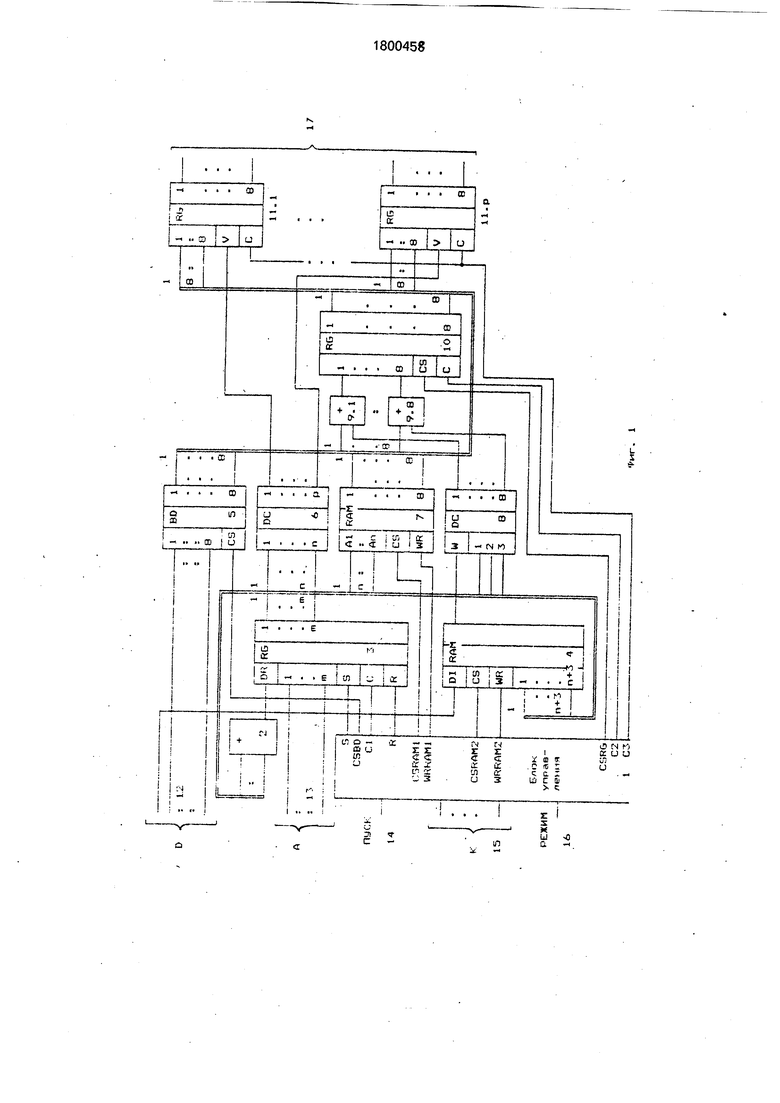

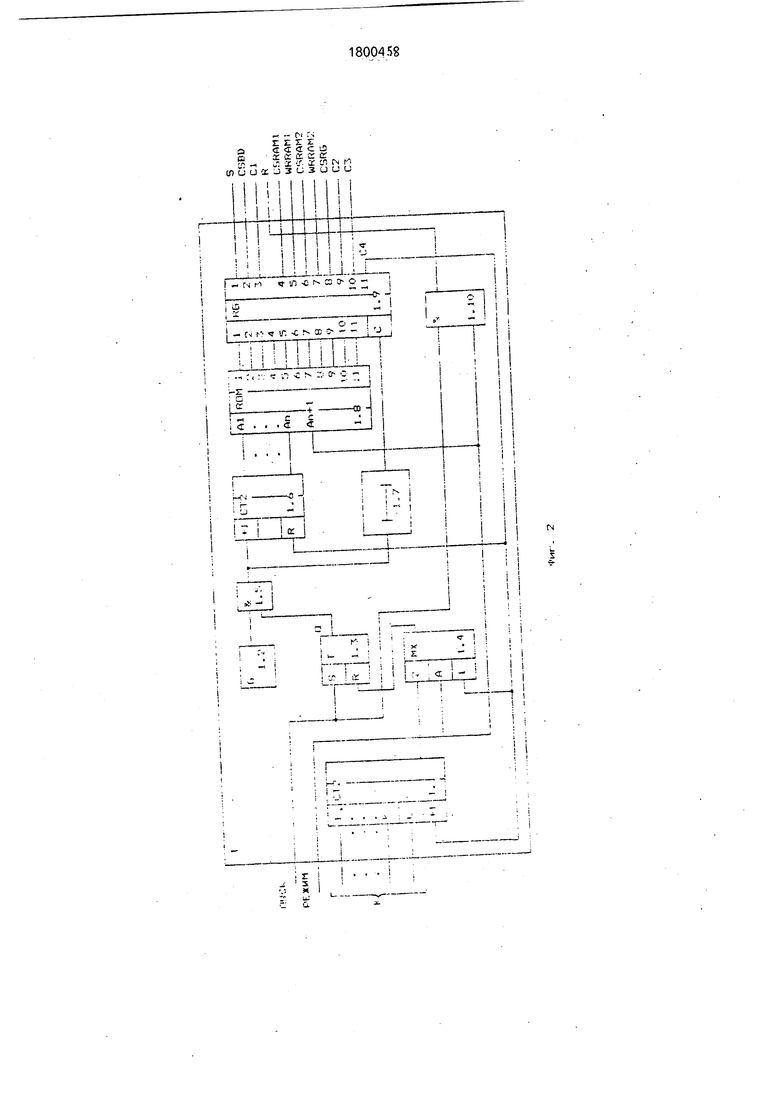

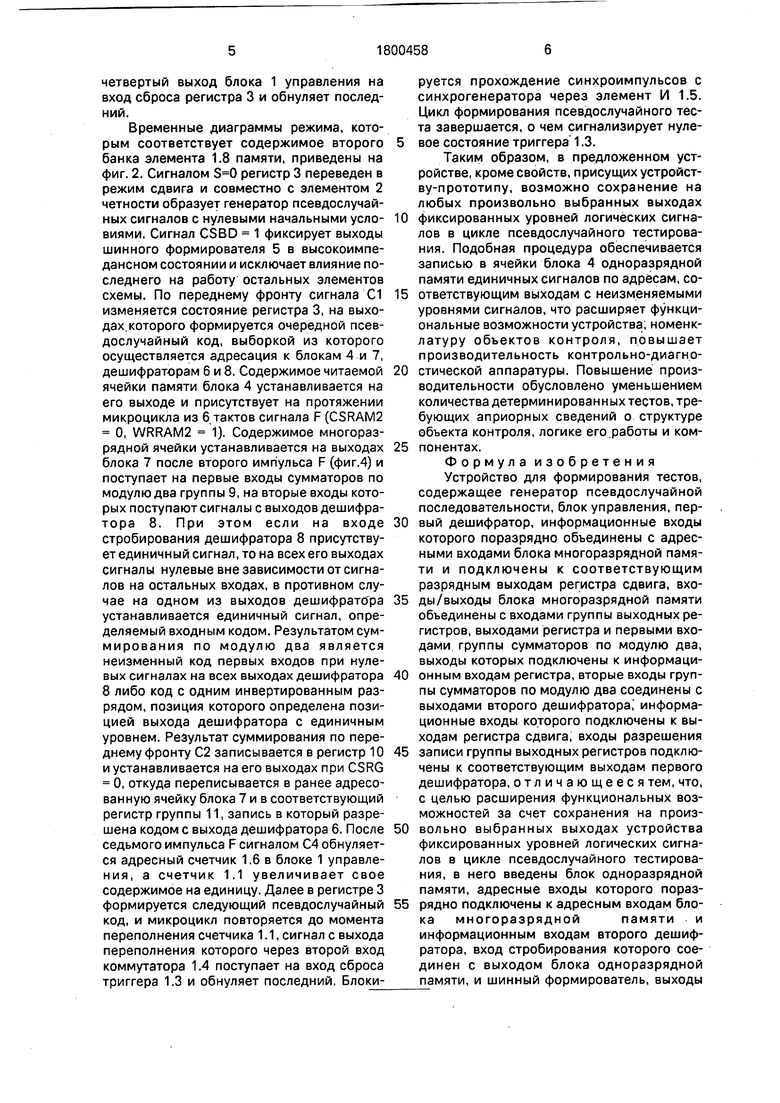

На фиг. 1 представлена функциональная схема устройства для формирования тестов; на фиг.2 - функциональная схема блока управления; на фиг. 3 - временные диаграммы сигналов, формируемых блоком управления в режиме задания начальных условий; на фиг. 4 - то же, в рабочем режиме.

Устройство для формирования тестов содержит блок 1 управления, элемент 2 четности и регистр 3 сдвига, образующие генераторпсевдослучайнойпоследовательности с нулевыми начальными условиями, блок 4 одноразрядной памяти, шинный формирователь 5, первый дешифратор 6, блок 7 многозарядной памяти, второй дешифратор 8, группу 9 сумматоров по модулю два, регистр 10 с тремя состояниями на выходе, группу 11 выходных регистров, входы 12 данных устройства, адресные входы 13 устройства, вход 14 запуска устройства, входы 15 задания длительности цикла формирования псевдослучайного теста, выходы 17 устройства.

Блок 1 управления содержит счетчик 1.1 тест-слов, синхрогенератор 1.2, триггер 1.3, коммутатор 1.4, первый элемент И 1.5, адресный счетчик 1,6, элемент 1.7 задержки, элемент 1.8 постоянной памяти, регистр 1.9 и второй элемент 1.10 И.

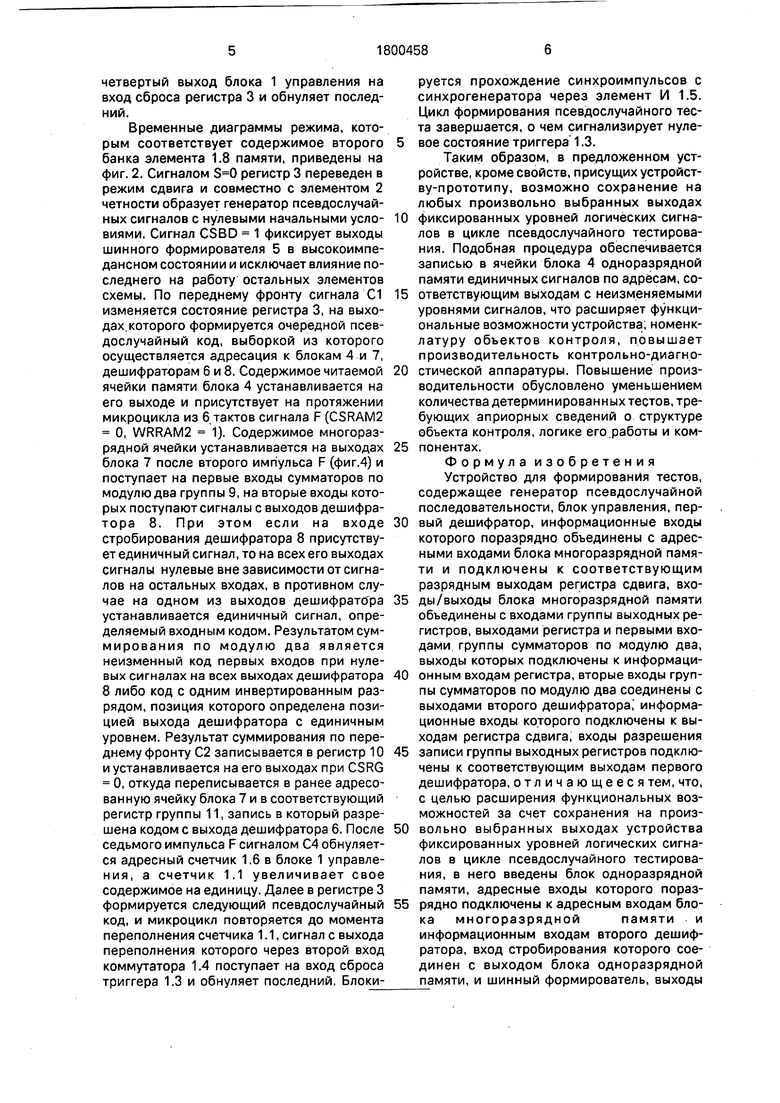

Элемент 1.8 постоянной памяти может быть реализован, например, на двух микросхемах ППЗУ 155 РЕЗ, программируемых в соответствии с таблицей,в которой символы обозначают:

+ - безразличное состояние:

О - логический нуль;

1 -логическая единица,

Устройство работает следующим образом.

Работа возможна в двух режимах. В режиме задания начальных условий осуществляется запись информации в выходные регистры группы 11 и соответствующие им

ел

С

00

о

S

ел

00

ячейки памяти блока 7. В одноразрядные ячейки памяти блока 4 заносится бинарная информация, соответствующая по распределению адресов разрядным выходам устройства. При этом уровень логической единицы, записанной в ячейку памяти блока 4, соответствует неизменяемому уровню сигнала на соответствующем выходе устройства в цикле синтеза псевдослучайного теста. Уровень логического нуля, записан- ный в ячейку памяти блока 4, соответствует выходу устройства с изменяемым уровнем сигнала в цикле псевдослучайного тестирования. Для реализации режима на входе 16 РЕЖИМ устанавливается нулевой уровенем сигнала. На входах 13 устанавливается адрес, определяющий выходной регистр группы 11, соответствующую ему ячейку памяти в блоке 7 и ячейку памяти в блоке 4, соответствующую одному из разрядов адресован- ного регистра. На входах 12 устанавливаются данные, заносимые в адресованный выходной регистр, ячейку блока 7 и ячейку блока 4. При этом информация, заносимая в блок 4, устанавливается на первом из входов 12. Перечисленные выше установки данных и адреса сопровождаются коротким единичным импульсом на входе 14 ПУСК устройства. Названным импульсом устанавливается в единичное состояние триггер 1.3 в блоке 1 управления, чем разрешается прохождение импульсов с синхрогенератора 1.2 через элемент J/I 1.5 на суммирующий вход адресного счетчика 1.6. Последний изменяет свое состояние в сто- рону увеличения. Наличие регистра 1.9 в блоке 1 управления необходимо для устранения состояний на выходах элемента 1.8 постоянной памяти при модификации адресов. Элемент задержки 1.7 компенсирует собственные временные задержки элементов 1.6 и 1.8, обеспечивая синхронизацию регистра 1.9 в момент установившихся уровней сигналов на выходах элемента 1.8 постоянной памяти.

Временные диаграммы блока 1 управления, которым соответствует содержимое первого банка памяти элемента 1.8 в режиме задания начальных условий приведены на фиг.З. Сигналом регистр 3 переведен в режим записи параллельной информации. После первого импульса F устанавливается в единичное состояние сигнал С1, по переднему фронту которого ранее установленный адрес записывается в регистр 3. Одновременно нулевыми сигналами CSBD, WRRAM1, WRRAM2 выбирается шинный формирователь 5 и подготавливаются к записи блоки 4 и 7 памяти. Данные через шинный формирователь 5 передаются на входы

регистров группы 11 и входы/выходы блркй 7. После второго импульса F при нулевом уровне сигналов CSRAM1 и CSRAM2 данные записываются в блоки памяти 4 и 7. Одновременно по переднему фронту сигнала СЗ в один из выходных регистров группы 11 в соответствии с единичным сигналом на одном из выходов дешифратора 6 осуществляется запись данных, являющихся начальными условиями для псевдослучайного теста. После пятого импульса F сигнал С4 с последующего выхода регистра 1.9 обнуляет адресный счетчик 1.6 и через первый вход коммутатора 1.4 поступает на выход последнего и сбрасывает триггер 1.3 в нулевое состояние, чем обеспечивается блокировка прохождения импульсов синхрогенератора 1.2 на счетчик 1.6 через элемент И 1.5. Выходы регистра 10 в режиме создания начальных условий находятся в высокоимпедансном состоянии и не оказывают влияния на другие элементы схемы. Далее устанавливается новый адрес и новые данные, сопровождаемые импульсом ПУСК. Микроцикл записи повторяется.

Результатом режима задания начальных условий является запись во все выходные регистры группы 11 данных, предваряющих псевдослучайный тест и продублированных в соответствующих ячейках блока 7 многоразрядной памяти. В ячейках блока 4 одноразрядной памяти занесена информация, соответствующая произвольно выбранным выходам устройства, сигналы на которых изменяются либо не изменяются в цикле псевдослучайного тестирования.

Дополнительно в названном режиме на выходе устройства может быть передан с входов 12 данных любой детерминированный заранее рассчитанный тест. Вход 1 ПУСК в этом случае выполняет функцию входа синхронизации устройства.

Режим формирования псевдослучайного теста предваряет установка на входе 16 единичного уровня сигнала и запись в счетчик 1.1 в блоке 1 управления кода, определяющего количество тест-слов псевдослучайного теста. Количество тест слов определяется разностью максимального кода счетчика 1.1 и начального кода.

Коротким единичным импульсом на входе 14 ПУСК устройства устанавливается в единичное состояние триггер 1.3 в блоке 1, чем разрешается прохождение импульсов с выхода синхрогенератора 1.2 через первый элемент И 1.5 на вход адресного счетчика 1.6. Одновременно через второй элемент JMO И названный импульс поступает через

четвертый выход блока 1 управления на вход сброса регистра 3 и обнуляет последний.

Временные диаграммы режима, которым соответствует содержимое второго банка элемента 1.8 памяти, приведены на фиг. 2. Сигналом регистр 3 переведен в режим сдвига и совместно с элементом 2 четности образует генератор псевдослучайных сигналов с нулевыми начальными условиями. Сигнал CSBD 1 фиксирует выходы шинного формирователя 5 в высокоимпе- дансном состоянии и исключает влияние последнего на работу остальных элементов схемы. По переднему фронту сигнала С1 изменяется состояние регистра 3, на выходах, которого формируется очередной псевдослучайный код, выборкой из которого осуществляется адресация к блокам 4 и 7, дешифраторам 6 и 8. Содержимое читаемой ячейки памяти блока 4 устанавливается на его выходе и присутствует на протяжении микроцикла из 6 тактов сигнала F (CSRAM2 О, WRRAM2 1). Содержимое многоразрядной ячейки устанавливается на выходах блока 7 после второго импульса F (фиг.4) и поступает на первые входы сумматоров по модулю два группы 9, на вторые входы которых поступают сигналы с выходов дешифратора 8. При этом если на входе стробирования дешифратора 8 присутствует единичный сигнал, то на всех его выходах сигналы нулевые вне зависимости от сигналов на остальных входах, в противном случае на одном из выходов дешифратора устанавливается единичный сигнал, определяемый входным кодом. Результатом сум- мирования по модулю два является неизменный код первых входов при нулевых сигналах на всех выходах дешифратора 8 либо код с одним инвертированным разрядом, позиция которого определена позицией выхода дешифратора с единичным уровнем. Результат суммирования по переднему фронту С2 записывается в регистр 10 и устанавливается на его выходах при CSRG 0, откуда переписывается в ранее адресованную ячейку блока 7 и в соответствующий регистр группы 11, запись в который разрешена кодом с выхода дешифратора 6. После седьмого импульса F сигналом С4 обнуляется адресный счетчик 1.6 в блоке 1 управления, а счетчик 1.1 увеличивает свое содержимое на единицу. Далее в регистре 3 формируется следующий псевдослучайный код, и микроцикл повторяется до момента переполнения счетчика 1.1, сигнал с выхода переполнения которого через второй вход коммутатора 1.4 поступает на вход сброса триггера 1.3 и обнуляет последний. Блокируется прохождение синхроимпульсов с синхрогенератора через элемент И 1.5. Цикл формирования псевдослучайного теста завершается, о чем сигнализирует нулевое состояние триггера 1.3.

Таким образом, в предложенном устройстве, кроме свойств, присущих устройству-прототипу, возможно сохранение на любых произвольно выбранных выходах

0 фиксированных уровней логических сигналов в цикле псевдослучайного тестирования. Подобная процедура обеспечивается записью в ячейки блока 4 одноразрядной памяти единичных сигналов по адресам, со5 ответствующим выходам с неизменяемыми уровнями сигналов, что расширяет функциональные возможности устройства; номенклатуру объектов контроля, повышает производительность контрольно-диагно0 стической аппаратуры. Повышение производительности обусловлено уменьшением количества детерминированных тестов, требующих априорных сведений о структуре объекта контроля, логике его работы и ком5 понентах.

Формула изобретения Устройство для формирования тестов, содержащее генератор псевдослучайной последовательности, блок управления, пер0 вый дешифратор, информационные входы которого поразрядно объединены с адресными входами блока многоразрядной памяти и подключены к соответствующим разрядным выходам регистра сдвига, вхо5 ды/выходы блока многоразрядной памяти объединены с входами группы выходных регистров, выходами регистра и первыми входами группы сумматоров по модулю два, выходы которых подключены к информаци0 онным входам регистра, вторые входы группы сумматоров по модулю два соединены с выходами второго дешифратора информационные входы которого подключены к выходам регистра сдвига, входы разрешения

5 записи группы выходных регистров подключены к соответствующим выходам первого дешифратора, отличающееся тем, что, с целью расширения функциональных возможностей за счет сохранения на произ0 вольно выбранных выходах устройства фиксированных уровней логических сигналов в цикле псевдослучайного тестирования, в него введены блок одноразрядной памяти, адресные входы которого пораз5 рядно подключены к адресным входам блока многоразряднойпамяти и информационным входам второго дешифратора, вход стробирования которого соединен с выходом блока одноразрядной памяти, и шинный формирователь, выходы

71800458 8

которого поразрядно объединены с входа-регистров, входы шинного формирователя ми/выходами блока многоразрядной памя-совместно с информационным входом бло: ти, выходы блока управления с первого пока одноразрядной памяти являются входа- одиннадцатый подключены к входу управ-ми задания начальных данных устройства, ления режимом работы регистра сдвига, к5 адресными входами которого являются ин- входу выборки шинного формирователя, кформационные входы регистра сдвига, вход входу синхронизации регистра сдвига, кпуска блока управления является входом пу- входу сброса регистра сдвига, к входу вы-ска устройства, вход логического условия борки блока многоразрядной памяти, к вхо-блока управления соединен с входом зада- ду чтения/записи блока многоразрядной10 ния режима работы устройства, входами за- памяти, к входу выборки блока одноразряд-дания длительности цикла формирования ной памяти, входу чтения/записи блока од-теста устройства является группа входов поразрядной памяти, к входу выборкиблока управления, тестовыми выходами ус- регистра; к входу синхронизации регистра итройства являются выходы группы выход- к входам синхронизации группы выходных15 ных регистров.

, .Jr

г

1.2

(Г

8 :

1 8 V

Rb

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| Герератор тестов | 1986 |

|

SU1361561A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1383368A1 |

| ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНЫХ СИГНАЛОВ | 2009 |

|

RU2416157C1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1619347A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1376084A1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1587515A1 |

| ТЕСТЕР УРОВНЯ ИННОВАЦИОННОГО ИНТЕЛЛЕКТА ЛИЧНОСТИ | 2013 |

|

RU2522992C1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| Устройство для ввода информации | 1989 |

|

SU1682996A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении систем контроля и диагностики сложных цифровых устройств, Целью изобретения является расширение функциональных возможностей за счет сохранения на произвольно выбранных выходах устройства фиксированных уровней логических сигналов в цикле псевдослучайного тестирования. 4 ил., 1 табл.

17

ПУСК 14

CSBD С1

CSRAM I WRHAM1

CSRAM; WRRAM;

Блок управления

CSR6

С2 1 СЗ

J

17

ИГЛ

RB

cs

I

СП 00

f-nr. 1

ПППЈПЈГХПП(Л V bj W X j Т. -v i- И

зз з 53 я х . a

Си D Ъ It 3233 ;.; ig .- 8SJ7008L

1800458

12345

...

Фиг. 3

| Система адаптивного управления | 1983 |

|

SU1133583A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для формирования тестов | 1986 |

|

SU1336013A1 |

Авторы

Даты

1993-03-07—Публикация

1990-12-17—Подача