1

Изобретение относится к области вычислительной техники и может найти применение при построении аналого-цифровых преобразователей (АЦП), а также при согласовании аналоговых и цифровых устройств в различных системах обработки сигналов.

Известно аналоговое запоминающее устройство, использующее последовательные аналоговые ключи на биполярных и полевых транзисторах 1.

Недостаток таких устройств - сравнительно высокий уровень помех, проходящих через паразитные емкости, что ограничивает как их точность, так и быстродействие.

Известно также аналоговое запоминающее устройство, использующее операционный усилитель и обратную связь при заряде накопительного конденсатора 2.

Недостатки этого устройства - сложность и относительно невысокое быстродействие.

Наиболее близким по технической сущности к предлагаемому является устройство, которое состоит из входного буферного каскада, аналогового ключа, разделительного элемента, накопительного конденсатора и выходного буферного каскада. Когда ключ

разомкнут, происходит стробирование исходного сигнала и заряда накопительного конденсатора. Когда ключ замыкается, выходной сигнал входного каскада замыкается на шину нулевого потенциала и на накопительном конденсаторе сохраняется заряд, оставшийся в момент замыкания ключа. Разделительный элемент, представляющий собой однонаправленный вентиль (либо диод, либо р-п переход транзистора), необходим для того, чтобы отделить накопительный кон10 денсатор от ключа в режиме запоминания ЗЗ Недостатками рассмотренного устройст. ва являются относительно невысокая точность образования выборочных значений, которая ограничивается в первую очередь разделительным элементом, а также однополярность устройства, что тоже определяется наличием разделительного элемента, представляющего собой однонаправленный вентиль.

Цель изобретения - увеличение точно20 сти образования выборочных значений и придание устройству свойства работать от биполярных входных сигналов.

Поставленная цель достигается тем, что в аналоговом запоминающем устройстве.

содержащем входной усилитель, вход которого соединен со входом устройства, накопительный элемент, например конденсатор, ключ, соединенный с шиной управления и шиной нулевого потенциала, выходной каскад, например операционный усилитель, выход которого соединен с выходом устройства, ключ соединен с одной обкладкой конденсатора и первым входом операционного усилителя, второй вход которого подключен к выходу входного усилителя и другой обкладке конденсатора.

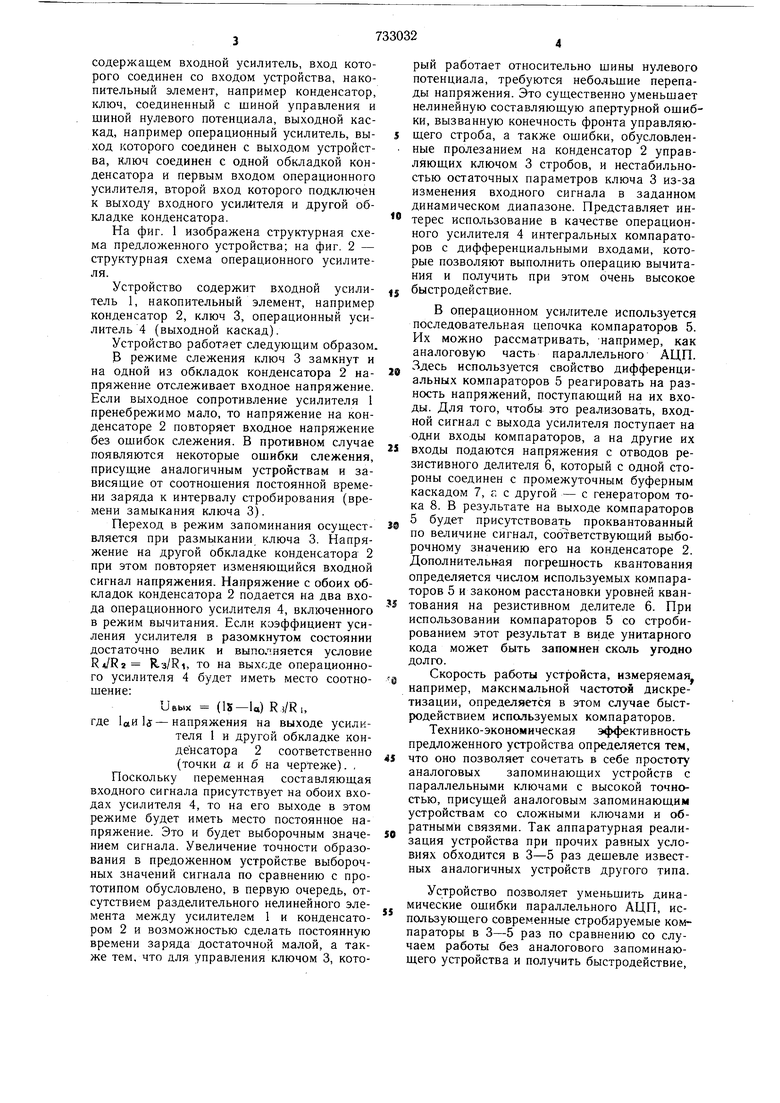

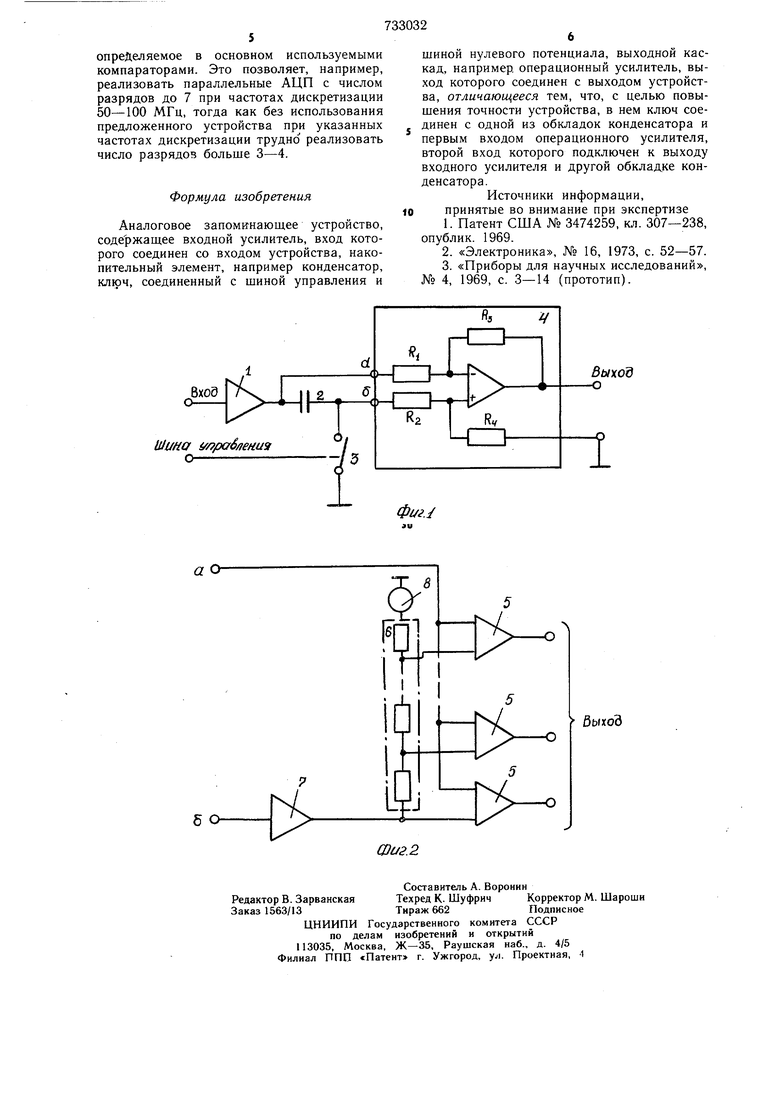

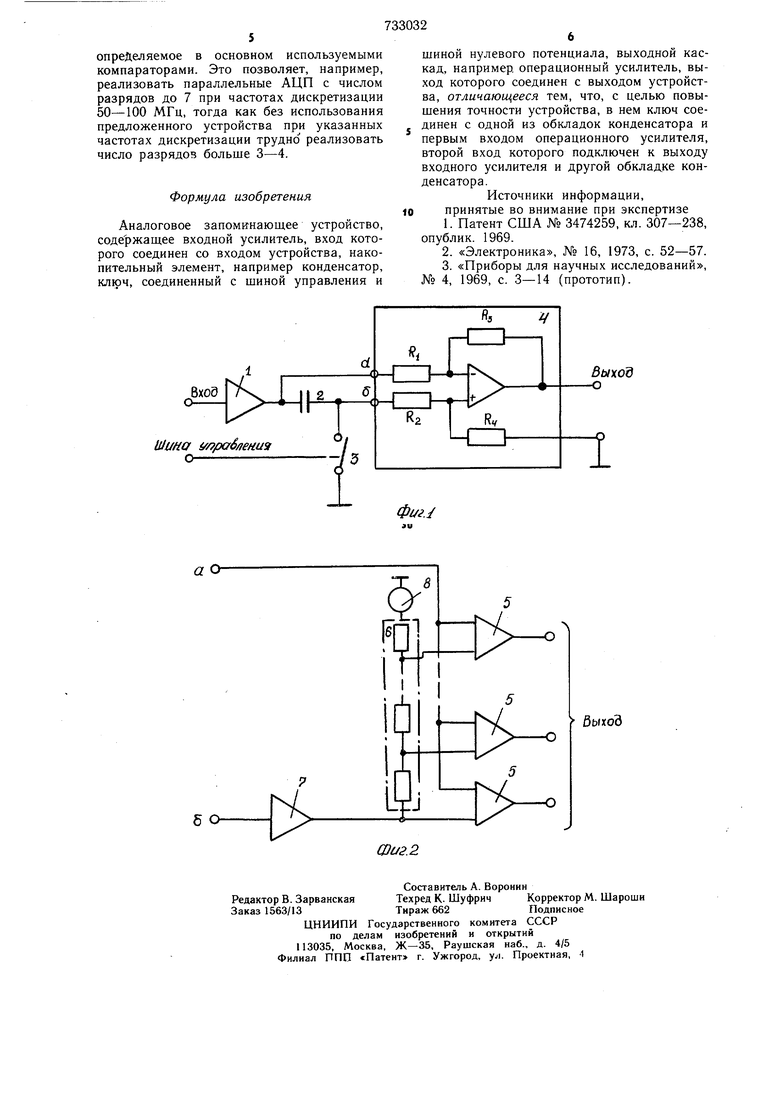

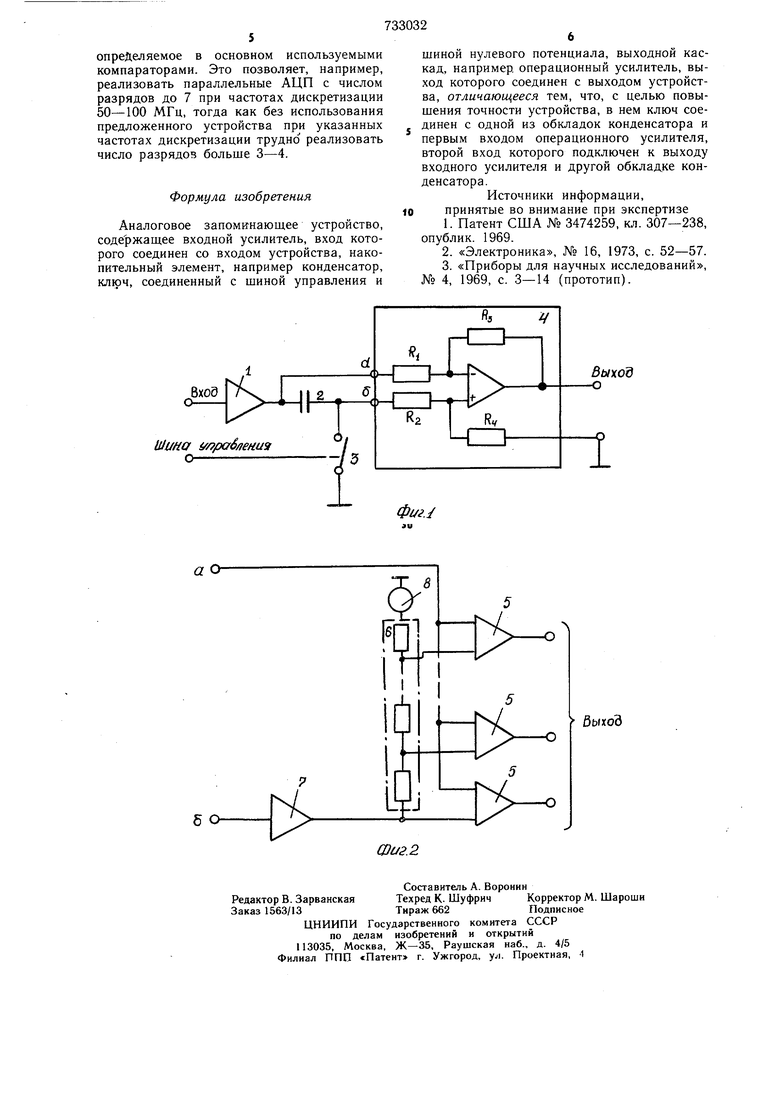

На фиг. 1 изображена структурная схема предложенного устройства; на фиг. 2 - структурная схема операционного усилителя.

Устройство содержит входной усилитель 1, накопительный элемент, например конденсатор 2, ключ 3, операционный усилитель 4 (выходной каскад).

Устройство работает следующим образом.

В режиме слежения ключ 3 замкнут и на одной из обкладок конденсатора 2 напряжение отслеживает входное напряжение. Если выходное сопротивление усилителя 1 пренебрежимо мало, то напряжение на конденсаторе 2 повторяет входное напряжение без ошибок слежения. В противном случае появляются некоторые ошибки слежения, присущие аналогичным устройствам и зависящие от соотношения постоянной времени заряда к интервалу стробирования (времени замыкания ключа 3).

Переход в режим запоминания осуществляется при размыкании ключа 3. Напряжение на другой обкладке конденсатора 2 при этом повторяет изменяющийся входной сигнал напряжения. Напряжение с обоих обкладок конденсатора 2 подается на два входа операционного усилителя 4, включенного в режим вычитания. Если коэффициент усиления усилителя в разомкнутом состоянии достаточно велик и выполняется условие Нд/К2 Ra/Ri, то на выходе операционного усилителя 4 будет иметь место соотношение:

ивых (IS-la) RVRi,

где - напряжения на выходе усилителя 1 и другой обкладке конденсатора 2 соответственно (точки а и б на чертеже). ,

Поскольку переменная составляющая входного сигнала присутствует на обоих входах усилителя 4, то на его выходе в этом режиме будет иметь место постоянное напряжение. Это и будет выборочным значением сигнала. Увеличение точности образования в предоженном устройстве выборочных значений сигнала по сравнению с прототипом обусловлено, в первую очередь, отсутствием разделительного нелинейного элемента между усилителем 1 и конденсатором 2 и возможностью сделать постоянную времени заряда достаточной малой, а также тем, что для управления ключом 3, который работает относительно щины нулевого потенциала, требуются небольшие перепады напряжения. Это существенно уменьшает нелинейную составляющую апертурной ошибки, вызванную конечность фронта управляющего строба, а также ошибки, обусловленные пролезанием на конденсатор 2 управляющих ключом 3 стробов, и нестабильностью остаточных параметров ключа 3 из-за изменения входного сигнала в заданном динамическом диапазоне. Представляет интерес использование в качестве операционного усилителя 4 интегральных компараторов с дифференциальными входами, которые позволяют выполнить операцию вычитания и получить при этом очень высокое быстродействие.

В операционном усилителе используется последовательная цепочка компараторов 5. Их можно рассматривать, -например, как аналоговую часть параллельного АЦП. Здесь используется свойство дифференциальных компараторов 5 реагировать на разность напряжений, поступающий на их входы. Для того, чтобы это реализовать, входной сигнал с выхода усилителя поступает на одни входы компараторов, а на другие их входы подаются напряжения с отводов резистиБного делителя 6, который с одной стороны соединен с промежуточным буферным каскадом 7, г, с другой - с генератором тока 8. В результате на выходе компараторов 5 будет присутствовать проквантованный по величине сигнал, соответствующий выборочному значению его на конденсаторе 2. Дополнителькая погрешность квантования определяется числом используемых компараторов 5 и законом расстановки уровней квантования на резистивном делителе 6. При использовании компараторов 5 со стробированием этот результат в виде унитарного кода может быть запомнен сколь угодно долго.

Скорость работы устройств, измеряемая например, максимальной частотон дискретизации, определяется в этом случае быстродействием используемых компараторов.

Технико-экономическая эффективность предложенного устройства определяется тем, что оно позволяет сочетать в себе простоту аналоговых запоминающих устройств с параллельными ключами с высокой точностью, присущей аналоговым запоминающим устройствам со сложными ключами и обратными связями. Так аппаратурная реализация устройства при прочих равных условиях обходится в 3-5 раз дешевле известных аналогичных устройств другого типа.

Устройство позволяет уменьшить динамические ошибки параллельного АЦП, использующего современные стробируемые компараторы в 3-5 раз по сравнению со случаем работы без аналогового запоминающего устройства и получить быстродействие,

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1982 |

|

SU1084897A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU832601A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU771729A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU767844A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU968855A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU963106A1 |

| Аналоговое запоминающее устройство | 1983 |

|

SU1104586A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU920843A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU1001179A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU924755A1 |

Авторы

Даты

1980-05-05—Публикация

1977-11-28—Подача