1

Изобретение относится к вычислительной технике, в частности к устройствам сопряжения ЭВМ, и может быть исполь-эовано в многомашинных иерархических автоматизированных системах управления производством -(АСУП) для обеспечения автоматического обмена информацией между ЭВМ различных уровней иерархии.

Известно устройство для обмена информацией, содержащее абоненты,буферный запоминающий блок, коммутатор, счетчики ввода и вывода, а также ассоциативных запоминающий блок, узел анализа состояний буферных областей, счетчики объема буферных областей, узел модификации управляющих елоев tilНедостатком указанного устройства является невозможность применения его в. системах реального масштаба времени вследствие ограниченного быстродействия, обусловленного тем, что все абоненты подразделяются на источники информации и приемники информации, причем за каждой парой абоиентов, участвующих в обмене, закрепляется определенная буферная область, в которую осуществляет запись информации абонент-источник, а считывание - абонент-приемник. Повторная запись информации в эту зону возможна при полном считывании информации абонентом-приемниксяч из данной буферной области.

Наиболее близким к предлагаемому изобретению по технической сущности и дОстигаемс 1у эффекту является устройство для обмена информацией, со10держащее множество каналов ввода-вывода, разбитых на несколько групп, адресуемую память, разделяемую указанными каналами, групповые адаптеры, устройство управления, буферное запо15мингиощее устройство дляозапоминания запросов, шину для передачи запроса от соответствующего адаптера к устройству управления, шину разрешения,по которой устройство управления разре20шает соответствующему адаптеру передавать запросы в шину запросов, а также множество линий признаков,управляемых соответствующими адаптером 2J.

25

Недостатком указанного устройства является невозможность применения его в системах реального масштаба времени, накладывающих жесткие тре30:бования на воемя обмена информацией.

Кроме того, выдача адаптерами запросов на обмен информацией и обмен информацией осуществляется только при наличии вакантного пространства в буферной памяти для записи запросов, что ведет к задержке в обмене информацией между адаптерами и памятью. Задержка при обмене информацией в системах реального времени недопустима, так как ведет к потере информации.

Цель изобретения - повышение быстродействия устройства.

Поставленная цель достигается тем что в устройство для обмена информацией, содержащее блок буферной памяти, вход-выход которого соединен с первыми информационными входами-выходами адаптеров группы адаптеров, блок управления, первые вход и выход вторые.вход и выход которого соединены соответственно с контрольным выходом и управляющим входом блока буферной памяти, с идентификационными выходами и входами адаптеров группы адаптеров, вторые информационные входы-выходы адаптеров являются входами-выходами устройства, введены дополнительно регистр прерываний, блок анализа запросов, распределител импу(1ьсов , группа формирователей импульсов конца обмена, две группы элементов И, группа элементов ИЛИ и элемент ИЛИ-НЕ, причем третий выход блока управления соединен с первыми входами элементов И первой группы, вторые входы которых соединены с выходами соответствующих формирователей импульсов конца обмена, выходы регистра прерываний соединены с первой группой входов блока управления, вторая группа входов которого соединена с выходами элементов И второй группы, входы каждого элемента ИЛИ группы соединены с выходами соответствующего элемента И группы соответствующего формирователя импульса конца обмена, запросные выходы адаптеров группы соединены с соответствующими запросными входами блока анализа запросов, управляющий вход которого соединен с выходом распределителя импульсов, каждый выход группы выходов блока анализа запросов соединен с входом соответствующего формирователя импульса конца обмена группы и с первым входом соответствующего элемента И второй группы, вторые входы элементов И второй группы через элемент ИЛИ-НЕ соединены с выходами формирователей импульса конца обмена, выходы элементов И первой группы соединены с разрядными входами регистра прерываний.

Кроме того, блок анализа запросов содержит группу элементов НЕ, три группы элементов И, группу элементов ИЛИ, элемент ИЛИ и узел приоритета, причем запросные входы блока соединены с первыми входами элементов И первой группы и через соответствующие элементы НЕ группы - с входами узла приоритета и с первыми входами элементов И третьей группы, вторые входы элементов И первой и третьей групп соединены с управляющими входами блока, запросные входы блока ,кроме первого запросного входа, соединены с соответствующими входами узла приоритета, выходы которого соединены с первыми входами элементов И второй группы, выходы элементов И третьей группы через элемент ИЛИ соединены с вторыми,входами элементов И второй группы, выходы которых ивыходы элементов И первой группы через соответствующие элементы ИЛИ группы соединены с выходами блока, а первый запросный вход блока соединен с первым входом соответствующего элемента И второй группы, причем блок управления содержит распределитель импульсов,первую и вторую группы элементов И, группу элементов ИЛИ,группу элементов НЕ, группу триггеров и элементов НЕ, причем вход распределителя импульсов является вторым входом блока и через элемент НЕ соединен с первым выходом блока, первый и второй выходы распределителя импульсов являются :первь1М и третьим Выходами блока, третий выход соединен с первыми входами элементов И второй группы, вторые входы которых являются первой группой входов блока а выходы соединены с первыми входами элементов ИЛИ группы, вторые входы которых соединены с выходами триггеров группы, а выходы соединены с первыми входами элементов И первой группы, вторь.е входы которых являются первым входом блока, а выходы являются вторым выходом блока, первые входы триггеров группы являются второй группой входов блока и через элемент НЕ соединены с вторыми входами триггеров группы.

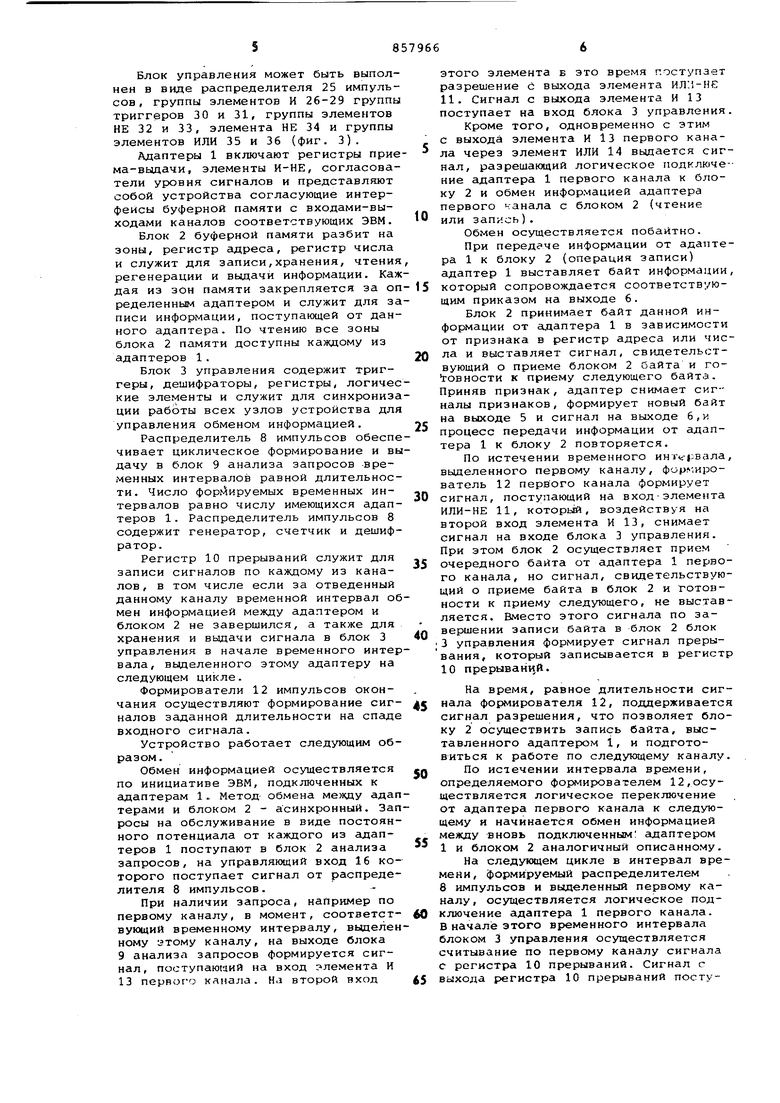

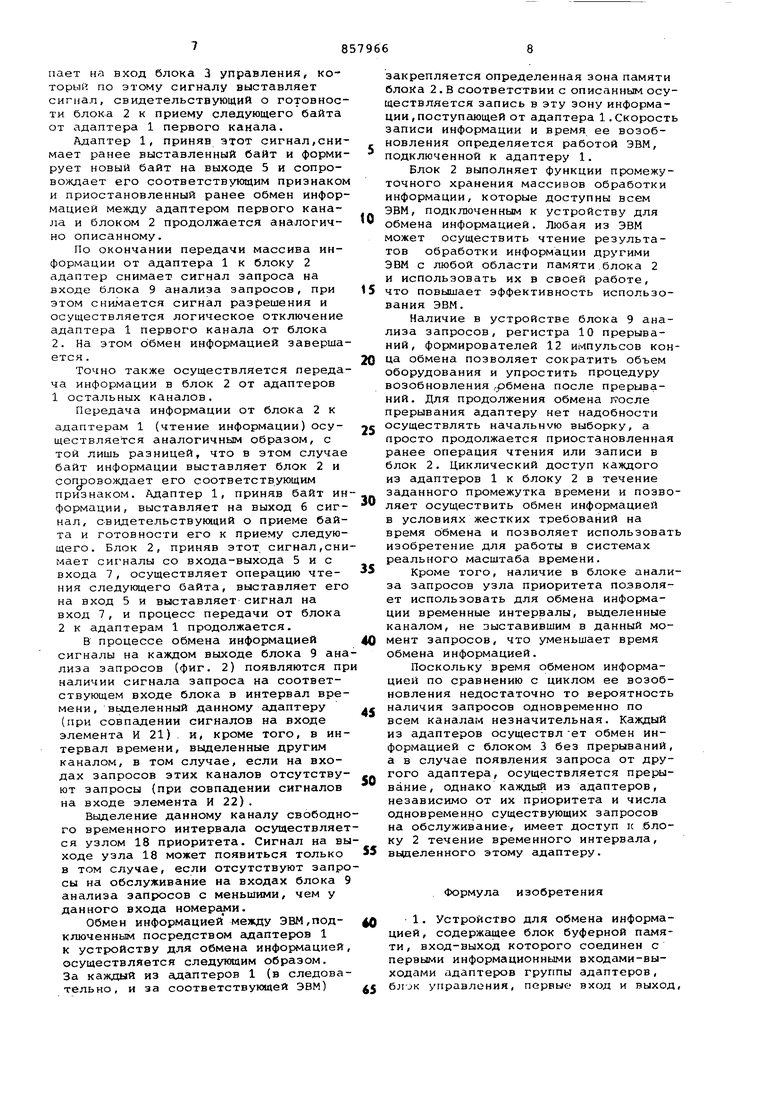

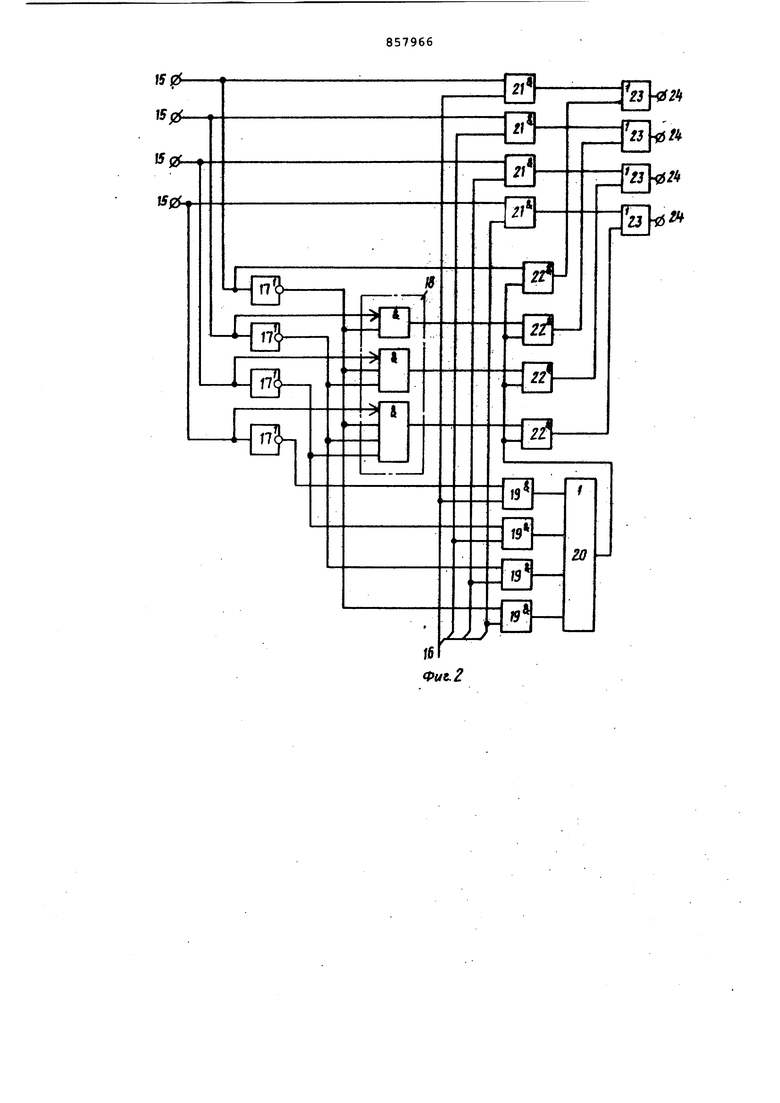

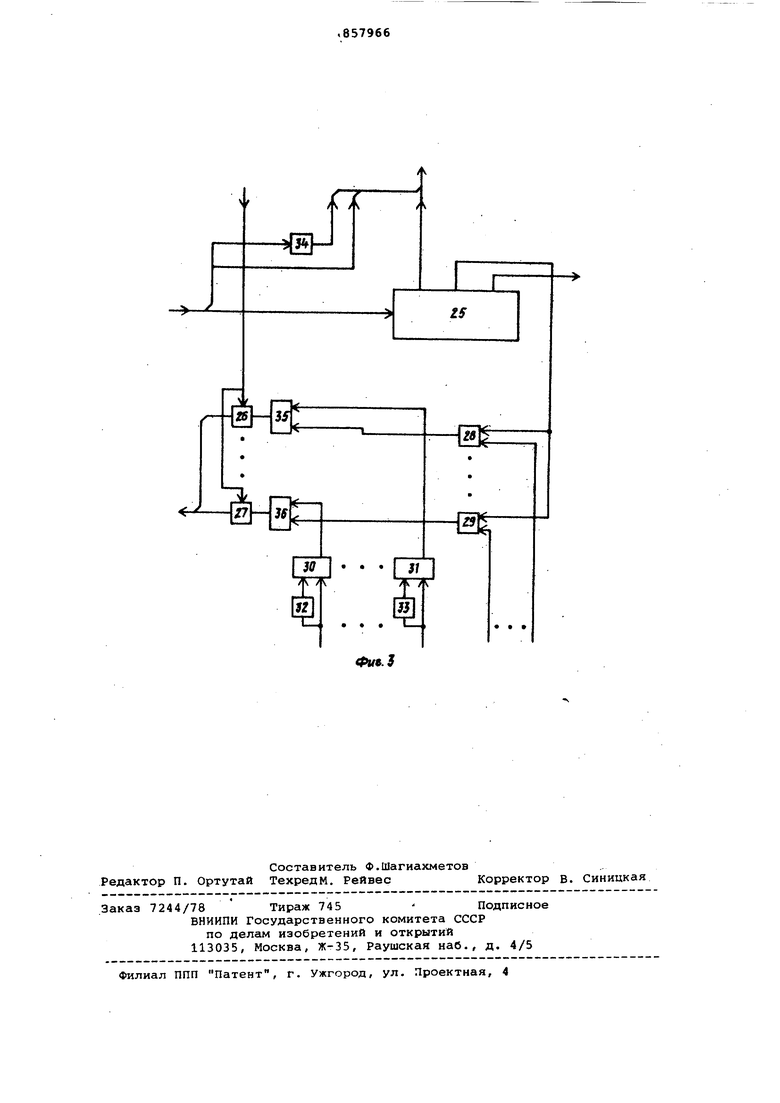

На фиг. 1 представлена структурная схема устройства; на фиг. 2 структурная схема блока анализа запросов; на фиг. 3 - вариант выполнения блока управления.

Устройство для обмена информацией содержит адаптеры 1, блок 2 буферной памяти, блок 3 управления, группу элементов И 4, выходы 5 и 6 адаптера вход 7 адаптера, распределитель 8 импульсов, блок 9 анализа запросов, регистр 10 прерываний, элемент ИЛИ-Н 11, формирователи 12 импульса конца обмена, группу элементов И 13, группу элементов ИЛИ 14, запросные входы 15; управляющий вход 16 (фиг. 1).

Блок анализа запросов содержит элементы НЕ 17, узел 18 приоритета, элементы И 19, элемент ИЛИ 20, элементы И 21 и 22, элементы ИЛИ 23, выходы 24 (фиг. 2 К Блок управления может быть выполнен в виде распределителя 25 импульсов , группы элементов И 26-29 группы триггеров 30 и 31, группы элементов НЕ 32 и 33, элемента НЕ 34 и группы элементов ИЛИ 35 и 36 (фиг. 3). Адаптеры 1 включают регистры прие ма-выдачи, элементы И-НЕ, согласователи уровня сигналов и представляиот собой устройства согласующие интерфейсы буферной памяти с входами-выходами каналов соответствующих ЭВМ. Блок 2 буферной памяти разбит на зоны, регистр адреса, регистр числа и служит для записи,хранения, чтения регенерации и выдачи информации. Каж дая из зон памяти закрепляется за оп ределенным адаптером и служит для за писи информации, поступающей от данного адаптера. По чтению все зоны блока 2 памяти доступны каждому из адаптеров 1. Блок 3 управления содержит триггеры, дешифраторы, регистры, логичес кие элементы и служит для синхрониза ции работы всех узлов устройства для управления обменом информацией. Распределитель 8 импульсов обеспе чивает циклическое формирование и вы дачу в блок 9 анализа запросов временных интервалов равной длительности. Число формируемых временных интервалов равно числу имеющихся адаптеров 1. Распределитель импульсов 8 содержит генератор, счетчик и дешифратор. Регистр 10 прерываний служит для записи сигналов по каждому из каналов , в том числе если за отведенный данному каналу временной интервал об мен информацией между адаптером и блоком 2 не завершился, а также для хранения и вьздачи сигнала в блок 3 управления в начале временного интер вала, вьщеленного этому адаптеру на следующем цикле. Формирователи 12 импульсов окончания осуществляют формирование сигналов заданной длительности на спаде входного сигнала. Устройство работает следующим образом. Обмен информацией осуществляется по инициативе ЭВМ, подключенных к адаптерам 1.. Метод обмена между адап терами и блоком 2 - асинхронный. Зап росы на обслуживание в виде постоянного потенциала от каждого из адаптеров 1 поступают в блок 2 анализа запросов, на управляющий вход 16 которого поступает сигнал от распределителя 8 импульсов. При наличии запроса, например по первому каналу, в момент, соответствующий временному интервалу, выделен ному этому каналу, на выходе блока 9 анализа запросов формируется CHI- нал, поступающий на вход элемента И 13 первого канала. Нл второй вход этого элемента Б это время поступает разрешение С выхода элемента ИЛ:1-НЕ 11. Сигнал с выхода элемента И 13 поступает на вход блока 3 управления. Кроме того, одновременно с этим с выхода элемента И 13 первого канала через элемент ИЛИ 14 выдается сигнал, разрешающий логическое подключение адаптера 1 первого канала к блоку 2 и обмен информацией адаптера первого канала с блоком 2 (чтение или запись). Обмен осуществляется побайтно. При передаче информации от адаптера 1 к блоку 2 (операция записи) адаптер 1 выставляет байт информации, который сопровождается соответствующим приказом на выходе 6. Блок 2 принимает байт данной информации от адаптера 1 в зависимостут от признака в регистр адреса или числа и выставляет сигнал, свидетельствующий о приеме блоком 2 байта и гоговности к приему следующего байта. Приняв признак, адаптер снимает сигналы признаков, формирует новый байт на выходе 5 и сигнал на выходе 6,и процесс передачи информации от адаптера 1 к блоку 2 повторяется. По истечении временного (;вала, выделенного первому каналу, формирователь 12 первого канала формирует сигнал, поступающий на входэлемента ИЛИ-НЕ 11, который, воздействуя на второй вход элемента И 13, снимает сигнал на входе блока 3 управления. При этом блок 2 осуществляет прием очередного байта от адаптера 1 первого канала, но сигнал, свидетельствующий о приеме байта в блок 2 и готовности к приему следующего, не выставляется. Вместо этого сигнала по завершении записи байта в блок 2 блок 3 управления формирует сигнал прерывания, который записывается в регистр 10 прерываний. На время, равное длительности сигнала формирователя 12, поддерживается сигнал разрешения, что позволяет блоку 2 осуществить запись байта, выставленного адаптером 1, и подготовиться к работе по следующему каналу. По истечении интервала времени, определяемого формирователем 12,осуществляется логическое переключение от адаптера первого канала к следующему и начинается обмен информацией между вновь подключенным адаптером 1 и блоком 2 аналогичный описанному. На следующем цикле в интервал вреени, формируемый распределителем импульсов и выделенный первому каалу, осуществляется логическое подлючение адаптера 1 первого канала. начале этого временного интервала локом 3 управления осуществляется читывание по первому каналу сигнала регистра 10 прерываний. Сигнал с ыхода регистра 10 прерываний поступает на вход блока 3 управления, который по этому сигналу выставляет сигнал, свидетельствуювдий о готовности блока 2 к приему следующего байта от адаптера 1 первого канала.

Адаптер 1, приняв этот сигнал,снимает ранее выставленный байт и формирует новый байт на выходе 5 и сопровождает его соответствующим признаком и приостановленный ранее обмен информацией между адаптером первого канала и блоком 2 продолжается аналогично описанному.

По окончании передачи массива информации от адаптера 1 к блоку 2 адаптер снимает сигнал запроса на входе блока 9 анализа запросов, при этом снимается сигнал разрешения и осуществляется логическое отключение адаптера 1 первого канала от блока 2. На этом обмен информацией завершается .

Точно также осуществляется передача информации в блок 2 от адаптеров 1 остальных каналов.

Передача информации от блока 2 к адаптерам 1 (чтение информации) осуществляется аналогичным образом, с той лишь разницей, что в этом случае байт информации выставляет блок 2 и сопровождает его соответствующим признаком. Адаптер 1, приняв байт информации, выставляет на выход 6 сигнал, свидетельствующий о приеме байта и готовности его к приему следующего. Блок 2, приняв этот сигнал,снимает сигналы со входа-выхода 5 и с входа 7, осуществляет операцию чтения следующего байта, выставляет его на вход 5 и выставляет сигнал на вход 7, и процесс передачи от блока 2 к адаптерам 1 продолжается.

В процессе обмена информацией сигналы на каждом выходе блока 9 анализа запросов (фиг. 2) появляются пр наличии сигнала запроса на соответствующем входе блока в интервал времени, выделенный данному адаптеру (при совпадении сигналов на входе элемента И 21) и, кроме того, в интервал времени, выделенные другим каналом, в том случае, если на входах запросов этих каналов отсутствуют запросы (при совпадении сигналов на входе элемента И 22).

Выделение данному каналу свободного временного интервала осуществляется узлом 18 приоритета. Сигнал на выходе узла 18 может появиться только в том случае, если отсутствуют запросы на обслуживание на входах блока 9 анализа запросов с меньшими, чем у данного входа номерами.

Обмен информацией между ЭВМ,подключенным посредством адаптеров 1 к устройству для обмена информацией, осуществляется следующим образом. За каждый из адаптеров 1 (в следовательно, и за соответствующей ЭВМ)

закрепляется определенная зона памяти блока 2. В соответствии с описанным осуществляется запись в эту зону информации, поступающей от адаптера 1 .Скорост записи информации и время ее возобновления определяется работой ЭВМ, подключенной к адаптеру 1.

Блок 2 выполняет функции промежуточного хранения массивов обработки информации, которые доступны всем ЭВМ, подключенным к устройству для обмена информацией. Любая из ЭВМ может осуществить чтение результатов обработки информации другими ЭВМ с любой области памяти блока 2 и использовать их в своей работе, что повышает эффективность использования ЭВМ.

Наличие в устройстве блока 9 анализа запросов, регистра 10 прерываний, формирователей 12 импульсов конца обмена позволяет сократить объем оборудования и упростить процедуру возобновления .рбмена после прерываний. Для продолжения обмена прерывания адаптеру нет надобности осуществлять начальную выборку, а просто продолжается приостановленная ранее операция чтения или записи в блок 2. Циклический доступ каждого из адаптеров 1 к блоку 2 в течение заданного промежутка времени и позволяет осуществить обмен информацией в условиях жестких требований на время обмена и позволяет использоват изобретение для работы в системах реального масштаба времени.

Кроме того, наличие в блоке анализа запросов узла приоритета позволяет использовать для обмена информации временные интервалы, выделенные каналом, не зыставившим в данный момент запросов, что уменьшает время обмена информацией.

Поскольку время обменом информацией по сравнению с циклом ее возобновления недостаточно то вероятность наличия запросов одновременно по всем каналам незначительная. Каждый из адаптеров осуществл -ет обмен информацией с блоком 3 без прерываний, а в случае появления запроса от другого адаптера, осуществляется прерывание, однако каждый из адаптеров, независимо от их приоритета и числа одновременно существующих запросов на обслуживание, имеет доступ к блоку 2 течение временного интервала, вьаделенного этому адаптеру.

Формула изобретения

1. Устройство для обмена информацией, содержащее блок буферной памяти, вход-выход которого соединен с первыми информационными входами-выходами адаптеров группы адаптеров, блок управления, первые вход и выход. вторые вход и выход которого соедине ны соответственно с контрольным выходом и управляющим входом блока буферной памяти, с идентифицированными выходами и входами адаптеров группы адаптеров, вторые информационные вхо ды-выходы адаптеров являются входами выходами устройства, о т л и ч а ющ е е с я тем, что, с целью повышения быстродействия устройства, оно содержит регистр прерываний, блок анализа запросов, распределитель импульсов, группу формирователей импульсов конца обмена, две группы ментов И, группу элементов ИЛИ и эле мент ИЛИ-НЕ, причем третий выход бло ка управления соединен с первыми вхо дами элементов И первой группы, вторые входы которых соединены с выхода ми соответствующих формирователей им пульсов конца обмена, выходы регистра прерываний соединены с первой груп пой входов блока управления, вторая группа входов которого соединена с выходами элементов И второй группы, входы каждого элемента ИЛИ группы соединены с выходами соответствующего элемента И группы соответствующего формирователя импульса конца обме на, запросные выходы адаптеров группы соединены с соответствующими запросными входами блока анализа запросов , управляющий вход которого соединен с выходом распределителя им пульсов, каждый выход группы выходов блока анализа запросов соединен с входом соответствующего формирователя импульса конца обмена группы и с первым входом соответствующего элемента И второй группы, вторые входы элементов И второй группы через элемент ИЛИ-НЕ соединены с выходами формирователей импульса конца обмена, выходы элементов И первой группы соединены с разрядными входами регистра прерываний. 2. Устройство по п. 1, отличающееся тем, что блок анали за запросов содержит группу элементов НЕ, три группы элементов И,группу элементов ИЛИ, элемент ИЛИ и узел приоритета, причем запросные входы блока соединены с первыми входами элементов И первой грулпы и через соответствующие элементы НЕ группы с входами узла приоритета и с первыми входами элементов И третьей группы, вторые входы элементов И первой и третьей групп соединены с управляющими входами блока, запросные входы блока, кроме первого запросного входа, соединены с соответствующими входами узла приоритета, выходы которого соединены с первьми входами элементов И второй группы, выходы элементов И третьей группы через элемент ИЛИ соед .мены с вторхлми входами элементов И второй группы, выходы которых и вьрсоды элементов И первой группы черюз соответствующие элементы ИЛИ группы соединены с выходами блока а первый запросный вход блока соединен с первым входом соответствующего элемента И второй группы. 3. Устройство по п. 1, отличающееся тем, что блок управления содержит распределитель импульсов, первую и вторую группы элементов И, группу элементов ИЛИ,группу элементов НЕ, группу триггеров и элементов НЕ, причем вход распределителя импульсов является вторым входом блока и через элемент НЕ соединен с первым выходом блока, первый и второй выходы распределителя кмпульсов являются первым и третьим выходами блока, третий выход соединен с первыми входами элементов И второй группы, вторые входы которых являются первой группой входов блока, а выходы соединены с первыми входами элементов ИЛИ группы, вторые входы которых соединены с выходами триггеров группы, а выходы соединены с первыми входами элементов И первой группы, вторые входы которых являются первым входом блока, а выходы являются вторым выходом блока, первые входы триггеров группы являются второй группой входов блока и через элемент НЕ соединены с вторьми входами триггеров группы. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР 496551, кл. G 06 F 3/04, 1974. 2.Патент США № 4126897, НКИ 340-172.5, МКИ G 06 F 3/00, G 06 F 13/00, 1976 ().

Г 710

Г--

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

| Устройство для сопряжения оконечного устройства с мультиплексным каналом передачи информации | 1987 |

|

SU1538172A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1988 |

|

SU1596338A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для сопряжения двух цифровых вычислительных машин | 1979 |

|

SU868741A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Устройство для вывода информации | 1980 |

|

SU962910A1 |

| Устройство обмена информацией между ЭВМ и абонентами | 1990 |

|

SU1835545A1 |

/У,

-U/zh/5.

/5,

6

Т (3

ш

„L-iTil

1-1.:: rr

f- Г7-1 -J L-T; 1 i

-f

r- -

us

t3

f

/

П

К 1S0.

J50.

0Л

-gj

Фик.2

Авторы

Даты

1981-08-23—Публикация

1979-12-10—Подача