со

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Система обработки нечеткой информации | 1987 |

|

SU1444803A1 |

| Устройство для обработки нечеткой информации | 1985 |

|

SU1564603A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ НЕЧЕТКОЙ ИНФОРМАЦИИ | 1998 |

|

RU2158441C2 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Процессор с микропрограммным управлением | 1982 |

|

SU1124298A1 |

Изобретение относится к вычислительной технике и может быть использовано при создании устройств обработки нечеткой информации в системах искусственного интеллекта. Целью изобретения является повышение быстродействия при выполнении арифметико-логических операций над нечеткими данными за счет параллельной обработки элементов нечеткого множества. Устройство содержит N регистров 1 слова, N блоков 2 памяти, N блоков 3 адреса, регистр 4 команд, дешифратор 5, блок 6 управления, N блоков 7 поиска минимума, N блоков 8 поиска максимума, N блоков 9 сдвига, арифметико-логический блок 10, счетчик 11 команд, буферный регистр 12. Устройство имеет вход А 3 сброса, вход А 4 пуска, вход А 6 управления начальной загрузкой, выход А 7 управления начальной загрузкой, вход А 8 адреса пуска. 3 з.п. ф-лы, 7 ил.

о

VI

Ј ел

Изобретение относится к вычислительной технике и может быть использовано при создании устройств обработки нечеткой информации в системах искусственного интеллекта.

Целью изобретения является повышение быстродействия при выполнении арифметико-логических операций над нечеткими данными за счет параллельной обработки элементов нечеткого множества.

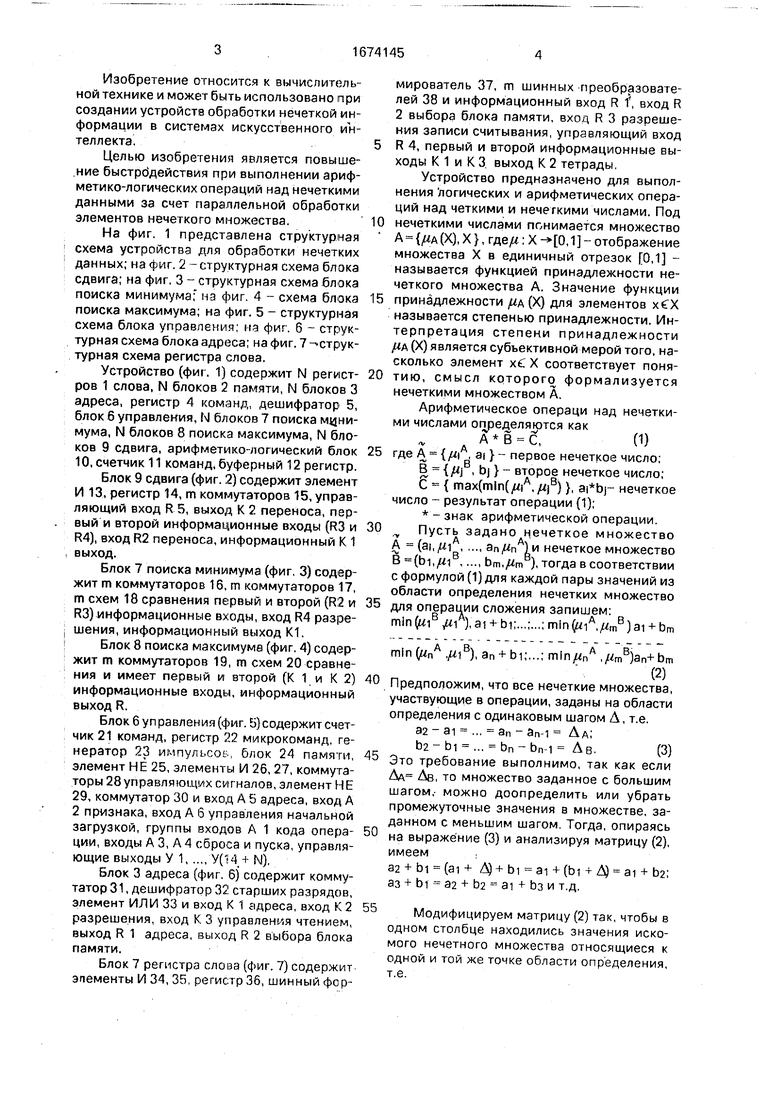

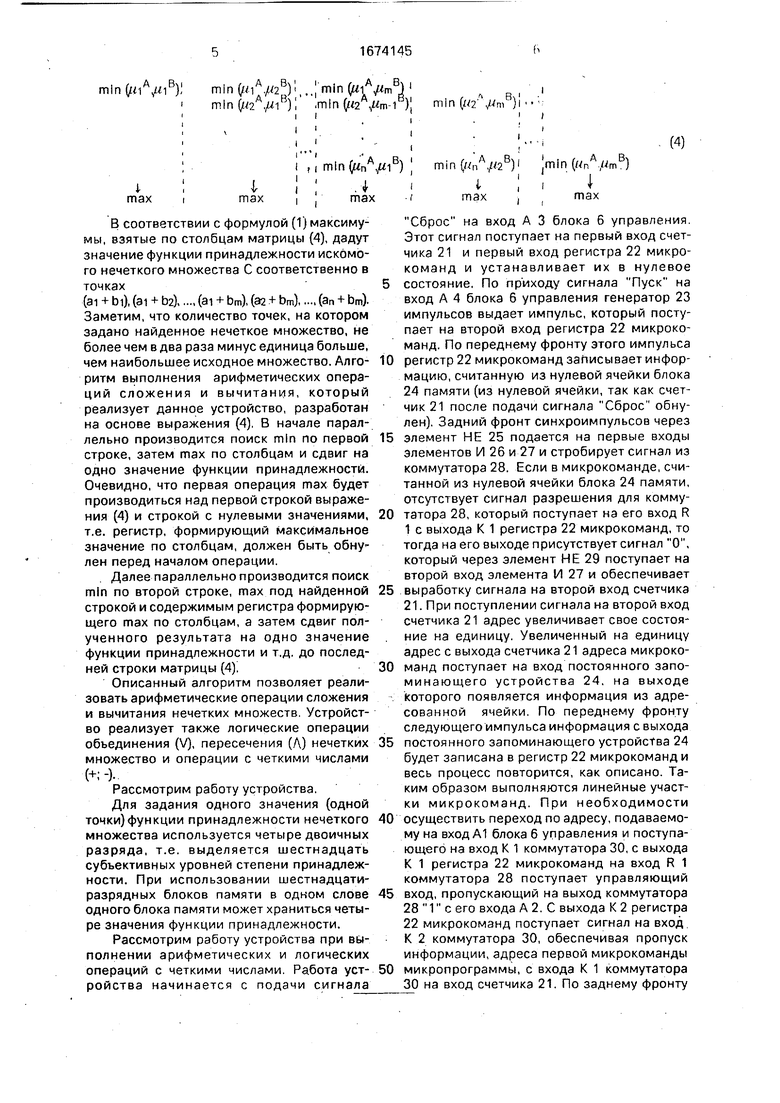

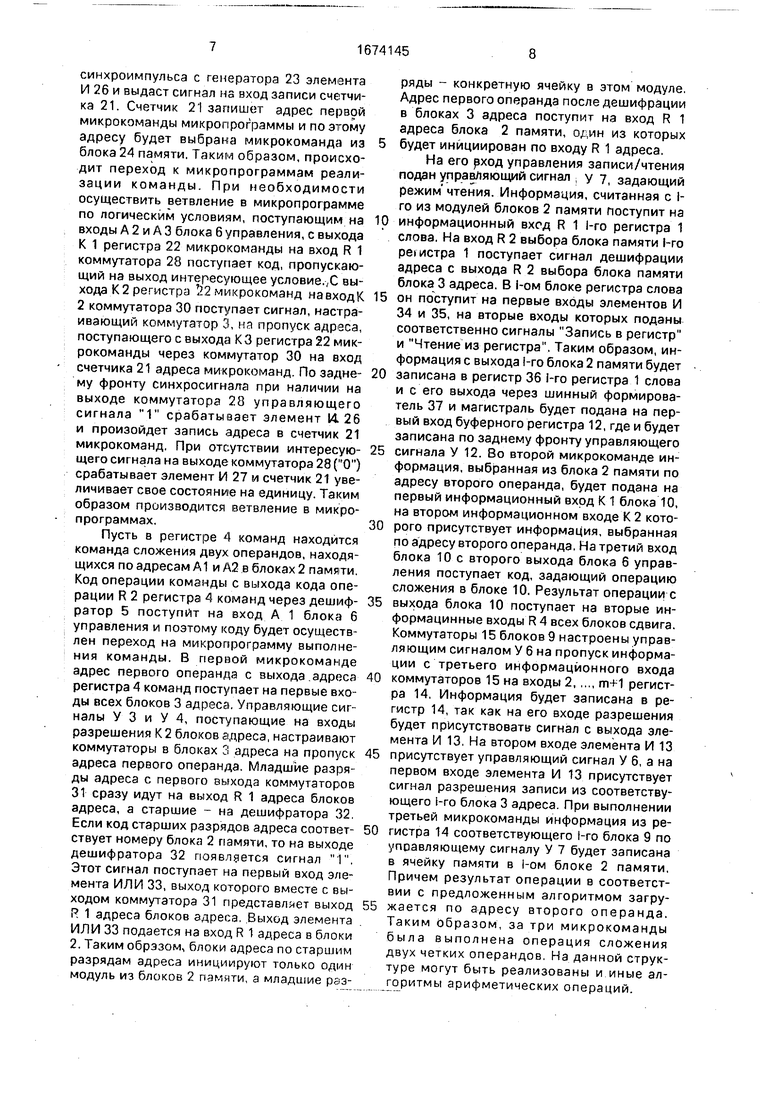

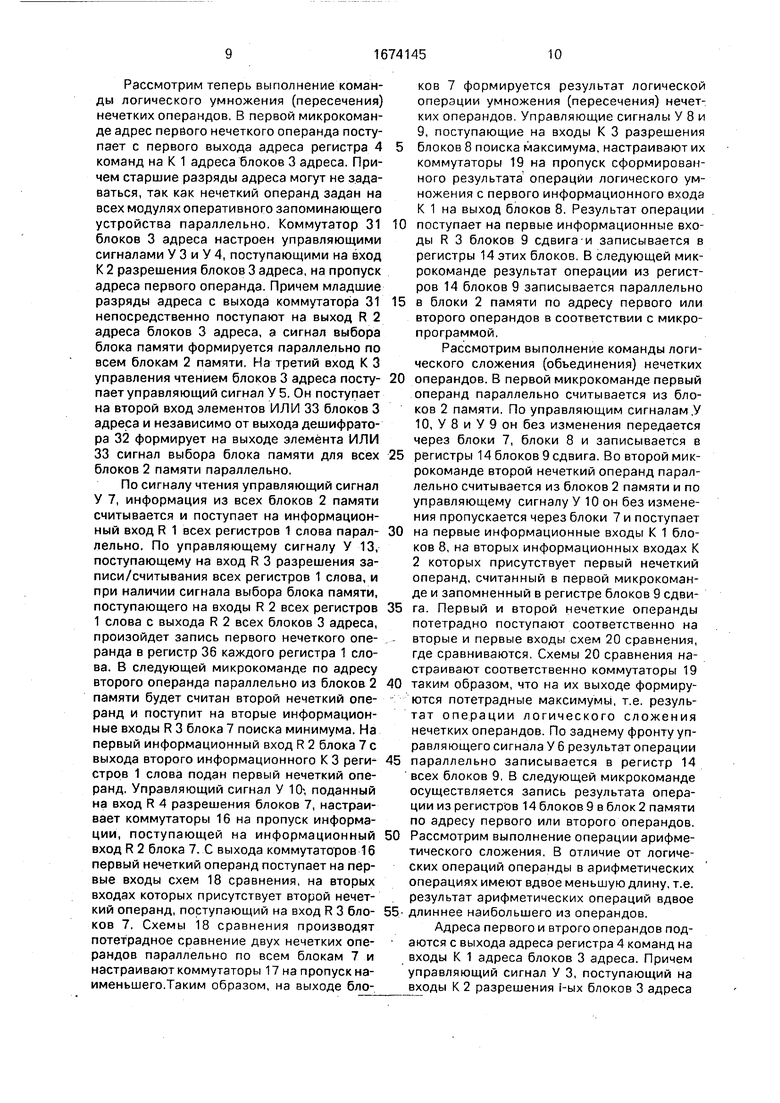

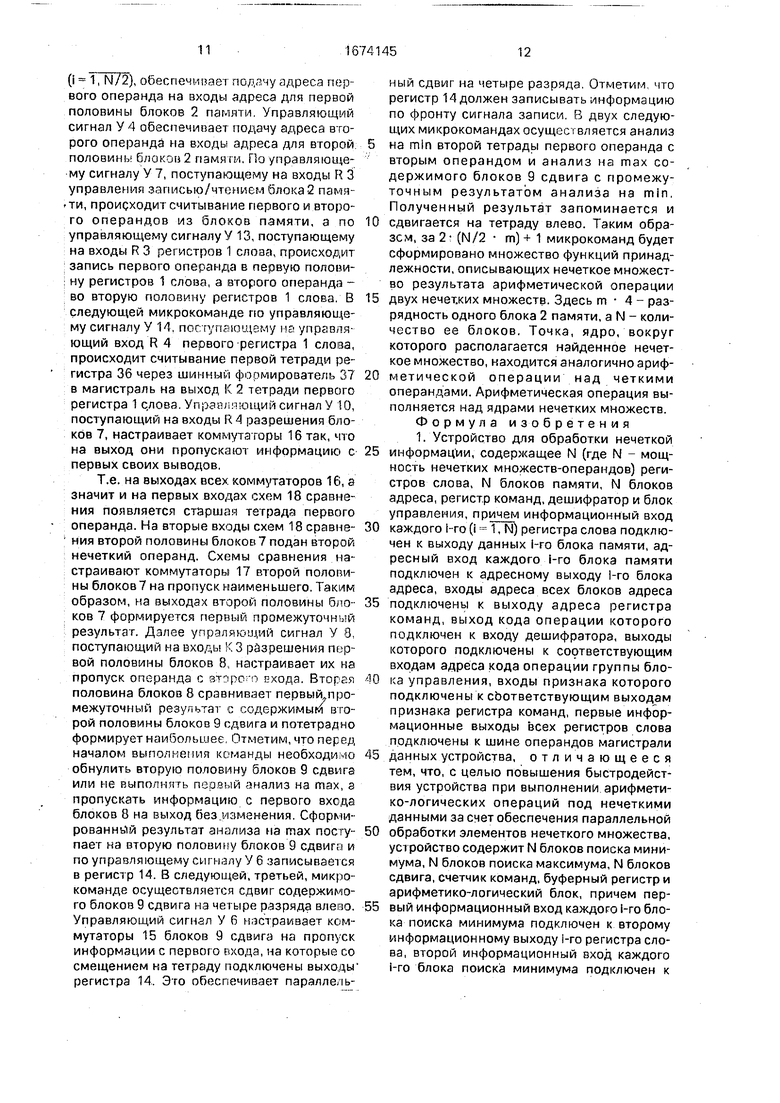

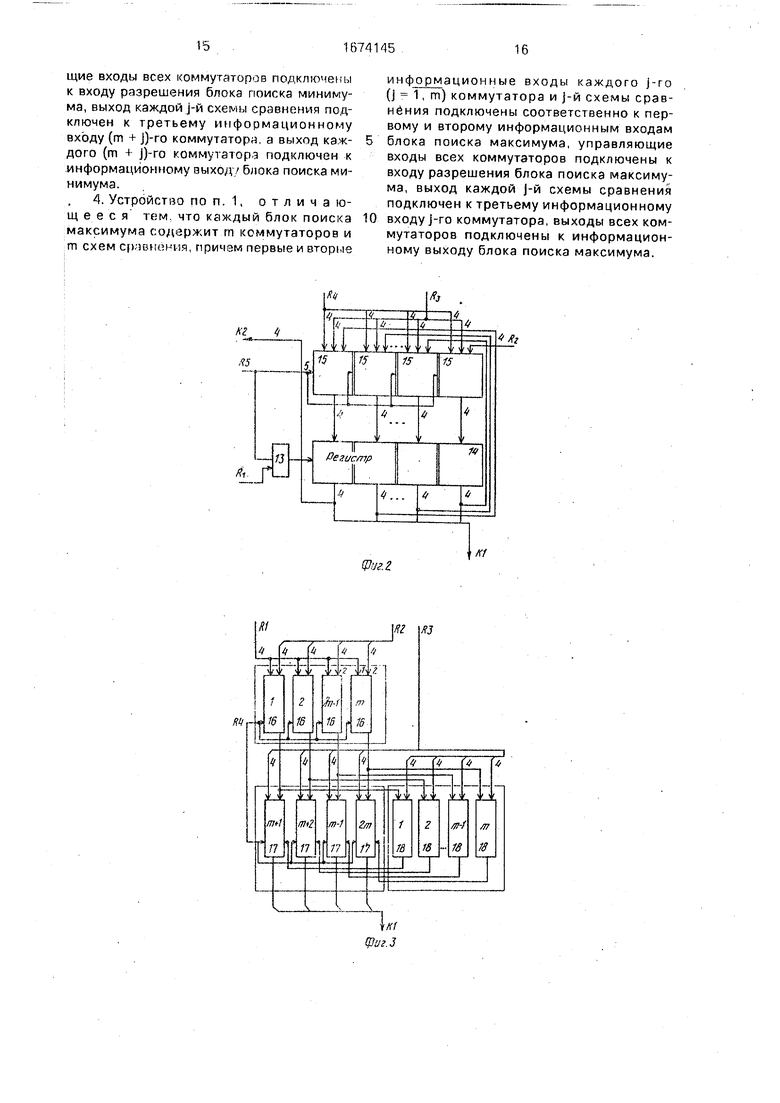

На фиг. 1 представлена структурная схема устройства для обработки нечетких данных; на фиг. 2 - структурная схема блока сдвига; на фиг. 3 - структурная схема блока поиска минимума на фиг. 4 - схема блока поиска максимума; на фиг. 5 - структурная схема блока управления; на фиг. 6 - структурная схема блока адреса; на фиг. 7 -структурная схема регистра слова.

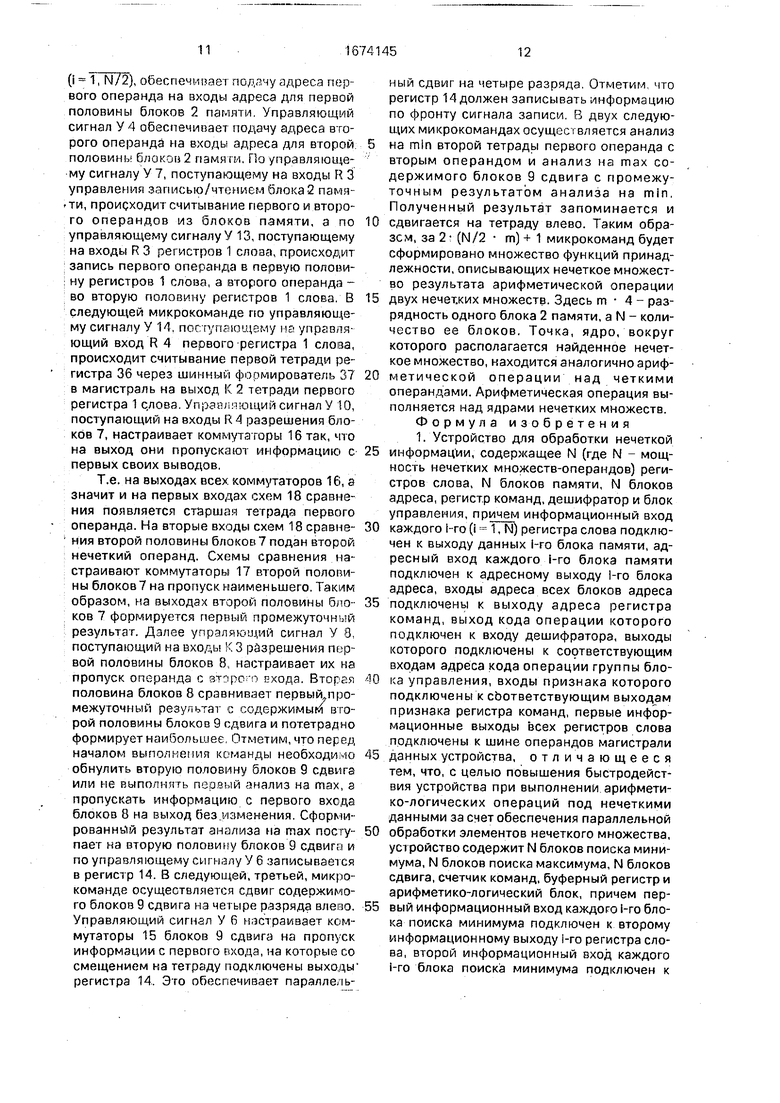

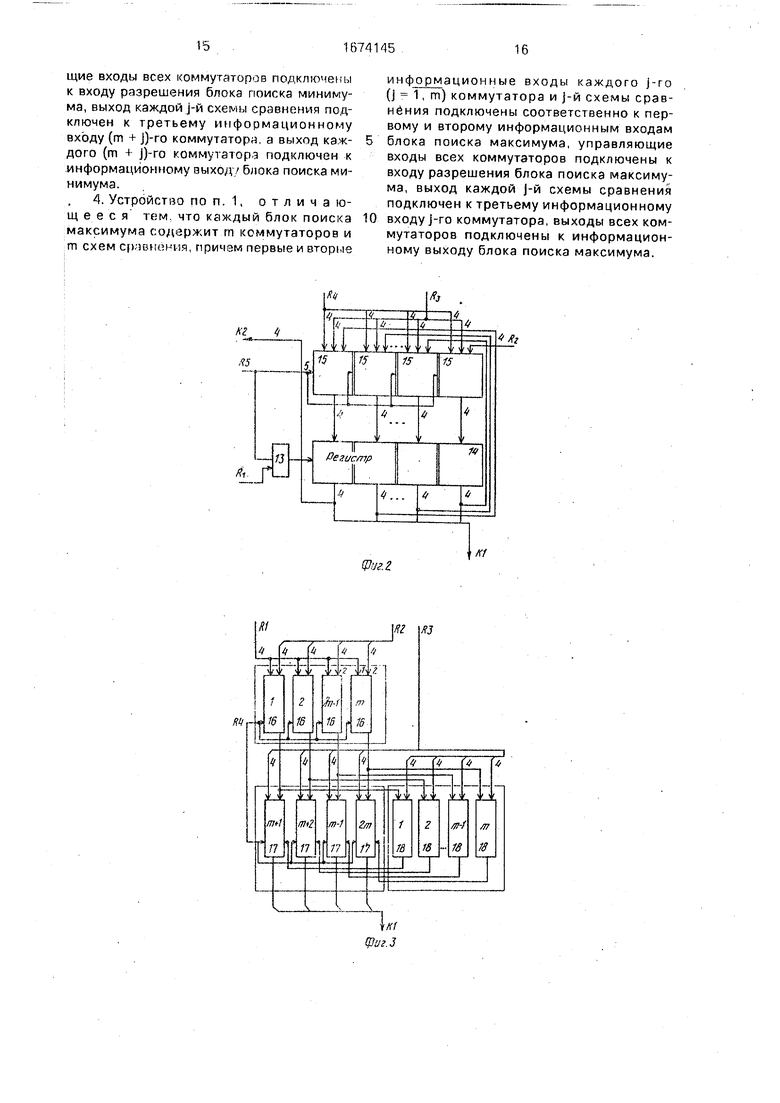

Устройство (фиг. 1) содержит N регистров 1 слова, N блоков 2 памяти, N блоков 3 адреса, регистр 4 команд, дешифратор 5, блок б управления, N блоков 7 поиска минимума, N блоков 8 поиска максимума, N блоков 9 сдвига, арифметико-логический блок 10, счетчик 11 команд, буферный 12 регистр. Блок 9 сдвига (фиг. 2) содержит элемент И 13, регистр 14, m коммутаторов 15, управляющий вход R 5, выход К 2 переноса, первый и второй информационные входы (R3 и R4), вход R2 переноса, информационный К 1 выход.

Блок 7 поиска минимума (фиг. 3) содержит m коммутаторов 16, m коммутаторов 17, m схем 18 сравнения первый и второй (R2 и R3) информационные входы, вход R4 разрешения, информационный выход К1.

Блок 8 поиска максимума (фиг. 4) содержит m коммутаторов 19, m схем 20 сравнения и имеет первый и второй (К 1 и К 2) информационные входы, информационный выход R.

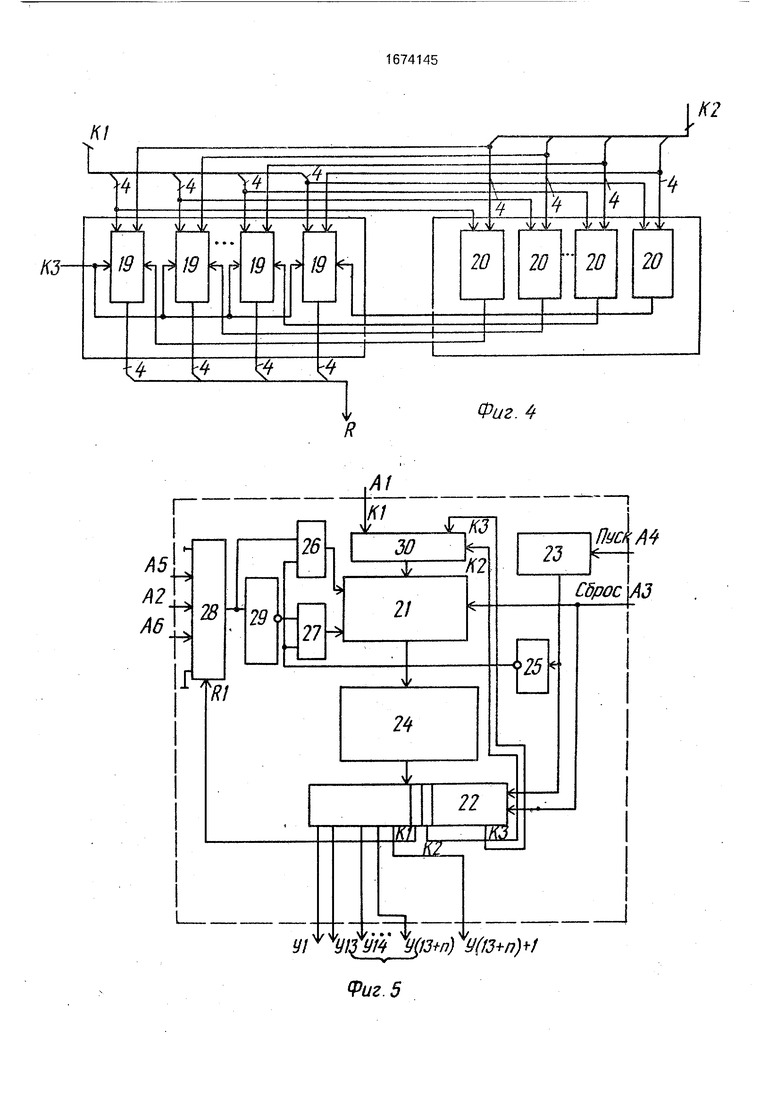

Блок б управления (фиг. 5)содержит счетчик 21 команд, регистр 22 микрокоманд, генератор 23 импульсов, блок 24 памяти, элемент НЕ 25, элементы И 26, 27, коммутаторы 28 управляющих сигналов, элемент НЕ 29, коммутатор 30 и вход А 5 адреса, вход А 2 признака, вход А 6 управления начальной загрузкой, группы входов А 1 кода операции, входы А 3, А 4 сброса и пуска, управляющие выходы У 1У(14 + N).

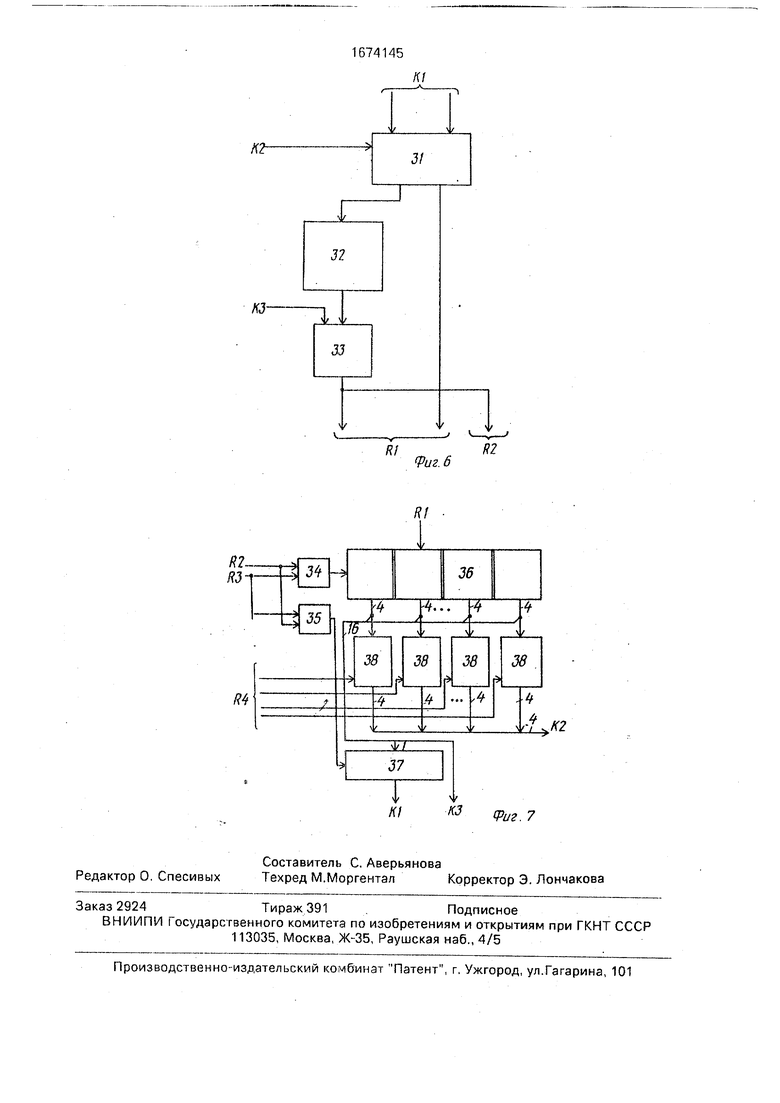

Блок 3 адреса (фиг. 6) содержит коммутатор 31, дешифратор 32 старших разрядов, элемент ИЛИ 33 и вход К 1 адреса, вход К 2 разрешения, вход К 3 управления чтением, выход R 1 адреса, выход R 2 выбора блока памяти.

Блок 7 регистра слова (фиг. 7) содержит элементы И 34, 35, регистр 36, шинный формирователь 37, m шинных преобразователей 38 и информационный вход R 1, вход R 2 выбора блока памяти, вход R 3 разрешения записи считывания, управляющий вход

R 4, первый и второй информационные выходы К 1 и К 3 выход К 2 тетрады.

Устройство предназначено для выполнения логических и арифметических операций над четкими и нечеткими числами. Под

нечеткими числами понимается множество А {/м (X), X}, где// : X ,1 - отображение множества X в единичный отрезок 0,1 - называется функцией принадлежности нечеткого множества А. Значение функции

принадлежности /гд (X) для элементов хСХ называется степенью принадлежности. Интерпретация степени принадлежности МА (X) является субъективной мерой того, насколько элемент xt X соответствует понятию, смысл которого формализуется нечеткими множеством А.

Арифметическое операци над нечеткими числами определяется как

С,0)

где А {/л , ai } - первое нечеткое число; В , bj} - второе нечеткое число, б { max(mln(iA,/)B)}, нечеткое число - результат операции (1);

- знак арифметической операции.

Пусть задано нечеткое множество

А (а|,,Д1Аап/МпА}и нечеткое множество

В(Ь1,/л bm.jUm ), тогда в соответствии

с формулой (1) для каждой пары значений из области определения нечетких множество

для операции сложения запишем:

(uiB,Ui ), 31 +bi;...;...; min(uiA,,MmB)31 +bm

mln(wnA /ЛВ), an + bi;...; min//nA ,mB)an+bm

(2)

Предположим, что все нечеткие множества, участвующие в операции, заданы на области определения с одинаковым шагом Л, т.е. Э2 - ai ... ап - ап-1 ДА;

D2- Ь1 ... Ьп -bn-1 Лв.(3)

Это требование выполнимо, так как если Дд Дв, то множество заданное с большим шагом, можно доопределить или убрать промежуточные значения в множестве, заданном с меньшим шагом. Тогда, опираясь

0 на выражение (3) и анализируя матрицу (2), имеем

a2 + bi-(ai+ Д)+bi ai+(bi + Д) ai + Ьг; аз + bi 32 + b2 ai + Ьз и т.д.

Модифицируем матрицу (2) так, чтобы в одном столбце находились значения искомого нечетного множества относящиеся к одной и той же точке области определения, т.е.

min () min (

л Э .

mln (//2Av«i

V ,min («2H,//m 1 )

I

max

, , min («пА,) min (//nA//2B) . min (un )

; i ; , i

max

max

max

В соответствии с формулой (1) максимумы, взятые по столбцам матрицы (4), дадут значение функции принадлежности искомого нечеткого множества С соответственно в точках

(ai + bi), (ai + 02),..., (ai + bm), (az + bm)(an + bm).

Заметим, что количество точек, на котором задано найденное нечеткое множество, не более чем в два раза минус единица больше, чем наибольшее исходное множество. Алго- ритм выполнения арифметических операций сложения и вычитания, который реализует данное устройство, разработан на основе выражения (4). В начале параллельно производится поиск mln no первой строке, затем max по столбцам и сдвиг на одно значение функции принадлежности, Очевидно, что первая операция max будет производиться над первой строкой выражения (4) и строкой с нулевыми значениями, т.е. регистр, формирующий максимальное значение по столбцам, должен быть обнулен перед началом операции.

Далее параллельно производится поиск mln по второй строке, max под найденной строкой и содержимым регистра формирующего max по столбцам, а затем сдвиг полученного результата на одно значение функции принадлежности и т.д. до последней строки матрицы (4).

Описанный алгоритм позволяет реализовать арифметические операции сложения и вычитания нечетких множеств. Устройство реализует также логические операции обьединения (V), пересечения (Д) нечетких множество и операции с четкими числами

(+; -).

Рассмотрим работу устройства.

Для задания одного значения (одной точки)функции принадлежности нечеткого множества используется четыре двоичных разряда, т.е. выделяется шестнадцать субьективных уровней степени принадлежности. При использовании шестнадцатиразрядных блоков памяти в одном слове одного блока памяти может храниться четыре значения функции принадлежности.

Рассмотрим работу устройства при выполнении арифметических и логических операций с четкими числами. Работа уст- ройства начинается с подачи сигнала

min (// Vn/ )i

; i ; , i

max

max

Сброс на вход А 3 блока 6 управления. Этот сигнал поступает на первый вход счетчика 21 и первый вход регистра 22 микрокоманд и устанавливает их в нулевое состояние. По приходу сигнала Пуск на вход А 4 блока б управления генератор 23 импульсов выдает импульс, который поступает на второй вход регистра 22 микрокоманд. По переднему фронту этого импульса регистр 22 микрокоманд записывает информацию, считанную из нулевой ячейки блока 24 памяти (из нулевой ячейки, так как счетчик 21 после подачи сигнала Сброс обнулен). Задний фронт синхроимпульсов через элемент НЕ 25 подается на первые входы элементов И 26 и 27 и стробирует сигнал из коммутатора 28. Если в микрокоманде, считанной из нулевой ячейки блока 24 памяти, отсутствует сигнал разрешения для коммутатора 28, который поступает на его вход R 1 с выхода К 1 регистра 22 микрокоманд, то тогда на его выходе присутствует сигнал О, который через элемент НЕ 29 поступает на второй вход элемента И 27 и обеспечивает выработку сигнала на второй вход счетчика 21. При поступлении сигнала на второй вход счетчика 21 адрес увеличивает свое состояние на единицу. Увеличенный на единицу адрес с выхода счетчика 21 адреса микрокоманд поступает на вход постоянного запоминающего устройства 24. на выходе которого появляется информация из адресованной ячейки. По переднему фронту следующего импульса информация с выхода постоянного запоминающего устройства 24 будет записана в регистр 22 микрокоманд и весь процесс повторится, как описано. Таким образом выполняются линейные участки микрокоманд. При необходимости осуществить переход по адресу, подаваемому на входА1 блока 6 управления и поступающего на вход К 1 коммутатора 30, с выхода К 1 регистра 22 микрокоманд на вход R 1 коммутатора 28 поступает управляющий вход, пропускающий на выход коммутатора 28 1 с его входа А 2. С выхода К 2 регистра 22 микрокоманд поступает сигнал на вход К 2 коммутатора 30, обеспечивая пропуск информации, адреса первой микрокоманды микропрограммы, с входа К 1 коммутатора 30 на вход счетчика 21. По заднему фронту

синхроимпульса с генератора 23 элемента И 26 и выдаст сигнал на вход записи счетчика 21. Счетчик 21 запишет адрес первой микрокоманды микропрограммы и по этому адресу будет выбрана микрокоманда из блока 24 памяти. Таким образом, происходит переход к микропрограммам реализации команды. При необходимости осуществить ветвление в микропрограмме по логическим условиям, поступающим на входы А 2 и А 3 блока 6 управления, с выхода К 1 регистра 22 микрокоманды на вход R 1 коммутатора 28 поступает код, пропускающий на выход интересующее условие.,С выхода К 2 регистра 22 микрокоманд навходК. 2 коммутатора 30 поступает сигнал, настраивающий коммутатор 3, на пропуск адреса, поступающего с выхода КЗ регистра 22 микрокоманды через коммутатор 30 на вход счетчика 21 адреса микрокоманд. По заднему фронту синхросигнала при наличии на выходе коммутатора 28 управляющего сигнала 1 срабатывает элемент 1426 и произойдет запись адреса в счетчик 21 микрокоманд. При отсутствии интересующего сигнала на выходе коммутатора 28 (О) срабатывает элемент И 27 и счетчик 21 увеличивает свое состояние на единицу. Таким образом производится ветвление в микропрограммах.

Пусть в регистре 4 команд находится команда сложения двух операндов, находящихся по адресам А1 и А2 в блоках 2 памяти. Код операции команды с выхода кода операции R 2 регистра 4 команд через дешифратор 5 поступит на вход А 1 блока 6 управления и поэтому коду будет осуществлен переход на микропрограмму выполнения команды. В первой микрокоманде адрес первого операнда с выхода адреса регистра 4 команд поступает на первые входы всех блоков 3 адреса. Управляющие сигналы У 3 и У 4, поступающие на входы разрешения К 2 блоков адреса, настраивают коммутаторы в блоках 3 адреса на пропуск адреса первого операнда. Младшие разряды адреса с первого выхода коммутаторов 31 сразу идут на выход R 1 адреса блоков адреса, а старшие - на дешифратора 32. Если код старших разрядов адреса соответствует номеру блока 2 памяти, то на выходе дешифратора 32 появляется сигнал 1 Этот сигнал поступает на первый вход элемента ИЛИ 33, выход которого вместе с выходом коммутатора 31 представляет выход Р 1 адреса блоков адреса. Выход элемента ИЛИ 33 подается на вход R 1 адреса в блоки 2. Таким обрэзом, блоки адреса по старшим разрядам адреса инициируют только один модуль из блоков 2 памяти, а младшие разряды - конкретную ячейку в этом модуле. Адрес первого операнда после дешифрации в блоках 3 адреса поступит на вход R 1 адреса блока 2 памяти, су ин из которых

будет инициирован по входу R 1 адреса.

На его вход управления записи/чтения подан управляющий сигнал у 7, задающий режим чтения. Информация, считанная с I- го из модулей блоков 2 памяти поступит на

0 информационный вход R 1 1-го регистра 1 слова. На вход R 2 выбора блока памяти 1-го ре истра 1 поступает сигнал дешифрации адреса с выхода R 2 выбора блока памяти блока 3 адреса. В l-ом блоке регистра слова

5 он поступит на первые входы элементов И 34 и 35, на вторые входы которых поданы соответственно сигналы Запись в регистр и Чтение из регистра. Таким образом, информация с выхода 1-го блока 2 памяти будет

0 записана в регистр 36 1-го регистра 1 слова и с его выхода через шинный формирователь 37 и магистраль будет подана на первый вход буферного регистра 12, где и будет записана по заднему фронту управляющего

5 сигнала У 12. Во второй микрокоманде информация, выбранная из блока 2 памяти по адресу второго операнда, будет подана на первый информационный вход К 1 блока 10, на втором информационном входе К 2 кото0 рого присутствует информация, выбранная по адресу второго операнда. На третий вход блока 10 с второго выхода блока 6 управления поступает код, задающий операцию сложения в блоке 10. Результат операции с

5 выхода блока 10 поступает на вторые ин- формацинные входы R 4 всех блоков сдвига. Коммутаторы 15 блоков 9 настроены управляющим сигналом У 6 на пропуск информации с третьего информационного входа

0 коммутаторов 15 на входы 2т+1 регистра 14. Информация будет записана в регистр 14, так как на его входе разрешения будет присутствовать сигнал с выхода элемента И 13. На втором входе элемента И 13

5 присутствует управляющий сигнал У б, а на первом входе элемента И 13 присутствует сигнал разрешения записи из соответствующего 1-го блока 3 адреса. При выполнении третьей микрокоманды информация из ре0 гистра 14 соответствующего 1-го блока 9 по управляющему сигналу У 7 будет записана в ячейку памяти в i-ом блоке 2 памяти. Причем результат операции в соответствии с предложенным алгоритмом загру5 жается по адресу второго операнда. Таким образом, за три микрокоманды была выполнена операция сложения двух четких операндов. На данной структуре могут быть реализованы и иные алгоритмы арифметических операций.

Рассмотрим теперь выполнение команды логического умножения (пересечения) нечетких операндов. В первой микрокоманде адрес первого нечеткого операнда поступает с первого выхода адреса регистра 4 команд на К 1 адреса блоков 3 адреса. Причем старшие разряды адреса могут не задаваться, так как нечеткий операнд задан на всех модулях оперативного запоминающего устройства параллельно. Коммутатор 31 блоков 3 адреса настроен управляющими сигналами У 3 и У 4, поступающими на вход К 2 разрешения блоков 3 адреса, на пропуск адреса первого операнда. Причем младшие разряды адреса с выхода коммутатора 31 непосредственно поступают на выход R 2 адреса блоков 3 адреса, а сигнал выбора блока памяти формируется параллельно по всем блокам 2 памяти. На третий вход К 3 управления чтением блоков 3 адреса посту- пает управляющий сигнал У 5. Он поступает на второй вход элементов ИЛИ 33 блоков 3 адреса и независимо от выхода дешифратора 32 формирует на выходе элемента ИЛИ 33 сигнал выбора блока памяти для всех блоков 2 памяти параллельно,

По сигналу чтения управляющий сигнал У 7, информация из всех блоков 2 памяти считывается и поступает на информационный вход R 1 всех регистров 1 слова парал- лельно. По управляющему сигналу У 13, поступающему на вход R 3 разрешения записи/считывания всех регистров 1 слова, и при наличии сигнала выбора блока памяти, поступающего на входы R 2 всех регистров 1 слова с выхода R 2 всех блоков 3 адреса, произойдет запись первого нечеткого операнда в регистр 36 каждого регистра 1 слова. В следующей микрокоманде по адресу второго операнда параллельно из блоков 2 памяти будет считан второй нечеткий операнд и поступит на вторые информационные входы R 3 блока 7 поиска минимума. На первый информационный вход R 2 блока 7 с выхода второго информационного К 3 реги- строе 1 слова подан первый нечеткий операнд. Управляющий сигнал У 10-, поданный на вход R 4 разрешения блоков 7, настраивает коммутаторы 16 на пропуск информации, поступающей на информационный вход R 2 блока 7. С выхода коммутаторов 16 первый нечеткий операнд поступает на первые входы схем 18 сравнения, на вторых входах которых присутствует второй нечеткий операнд, поступающий на вход R 3 бло- ков 7. Схемы 18 сравнения производят потетрадное сравнение двух нечетких операндов параллельно по всем блокам 7 и настраивают коммутаторы 17 на пропуск наименьшего.Таким образом, на выходе блоков 7 формируется результат логической операции умножения (пересечения) нечетких операндов. Управляющие сигналы У 8 и

9,поступающие на входы К 3 разрешения блоков 8 поиска максимума, настраивают их коммутаторы 19 на пропуск сформированного результата операции логического умножения с первого информационного входа К 1 на выход блоков 8. Результат операции поступает на первые информационные входы R 3 блоков 9 сдвига и записывается в регистры 14 этих блоков. В следующей микрокоманде результат операции из регистров 14 блоков 9 записывается параллельно в блоки 2 памяти по адресу первого или второго операндов в соответствии с микропрограммой,

Рассмотрим выполнение команды логического сложения (объединения) нечетких операндов. В первой микрокоманде первый операнд параллельно считывается из блоков 2 памяти. По управляющим сигналам,У

10,У 8 и У 9 он без изменения передается через блоки 7, блоки 8 и записывается в регистры 14 блоков 9 сдвига. Во второй микрокоманде второй нечеткий операнд параллельно считывается из блоков 2 памяти и по управляющему сигналу У 10 он без изменения пропускается через блоки 7 и поступает на первые информационные входы К 1 блоков 8, на вторых информационных входах К 2 которых присутствует первый нечеткий операнд, считанный в первой микрокоманде и запомненный в регистре блоков 9 сдвига. Первый и второй нечеткие операнды потетрадно поступают соответственно на вторые и первые входы схем 20 сравнения, где сравниваются. Схемы 20 сравнения настраивают соответственно коммутаторы 19 таким образом, что на их выходе формируются потетрадные максимумы, т.е. результат операции логического сложения нечетких операндов. По заднему фронту управляющего сигнала У 6 результат операции параллельно записывается в регистр 14 всех блоков 9. В следующей микрокоманде осуществляется запись результата операции из регистров 14 блоков 9 в блок 2 памяти по адресу первого или второго операндов. Рассмотрим выполнение операции арифметического сложения. В отличие от логических операций операнды в арифметических операциях имеют вдвое меньшую длину, т.е. результат арифметических операций вдвое длиннее наибольшего из операндов.

Адреса первого и втрого операндов подаются с выхода адреса регистра 4 команд на входы К 1 адреса блоков 3 адреса. Причем управляющий сигнал У 3, поступающий на входы К 2 разрешения i-ых блоков 3 адреса

i 1, N/2), обеспечивает подачу адреса перого операнда на входы адреса для первой оловины блоков 2 памяти. Управляющий игнал У 4 обеспечивает подачу адреса втоого операнда на входы адреса для второй оловины блокои2 памяти. По управляющеу сигналу У 7, поступающему на входы R 3 правления записью/чтением блока 2 памя- и, происходит считывание первого и второго операндов из блоков памяти, а по правляющему сигналу У 13, поступающему на входы R 3 регистров 1 слова, происходит запись первого операнда в первую половину регистров 1 слова, а второго операнда - во вторую половину регистров 1 слова. В следующей микрокоманде по управляющему сигналу У 14. поступающему на управляющий вход R 4 первого регистра 1 слова, происходит считывание первой тетради регистра 36 через шинный формирователь 37 в магистраль на выход К 2 тетради первого регистра 1 слова. Упрапляющий сигнал У 10, поступающий на входы R 4 разрешения блоков 7, настраивает коммутаторы 16 так, что на выход они пропускают информацию с первых своих выводов.

Т.е. на выходах всех коммутаторов 16, а значит и на первых входах схем 18 сравнения появляется старшая тетрада первого операнда. На вторые входы схем 18 сравнения второй половины блоков 7 подан второй нечеткий операнд. Схемы сравнения настраивают коммутаторы 17 второй половины блоков на пропуск наименьшего. Таким образом, на выходах второй половины блоков 7 формируется первый промежуточный результат. Далее упраляющий сигнал У 8, поступающий на входы К 3 разрешения первой половины блоков 8, настраивает их на пропуск операнда с втпрсг пхода. Вторая половина блоков 8 сравнивает первый,про- межуточный результат с содержимый второй половины блоков 9 сдвига и потетрадно формирует наибольшее. Отметим, что перед началом выполнения команды необходимо обнулить вторую половину блоков 9 сдвига или не выполнять первый анализ на max, a пропускать информацию с первого входа блоков 8 на выход без изменения. Сформированный результат анализа на max поступает на вторую половину блоков 9 сдвига и по управляющему сигналу У 6 записывается в регистр 14. В следующей, третьей, микрокоманде осуществляется сдвиг содержимого блоков 9 сдвига на четыре разряда влево. Управляющий сигнал У 6 настраивает коммутаторы 15 блоков 9 сдвига на пропуск информации с первого входа, на которые со смещением на тетраду подключены выходы регистра 14. Это обеспечивает параллельный сдвиг на четыре разряда. Отметим, что регистр 14 должен записывать информацию по фронту сигнала записи. R двух следующих микрокомандах осущсст вляется анализ

на min второй тетрады первого операнда с вторым операндом и анализ на max содержимого блоков 9 сдвига с промежуточным результатом анализа на min. Полученный результат запоминается и

0 сдвигается на тетраду влево. Таким образом, за 2- (N/2 т) + 1 микрокоманд будет сформировано множество функций принадлежности, описывающих нечеткое множество результата арифметической операции

5 двух нечетких множеств. Здесь m 4 - разрядность одного блока 2 памяти, а N -- коли- чесгво ее блоков. Точка, ядро, вокруг которого располагается найденное нечеткое множество, находится аналогично ариф0 метической операции над четкими операндами. Арифметическая операция выполняется над ядрами нечетких множеств. Формула изобретения 1. Устройство для обработки нечеткой

5 информации, содержащее N (где N - мощность нечетких множеств-операндов) регистров слова, N блоков памяти, N блоков адреса, регистр команд, дешифратор и блок управления, причем информационный вход

0 каждого i-го (i ---1, N) регистра слова подключен к выходу данных 1-го блока памяти, адресный вход каждого 1-го блока памяти подключен к адресному выходу 1-го блока адреса, входы адреса всех блоков адреса

5 подключены к выходу адреса регистра команд, выход кода операции которого подключен к входу дешифратора, выходы которого подключены к соответствующим входам адреса кода операции группы блока управления, входы признака которого подключены к соответствующим выходам признака регистра команд, первые информационные выходы всех регистров слова подключены к шине операндов магистрали

5 данных устройства, отличающееся тем, что, с целью повышения быстродействия устройства при выполнении арифметико-логических операций под нечеткими данными за счет обеспечения параллельной

0 обработки элементов нечеткого множества, уст ройство содержит N блоков поиска минимума, N блоков поиска максимума, N блоков сдвига, счетчик команд, буферный регистр и арифметико-логический блок, причем пер5 вый информационный вход каждого 1-го блока поиска минимума подключен к второму информационному выходу 1-го регистра слова, второй информационный вход каждого 1-го блока поиска минимума подключен к

выходу данных i-ro блока памяти, вход выбора каждого 1-го блока поиска минимума подключен к выходу тетрады 1-го регистра слова, информационный выход каждого 1-го блока поиска минимума подключен к первому информационному входу 1-го блока поиска максимума, второй информационный вход которого подключен к информационному выходу 1-го блока сдвига и к входу данных 1-го блока памяти, информационный выход каждого 1-го блока поиска максимума подключен к первому информационному входу 1-го блока сдвига, вход разрешения записи которого подключен к выходу выбора блока памяти 1-го блока адреса и к входу выбора блока памяти 1-го регистра слова, вход переноса каждого 1-го блока сдвига подключен к выходу переноса (1+1)-го блока сдвига, вход переноса 1-го блока сдвига подключен к источнику логического нуля устройства, вторые информационные входы всех блоков сдвига подключены к входу кода операции регистра команд, к информационному выходу арифметико-логического блока и к информационному входу счетчика команд, информационный выход которого подключен к выходу адреса регистра команд, вход адреса пуска счетчика команд является входом адреса пуска устройства, управляющий вход счетчика команд подключен к первому выходу блока управления, входы сброса и пуска которого являются входами сброса и пуска устройства, адресный вход блока управления подключен к адресному выходу арифметико-логического блока, первый информационный вход которого подключен к первым информационным выходам всех регистров слов и к информационному входу буферного регистра, информационный выход которого подключен к второму информационному входу арифметико-логического блока, вход кода операции которого подключен к второму выходу блока управления, третий выход блока управления подключен к входам разрешения каждого j-ro блока адреса (где j 1, N/2), четвертый выход блока управления подключен к входам разрешения каждо- го к-го блока адреса (где к (N/2 + 1), N), пятый выход блока управления подключен к входам управления чтением каждого 1-го блока адреса, шестой выход блока управления подключен к управляющим входам каждого 1-го блока сдвига, седьмой выход блока управления подключен к входам управления записью-чтением каждого 1-го блока памяти, восьмой выход блока управления подключен к входам разрешения каждого J-ro (где J 1, N/2) блока поиска максимума, девятый выход блока управления подключен к входам разрешения каждого к-го (где к (N/2 + 1), N) блока поиска максимума, десятый выход блока управления подключен входам разрешения каждого i-ro блока 5 поиска минимума, одиннадцатый и двенадцатый выходы блока управления подключены соответственно к управляющим входам регистра команд и буферного регистра, тринадцатый выход блока управления под- 0 ключей к входам разрешения записи-считывания i-ro регистра слова, управляющие входы каждого 1-го регистра слова подключены соответственно к (13 + )-м выходам блока управления (1 1, N), вход управления

5 начальной загрузкой и (14 + М)-й выход блока управления являются соответственно входом начальной загрузки и выходом управления начальной загрузки устройства. 2. Устройство по п. 1, о т л и ч а ю щ е0 е с я тем, что каждый блок сдвига содержит элемент И, регистр сдвига, m коммутаторов (т 1/4 от разрядности слова блоков памяти), первый вход элемента И является входом разрешения записи блока сдвига, а

5 выход элемента И подключен к входу разрешения записи регистра сдвига, каждый j-й вход которого (j 2, m + 1) подключен к выходу (-1)-го коммутатора, каждый к-й выход регистра сдвига (к 1, т) подключен к

0 информационному выходу блока сдвига, первый выход регистра сдвига подключен к выходу переноса блока сдвига, каждый 1-й выход регистра сдвига (1 2, т) подключен соответственно к первому информационно5 му входу (1-1)-го коммутатора, первый информационный вход т-го коммутатора подключен к входу переноса блока сдвига, второй и третий информационные входы всех коммутаторов подключены соответст0 венно к первому и второму информационным входам блока сдвига, управляющие входы каждого коммутатора соединены с вторым входом элемента И и подсоединены к управляющему входу блока сдвига.

5 3. Устройство по п. 1, отличающееся тем, что каждый блок поиска минимума содержит 2т коммутаторов и m схем сравнения, причем первые и вторые информационные входы каждого J-ro (j 1- m)

0 коммутатора подключены соответственно к входу выбора и первому информационному входу блока поиска минимума, информа- ционные выходы каждого j-ro коммутатора (j 1, т) подключены соответственно к пер5 вым информационным входам (m + j)-ro коммутатора и j-й схемы сравнения, вторые информационные входы каждого (m + j)-ro коммутатора 0 1. гп) и j-й схемы сравнения подключены к второму информационному входу блока поиска минимума, управляющие входы всех коммутаторов подключены к входу разрешения блока поиска минимума, выход каждой j-й схемы сравнения подключен к третьему информационному входу (m + j)-ro коммутатора, а выход каждого (т + j)-ro коммутатора подключен к информационному выход/ блока поиска минимума.

информационные входы каждого j-ro (j 1, m) коммутатора и j-й схемы сравнения подключены соответственно к первому и второму информационным входам блока поиска максимума, управляющие входы всех коммутаторов подключены к входу разрешения блока поиска максимума, выход каждой j-й схемы сравнения подключен к третьему информационному входу j-ro коммутатора, выходы всех коммутаторов подключены к информационному выходу блока поиска максимума.

t гпф

t

дншн

F1

A9V 4™

9V

i

/V

R

1

| Головкин Б.А | |||

| Параллельные вычислительные системы М.: Наука, 1980, с | |||

| Способ получения древесного угля | 1921 |

|

SU313A1 |

| Балашов Е.П,, Смолов Б,В | |||

| и др | |||

| Многофункциональные регулярные вычислительные структуры | |||

| М/ Советское радио, 1978, с | |||

| Упругое экипажное колесо | 1918 |

|

SU156A1 |

Авторы

Даты

1991-08-30—Публикация

1989-07-24—Подача