Изобретение относится к автомати ке и вычислительной технике и предназначено для сравнения трех двоичных чисел и выбора из них большего, среднего или меньшего по величине. Известно устройство для сравнени чисел, содержащее элементы И, ИЛИ, триггеры, элемент И-ИЛИ-НЕ 1. Недостаток устройства заключаетс в том, что оно сравнивает числа и вырабатывает в качестве результата сравнения только сигнал, характеризующий величину заданного числа. Наиболее близким к предлагаемому техническим решением является устройство для обработки цифровой информации, содержащее компараторы, блок мультиплексора, дешифратор, причем входные шины сравниваег зх чи сел соединены с информационными вхо дами компараторов и блок мультиплек сора. Кроме того, это устройство со держит схемы формирования сигнала о нахождении числа за границами интервала 2 . Недостатками этого устройства яв ются низкие функциональные возможности при решении задачи выбора требуемых двоичных чисел и низкое быстродействие, так.как сравнение провод1ится, как минимум, за два т а кт а, Цель изобретения - повышение быстродействия . Поставленная цель достигается тем, что в устройстве выходы компараторов соединены с информационными входами блока анализа результатов, управляющие входы которого подключены к выходу дешифратора, управляющие выходы блока анализа результатов соединены с управляюпдами входами блока мультиплексора, и тем, что в устройстве блок анализа результатов состоит из первой группы элементов И, элементов НЕ, трех групп элементов ИЛИ, трех групп выходных элементов И, выходных элементов ИЛИ, шифратора, причем первые входы первого, четвертого и шестого элементов И первой группы соединены с первым информационным входом блока, который через первый элемент НЕ подключен к первым входам второго, пятого, седьмого и восьмого элементов И первой группы, вторые входы второго и третьего элементов И первой группы соединены со вторым информационным входом блока, который через второй элемент НЕ подключен ко вторым вхоам первого, четвертого, пятого, едьмого и восьмого элементов И первой группы, третьи входы пятого, естого, седьмого и восьмого элеменов И группы соединены с третьим нформационным входом блока, который через третий элемент НЕ подключен К третьим входам первого, второго, третьего и четвертого элементов И первой группы, четвертые входы третьего, пятого и восьмого элементов И Первой группы соединены с четвертым информационным входом блока, который через четвертый элемент НЕ подключен к четвертым входам первого,второго, четвертого, шестого и седьмого элементов И, пятые входы первого и второго элементов И первой группы соединены с пятым информадионным входом блока, который через пятый элемент НЕ подключен к пятым входам третьего, четвертого, пятого,шестого, седьмого и восьмого элементов И, шестые выходы четвертого, шестого, седьмого и восьмого элементов И первой группы соединены с шестым информационным входом блока, который через шестой элемент НЕ подключен к шестым входам первого, второго, третьего и пятого элементов И первой грудпы, выходы седьмого и восьмого элементов И первой группы соединены с первым и вторым входами первого элемента ИЛИ первой группы, второго элемента ИЛИ второй группы и третьего элемента ИЛИ третьей группы, третьи входз л которых подключены к выходам пятого , первого и шестого элементов И первой группы соответственно, выходы второго и третьего элементов И первой группы соединены с первым и вторым входами третьего элемента. ИЛИ первой группы, первого элемента ИЛИ второй .руппы и второго элемента ИЛИ третьей группы, третьи входы которых подключенык выходам первого, шестого и пятого элементов И первой группы соответственно, первые входы второго элемента ИЛИ первой группы,третьего:; элемента ИЛИ второй группы и первого элемента ИЛИ третьей хруппы соединены с выходом четвертого элемента И первой группы, а их вторые вхо,г1Ы подключены к выходам шестого, пятого и первого элементов И первой группы соответственно, выходы элементов ИЛИ первой , второй и третьей групп под- . ключены к первым входам выходных элементов И первой, второй, третьей групп, вторые входы выходных элементов И первой, второй и третьей групп соединены с первым, вторым и третьим гзходами упрс вления блока соответственно, выходы первых выходных элементов И всех групп соединены со входами первого выходного элемента ИЛИ, выходы вторых выходных элементов И всех групп подключены ко входам второго выходного элемента ИЛИ,

выходы третьих выходных элементов И всех групп соединены со входами третьего выходного элемента ИЛИ, входы шифратора соединены с выходами элементов И первой группы.

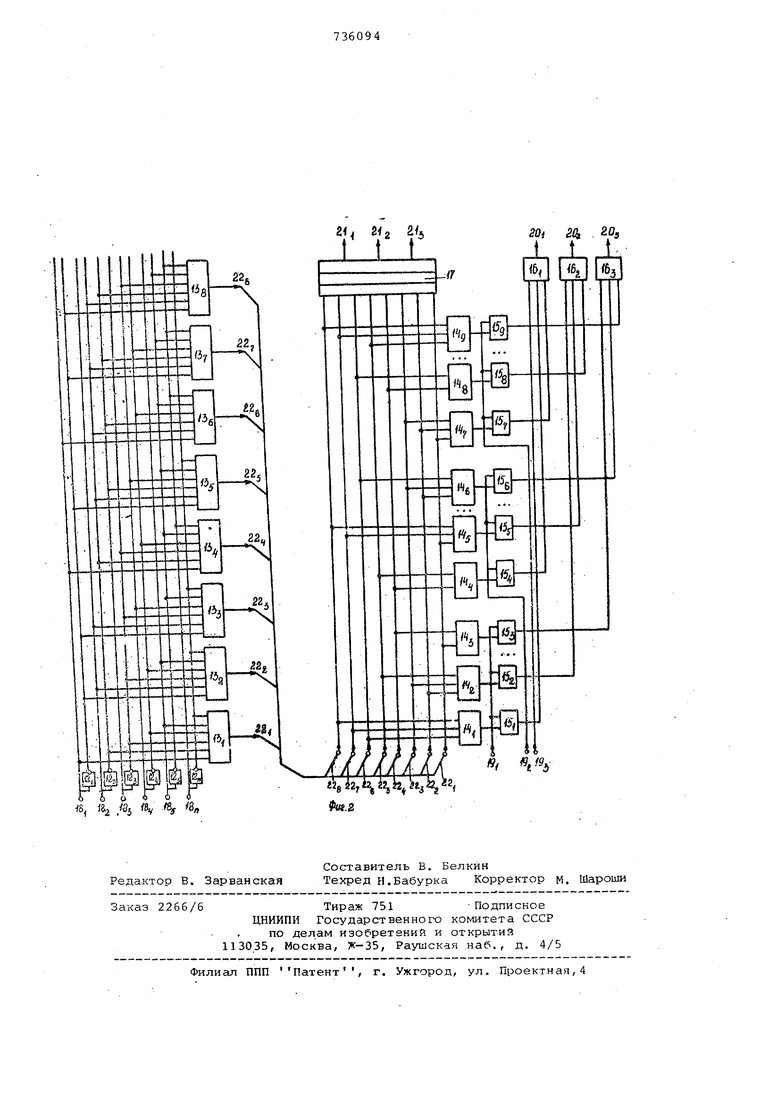

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг, 2 - функциональная схема блока анализа результатов.

Устройство содержит компараторы 1 и 2, блок 3 мультиплексора, дешифратор 4, блок 5 анализа результатов, информационные входы 6, 7 и 8, управляюигие входы 9, выходы 10 и 11 устройства. Блок 5 анализа результатов состоит из элементов НЕ 12,122,...,

5 12 элементов И 1 3, , 1 Зр ,.,., 1 Зд , элементов ИЛИ 1 4 , 1 4 , . . .., 1 4q , элементов И 1 5 , 1 5. , , . . , 1 5q , элементов ИЛИ 16, ., 16g , i6j ,шифратора 17, информационных входов 18 , 1 Bj , . . . , I8g узла, входов i9,19q ,l9j управления выходов 20, ,20 ,20,, ,21, ,21g ,21j , узла, промежуточных связей 22, , 222 , . . ., 22у .

В качестве компараторов 1 и 2 могут быть использованы любые быстродействующие компараторы, позволяю цие сравнивать данное число с двумя другими числами, являющимися границами некоторого интервала.

Блок 3 мультиплексора представляет собой комбинационную схему, которая описывается логической функцией:

Д ХЛ С,

где Д - это одно из чисел А,В или С в зависимости от тока, какой из сигналов YI ,У2 или Y является единичным. Таким образом на выходе 11

выделяется код одного из чисел А, В или С и выделенное число является

либо старшим, либо средним, либо младшим в зависимости от заданного дешифратором 4 режима работы.

Дешифратор 4 предназначен для преобразования двоичного позиционного кода в унитарный и выполняется по любой известной схеме. 1 ифратор 17 (фиг.2) блока 5 анализа результатов предназначен для преобразования унитарного кода в двоичный позиционный и выполняется по любой известной схеме.

Устройство работает следуюцим образом.

На информационные входы 6, 7 и 8 поступают п-разрядные сравниваомгле числа (соответственно А,В и С). Разряды числа А поступают на первые информационные входы компаратора. 1, вторые входы компаратора ., на первые входы блока 3 мультип1е ксора. Разряды числа В поступают чл вторые информационные входы компаратора 1, на первые входы компаратора 2, на вторые входы Рлока 3 tyльтиплeкcopa, Разряды числа .: поступают на третьи входы коьшараторов 1 и 2,блока 3 мультиплексора. Компараторы индицируют случаи , , и В7А, , . Результаты сравнения с выходов- компараторов поступают на блок анализа результатов, который в зависимости от заданного режима работы схема определяет заданное число {больше, меньше, среднее-или отключение устройства) . Режим работы устройства задается управляющим кодом, который подается на входы 9. Дешифрованный код режима работы поступает в блок 5 анализ результатов . Информация о выбранном числе поступает через блок анал за результатов в блок 3 мультиплексора. Пример, Пусть число (код 111), (код 101), (код Oil) и необходимо выбрать сред нее из них. На входные шины 9 дешиф ратора 4 подается двоичный код 10, При этом на входы 18, ,182,18,.,,, I8g блока анализа результатов поступает код lOOOlOiHa выходе 22 эле мента И 13 появится сигнал , который поступает на входы шифратор 17 и элементов ИЛИ 14., , 1 45 , 1 4j , На выходах шифратора 17 появляется дво ичный- код 111, что соответствует соотношению А, В, С. Так как производится выбор среднего из трех чисел, то единичный сигнал подается с дешифратора 4 на вход 192 блока анализа результатов и открывает элементы И 15 , ISj , ,Следовательно, на элемент ИЛИ 16 поступает единичный си нал с выхода элемента ИЛИ 14, С выходной шины 20д блока анализа резу татов сигнал подается на блок 3 мул типлексора и в соответствии с реали зуемой им логической функцией на вх ную шину 11 выдается код числа В, т.е. 101. Следовательно, выбор сред него из трех чисел произведен. При выборе большего и меньшего числа устройство работает аналогично. Предлагаемое устройство имеет большее быстродействие, так как сра нение производится за один такт. Формула изобретения 1, Устройство для обработки цифровой информации, содержащее компараторы, блок мультиплексора, дешифратор, причем входные шины сравниваемых чисел соединены с информационными входами компараторов и бло дмультиплексора, отличающееся тем, что, с целью повышения быстродействия, в нем выходы компараторов соелинены с информационными входами блока анализа результатов, управляющие входы которого подключены к вьлходу дешифр.атора, управляю1цие выходы блока анализа результатов соединены с управляющими входами бло ка мультиплексора. 2, Устройство по п,1,о т л ичающееся тем, что в нем блок анализа результатов состоит из первой группы элементов И, элементов НЕ, трех групп элементов ИЛИ, трех групп выходных элементов И, выходных элементов ИЛИ, шифратора, причем первые входы первого, четвертого и шестого элементов И первой группы соединены с первым информационным входом блока, который, через первый элемент НЕ подключен к первым входам второго, пятого, седьмого и восьмого элементов И первой группы, вторые входы второго и третьего элементов И первой группы соединены со вторым информационным входом блока, который через второй элемент НЕ подключен ко вторым входам первого, четвертого, пятого, седьмого и восьмого элементов И первой группы, третьи вхо,цы пятого, шестого, седьмого и восьмого элементов И групггы соединены с третьим информационным в.ходом блока, который через третий элемент НЕ подключен к третьим входам первого,второго, третьего и четвертого элементов И первой группы, четвертые входы третьего, пятого и BOCbNroro элементов И первой группы соединены с четвертым информационным входом блока, который через четвертый элемент НЕ подключен к четвертым входам первого, второго, четвертого, шестого и седьмого элементов И, пятые входы -первого и второго элементов И первой группы соединены с пятым информационным входом блока, который через пятый элемент НЕ подключен к пятым входам третьего, четвертого, пятого, шестого,седьмого и восьмого элементов И, шестые выходы четвертого, шестого, седьмого и восьмого элементов И первой группы соединены с шестым информационным входом блока, который через шестой элемент НЕ подключен к шестым входам первого, второго, третьего и пятого элементов И первой группы, выходы седьмого и восьмого элементов И первой группысоединены с первым и вторым входам-t первого элеьюнта ИЛИ первой группы, второго элемента ИЛИ второй группы и третьего элемента ИЛИ третьей группы, третьи входы которых подключены к выходам пятого, первого и шестого элементов И первой группы соответственно, выходы второго и третьего элементов И первой группы соединены с первым- и вторым вход:ами третьего элемента ИЛИ первой группы, первого, элемента ИЛИ второй группы и второго элемента ИЛИ третьей группы, третьи входы которых подключены к выходам пе-pBorOf шестого пятого элементов И первой группы

соответственно, первые входы второго элемента ИЛИ первой группы, третьего элемента ИЛИ второй группы и первого элемента ИЛИ третьей группы соединены с выходом четвертого элемента И первой группы, а их вторые входа подключены к выходам шестого, пятого и первого элементов И первой группы соответственно,выходы элементов ИЛИ первой, второй и третьей групп подключены к первым входам выходных элементов И первой, второй и третьей групп, вторые входы выходных элементов И первой, второй и третьей групп соединены с первым, вторым и третьим входами управления блока соответственно,выходы первых выходных элементов И

всех групп соединены со входами пер вого выходного элемента ИЛИ, выходы вторых выходных элементов И всех групп подключены ко входам второго выходного элемента ИЛИ, выходы третьих выходных элементов И всех групп соединены со входами третьего выходного элемента ИЛИ, входы шифратора соединены с выходами элементов И первой группы.

Источники информации, принятые во внимание при экспертизе

1,Авторское свидетельство СССР

№ 478302, кл. G Об F 7/02, 12.03.72,

2.Авторское свидетельство СССР f 310246, кл. G 06 F 7/04, 30.05.65

(прототип),

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения информации | 1982 |

|

SU1076900A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ СОВМЕСТНО ХРАНИМЫХ ГРАНИЦ ПРИ ИНТЕРВАЛЬНЫХ ВЫЧИСЛЕНИЯХ | 2012 |

|

RU2497179C1 |

| Устройство для поворота вектора | 1983 |

|

SU1132285A1 |

| Устройство для контроля дефектов фотошаблона | 1989 |

|

SU1698712A1 |

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Устройство для индикации | 1985 |

|

SU1261005A1 |

| Процессорный модуль | 1985 |

|

SU1343421A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Декодер кодов Рида-Соломона | 1989 |

|

SU1777244A1 |

| Устройство для контроля правильности электрических соединений | 1984 |

|

SU1219987A1 |

Авторы

Даты

1980-05-25—Публикация

1977-02-01—Подача