сравнения, счетчик 10 этапов вычислений и блок синхронизации, включающий генератор 2 тактовых импульсов,

Изобретение относится к вычислительной технике и может быть использовано при построении высокопроизводительных систолических матричных процессоров с программируемой динамической- адаптацией алгоритма обработки и маршрута передачи данных, например при цифровой обработке сигналов и изображений.

Целью изобретения является повышение производительности модуля.

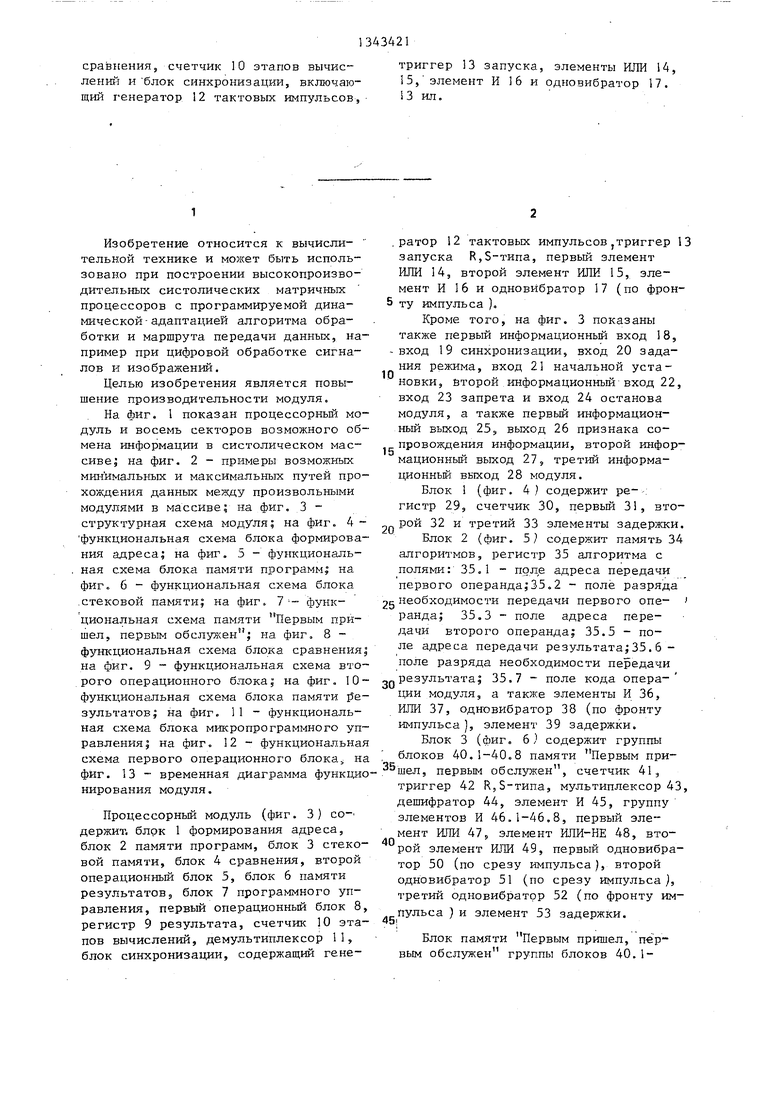

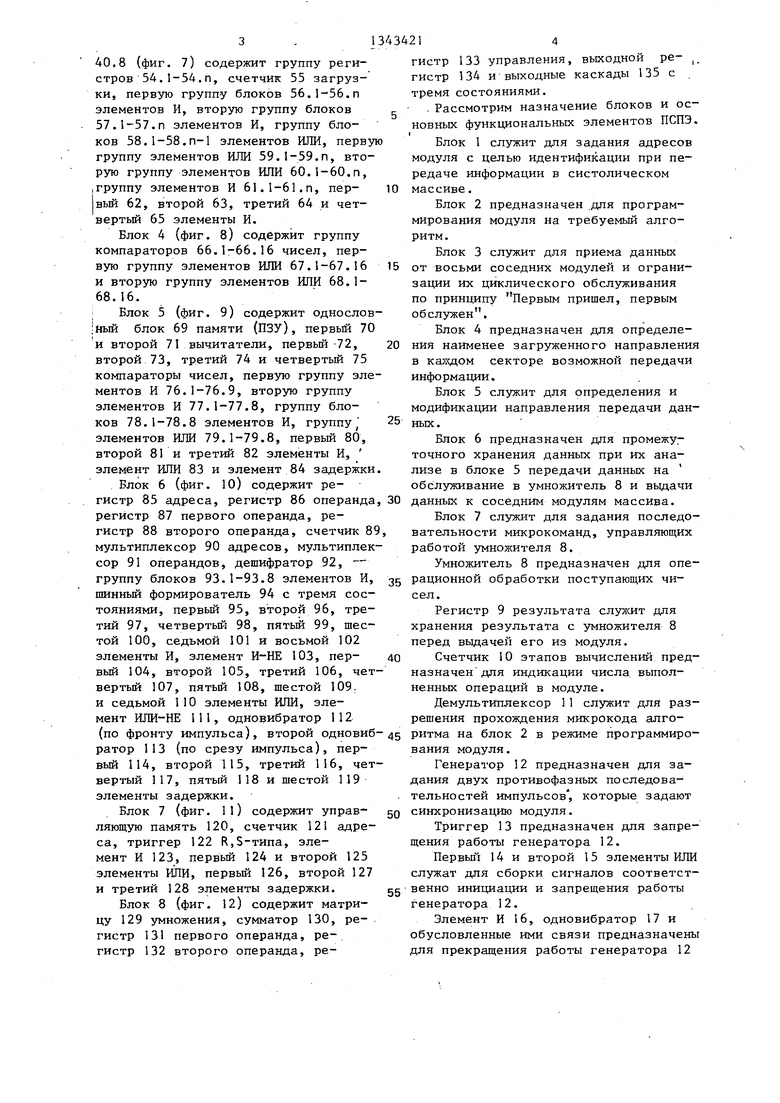

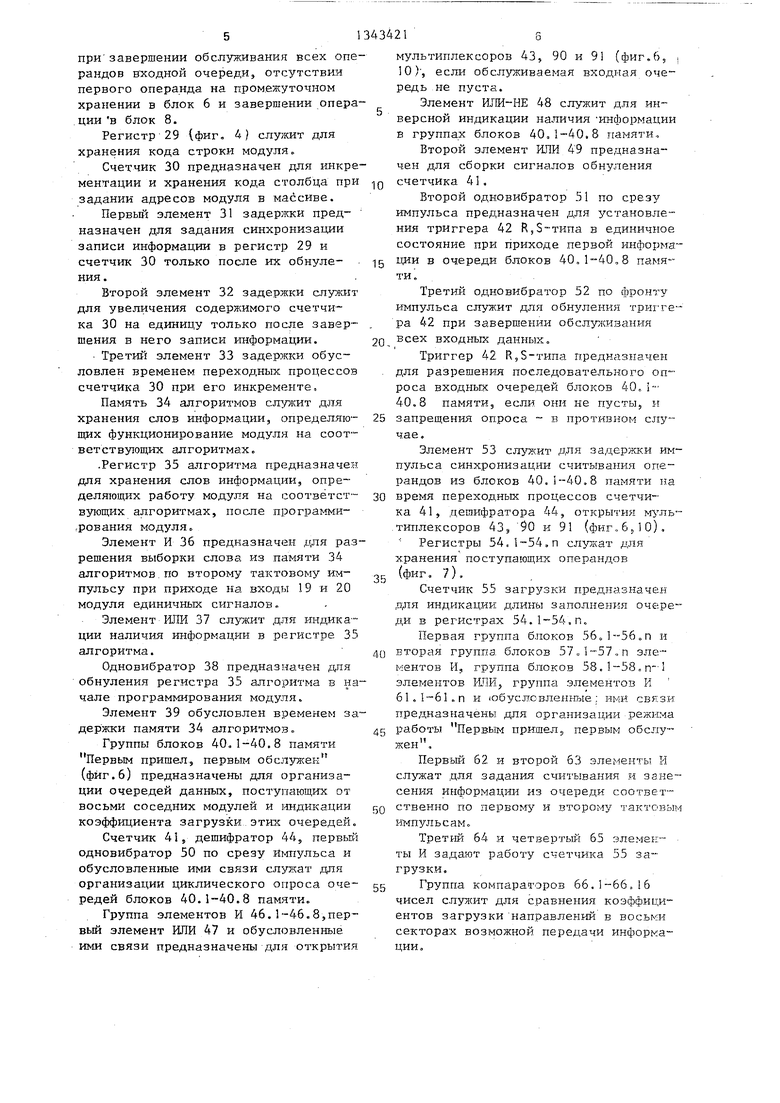

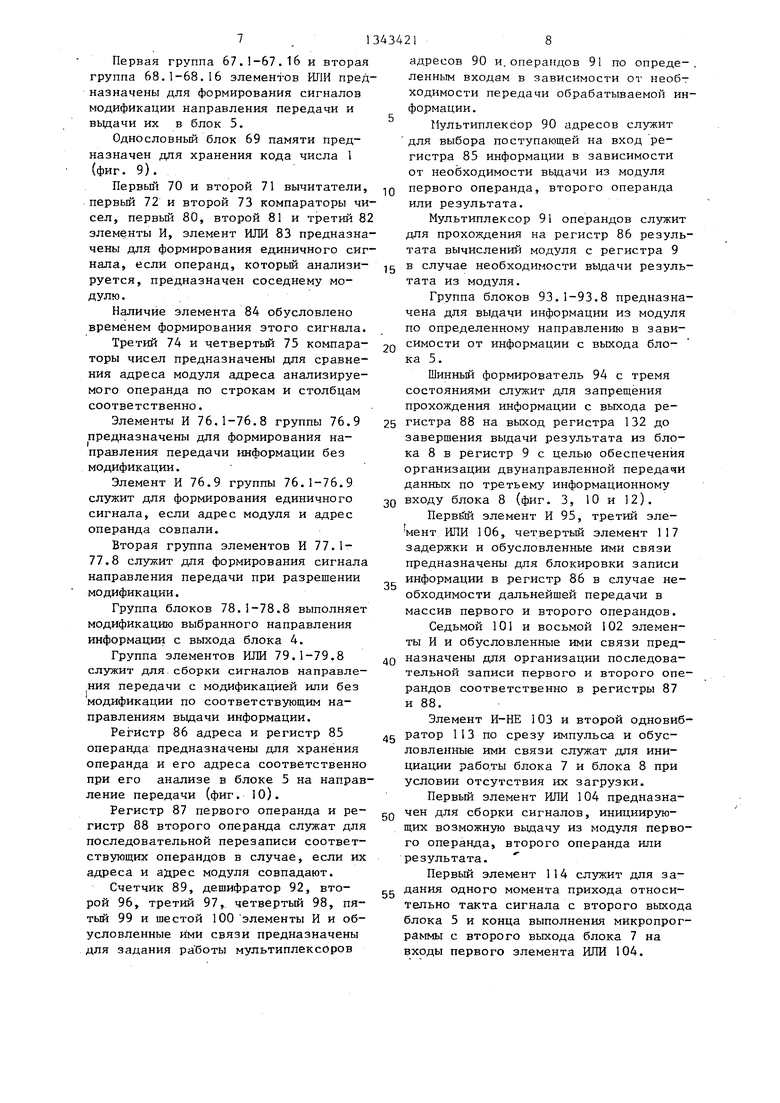

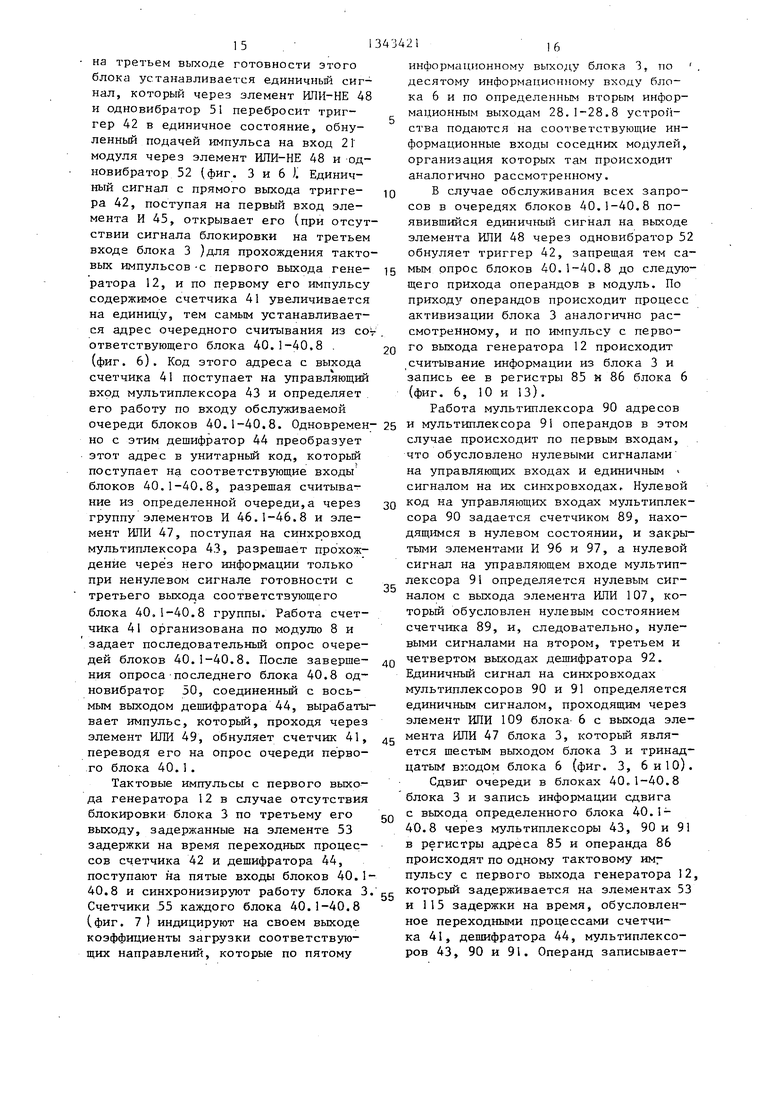

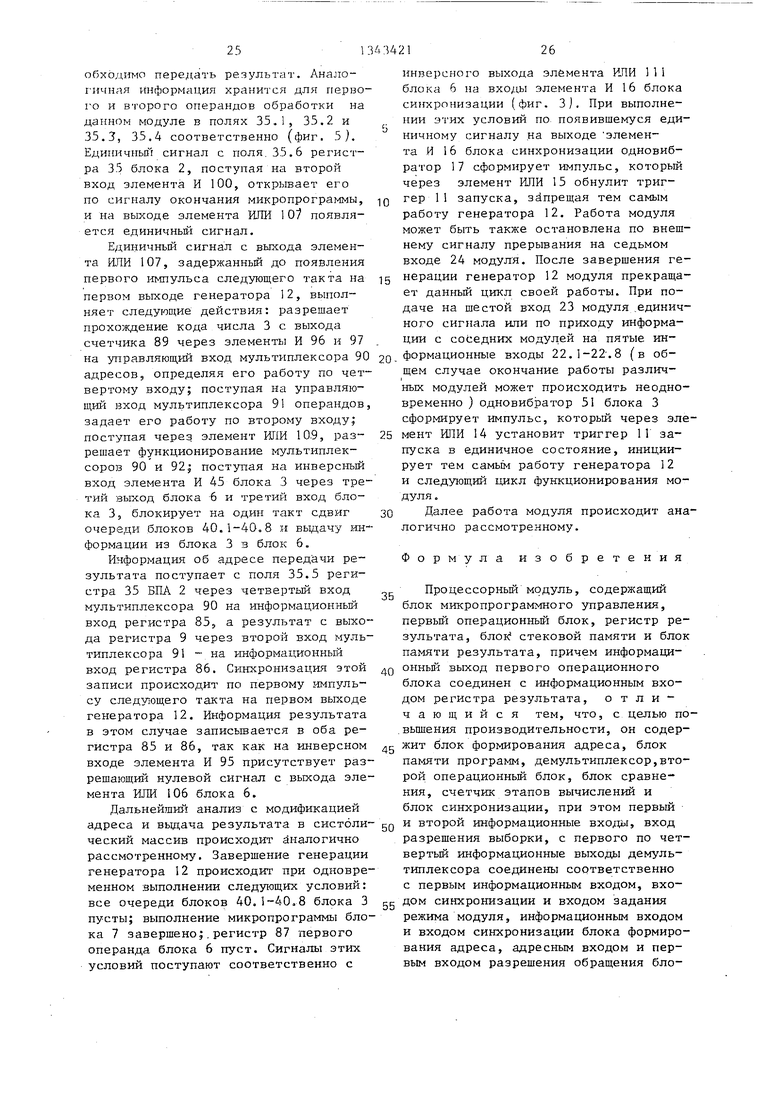

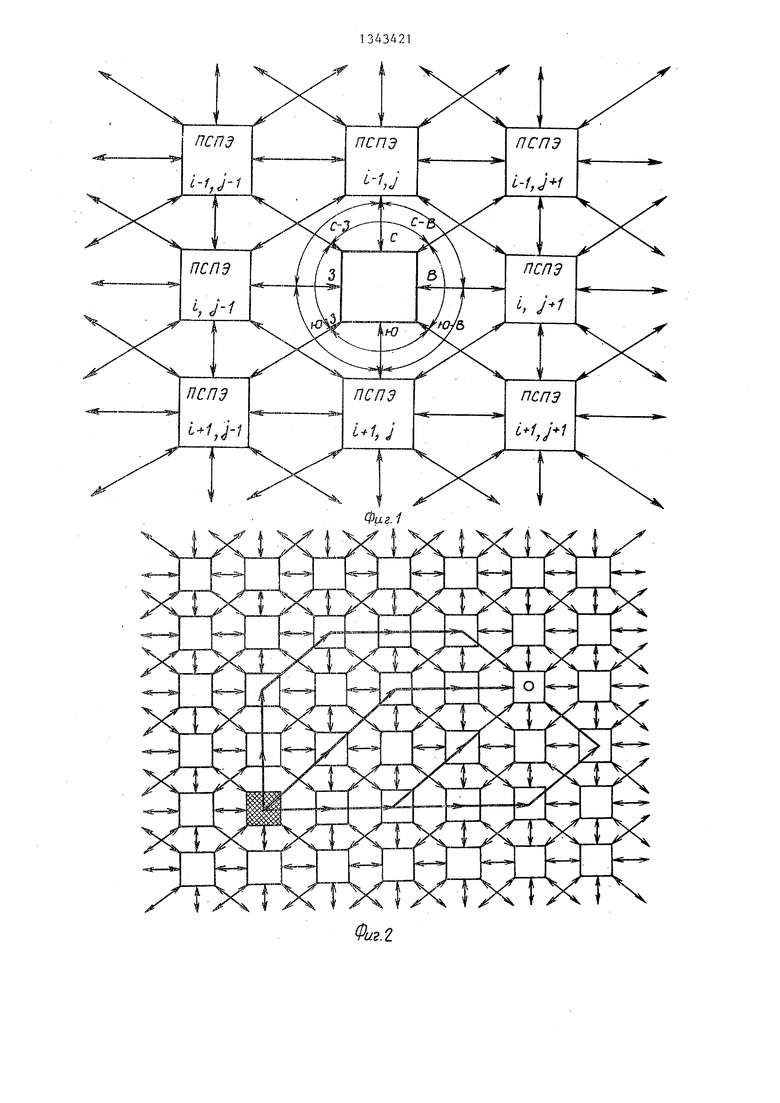

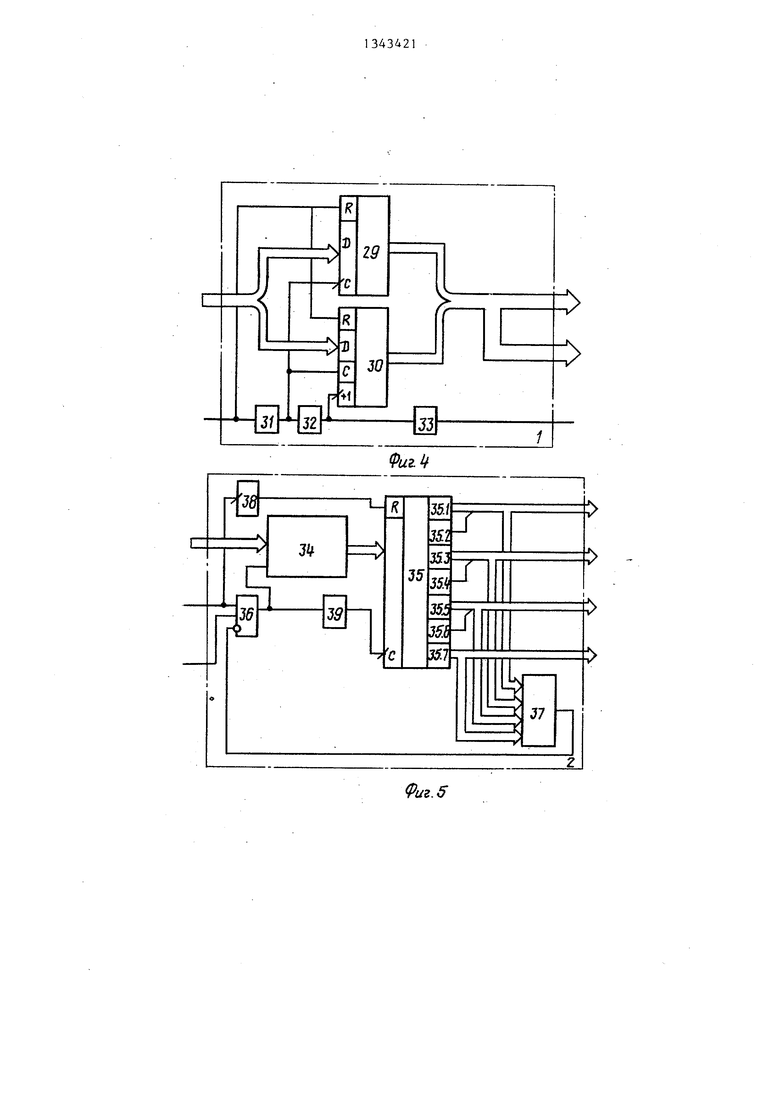

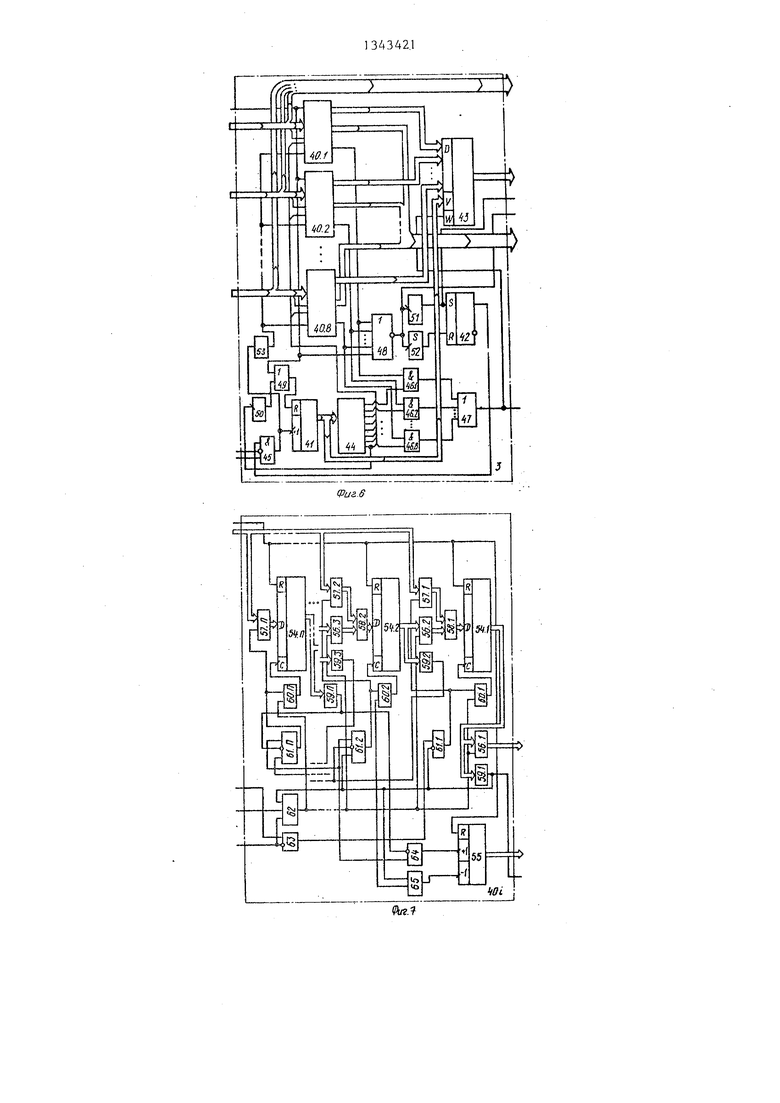

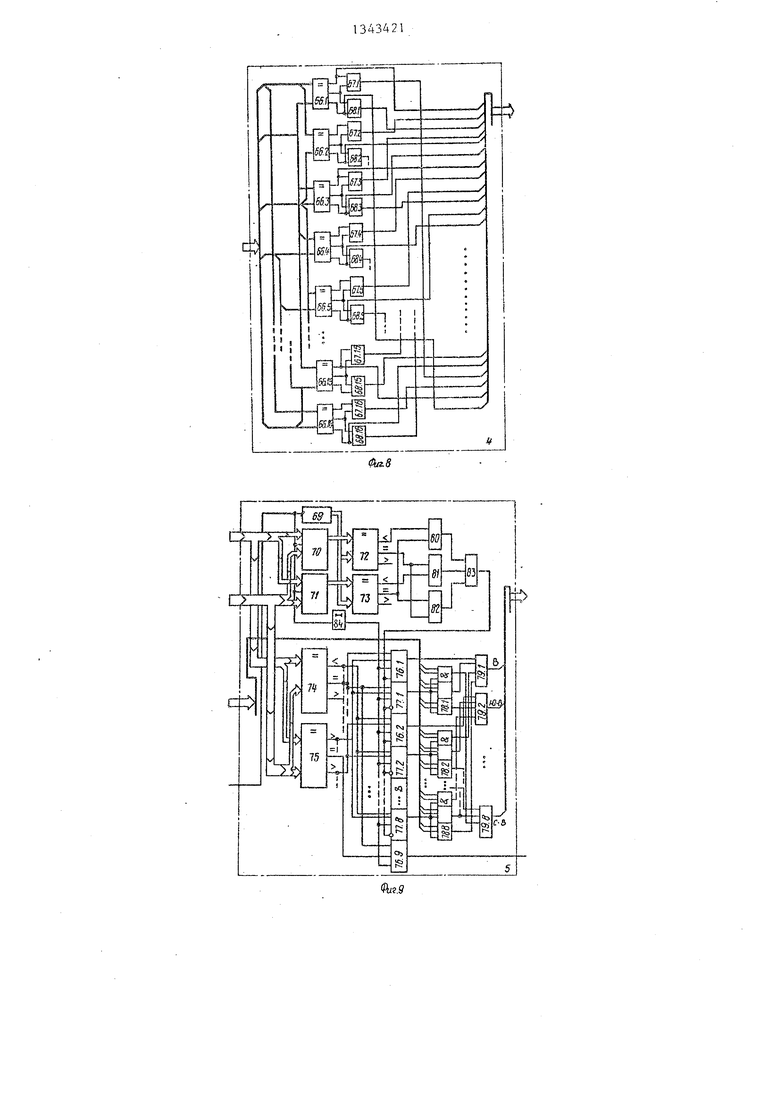

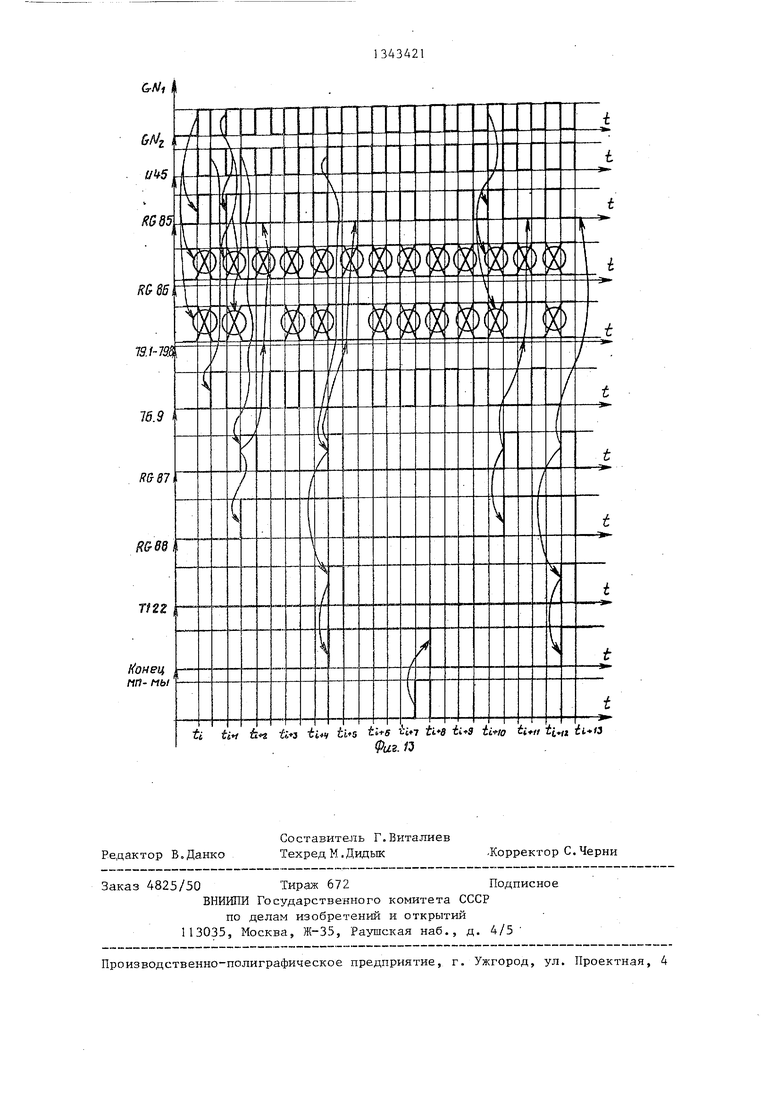

На фиг. I показан процессорньй модуль и восемь секторов возможного обмена информации в систолическом массиве; на фиг. 2 - примеры возможных минимальных и максимальных путей прохождения данных между произвольными модулями в массиве; на фиг. 3 - структурная схема модуля; на фиг. 4 - функциональная схема блока формирования адреса; на фиг. 5 - функциональная схема блока памяти программ; на фиг. б - функциональная схема блока .стековой памяти; на фиг. 1- функциональная схема памяти Первым пришел, первым обслужен ; на фиг. 8 - функциональная схема блока сравнения; на фиг. 9 - функциональная схема второго операционного блока; на фиг. 10- функциональная схема блока памяти результатов; на фиг. 11 - функциональная схема блока микропрограммного управления; на фиг. 12 - функциональная схема первого операционного блока на фиг. 13 - временная диаграмма функционирования модуля.

Процессорный модуль (фит. 3 ) со- держит, блок 1 формирования адреса, блок 2 памяти программ, блок 3 стековой памяти, блок 4 сравнения, второй операционный блок 5, блок 6 памяти результатовэ блок 7 программного управления, первый операционный блок 8, регистр 9 результата, счетчик 10 этапов вычислений, демультиплексор И, блок синхронизации, содержащий генетриггер 13 запуска, элементы ИЛИ 14, 15, элемент И 16 и одновибратор 17. 13 ил.

5

0

5

0

5

0

5

ратор 12 тактовых импульсов,триггер 13 запуска Р,5-типа, первый элемент ИЛИ 14, второй элемент ИЛИ 15, элемент И 16 и одновибратор 17 (по фронту импульса ).

Кроме того, на фиг. 3 показаны также первый информационньш вход 18, вход 19 синхронизации, вход 20 задания режима, вход 21 начальной установки, второй информационньш вход 22, вход 23 запрета и вход 24 останова модуля, а также первый информационный выход 25., выход 26 признака сопровождения информации, второй информационньш выход 27, третий информа- ционньй ВБ1ХОД 2 8 модуля.

Блок 1 (фиг. 4) содержит ре--: гистр 29, счетчик 30, первый 31, второй 32 и третий 33 элементы задержки.

Блок 2 (фиг. Ъ содержит память 34 алгоритмов, регистр 35 алгоритма с полями: 35.1 - поле адреса передачи первого операнда;35.2 - поле разряда необходимости передачи первого one- ранда; 35.3 - поле адреса передачи второго операнда; 35.5 - поле адреса передачи результата;35.6 - поле разряда необходимости передачи результата; 35.7 - поле кода опера- ции модуля, а также элементы И 36, ИЛИ 37, одновибратор 38 (по фронту импульса , элемент 39 задержки.

Блок 3 (фиг. 6) содержит группы блоков 40.1-40.8 памяти Первым пришел, первым обслужен, счетчик 41, триггер 42 Я,5-типа, мультиплексор 43, дешифратор 44, элемент И 45, группу элементов И 46.1-46.8, первый элемент ИЛИ 47S элемент ИЛИ-НЕ 48, второй элемент ИЛИ 49, первый одновибратор 50 (по срезу импульса), второй одновибратор 51 (по срезу импульса третий одновибратор 52 (по фронту импульса ) и элемент 53 задержки.

Блок памяти Первым пришел, первым обслужен группы блоков 40.140,8 (фиг, 7) содержит группу регистров 54, 1-54, п, счетчик 55 загрузки, первую группу блоков 56.1-56.п элементов И, вторую группу блоков 57.1-57.п элементов И, группу блоков 58.l-58.n-l элементов ИЛИ, первую группу элементов ИЛИ 59.1-59.П, вторую группу элементов ИЛИ 60.1-60.п, группу элементов И 61.1-61,п, пер- вьй 62, второй 63, третий 64 и четвертый 65 элементы И.

Блок 4 (фиг. 8) содержит группу компараторов 66.1-66.16 чисел, первую группу элементов ИЛИ 67.1-67.16 и вторую группу элементов ИЛИ 68.1- 68,16,

I Блок 5 (фиг. 9) содержит однослов- :ный блок 69 памяти (ПЗУ), первьй 70 к второй 71 вычитатели, первый-72, второй 73, третий 74 и четвертьй 75 компараторы чисел, первую группу элементов И 76.1-76.9, вторую группу элементов И 77.1-77.8, группу блоков 78.1-78.8 элементов И, группу элементов ИЛИ 79.1-79.8, первый 80, второй 81 и третий 82 элементы И, элемент ИЛИ 83 и элемент 84 задержки

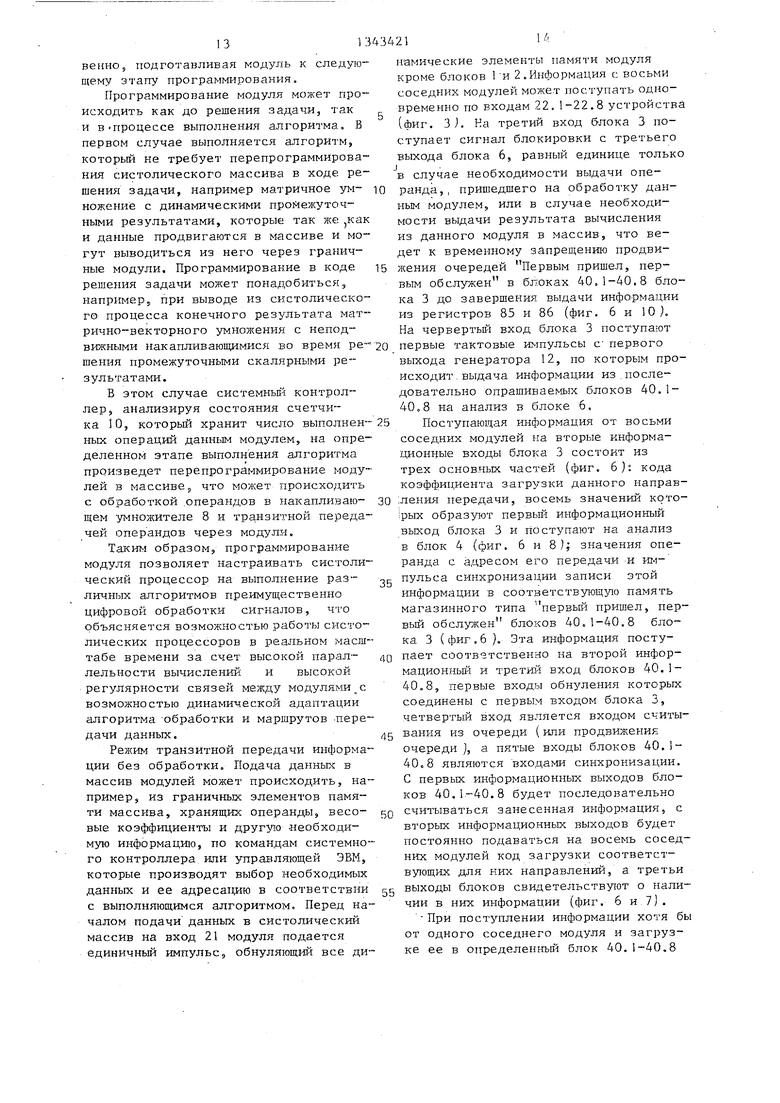

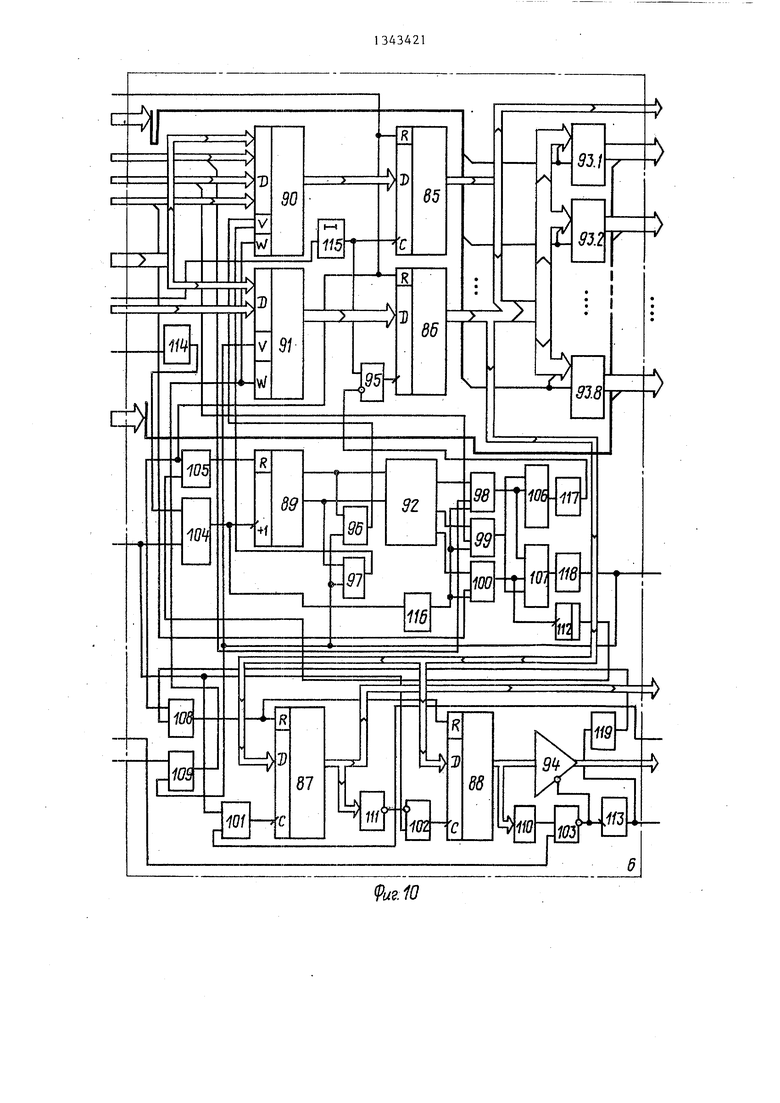

Блок 6 (фиг. 10) содержит регистр 85 адреса, регистр 86 операнда регистр 87 первого операнда, регистр 88 второго операнда, счетчик 89 мультиплексор 90 адресов, мультиплексор 91 операндов, дешифратор 92, - группу блоков 93.1-93.8 элементов И, шинньй формирователь 94 с тремя состояниями, первый 95, второй 96, третий 97, четвертый 98, пятьй 99, шестой 100, седьмой 101 и восьмой 102 элементы И, элемент И-НЕ 103, пер- вьй 104, второй 105, третий 106, четвертьй 107, пятьй 108, шестой 109. и седьмой 110 элементы ИЛИ, элемент ИЛИ-НЕ 111, одновибратор 112 (по фронту импульса), второй одновибратор 113 (по срезу импульса), первый 114, второй 115, третий 116, четвертый 117, пятьй 118 и шестой 119 элементы задержки.

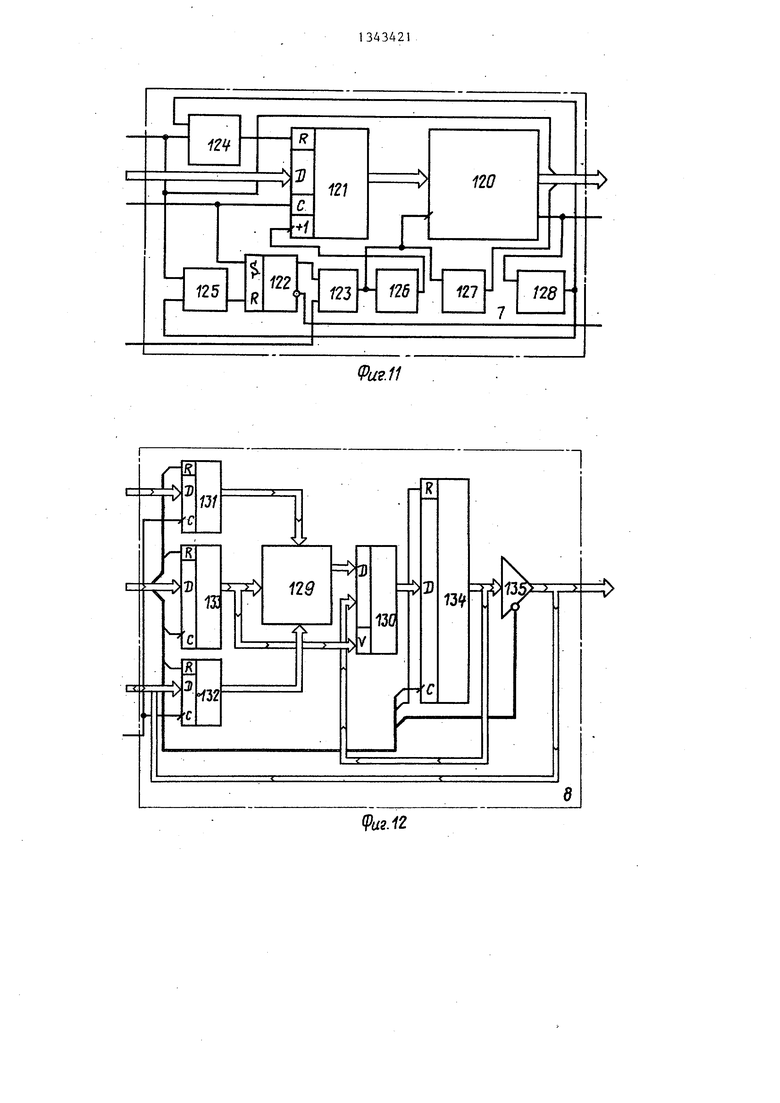

Блок 7 (фиг, 11) содержит управ- ляющую память 120, счетчик 121 адреса, триггер 122 R,S-THna, элемент И 123, первьй 124 и второй 125 элементы ИЛИ, первьй 126, второй 127 и третий 128 элементы задержки,

Блок 8 (фиг. 12) содержит матрицу 129 умножения, сумматор 130, регистр 131 первого операнда, ре-, гистр 132 второго операнда, регистр 133 управления, выходной ре- ,. гистр 134 и-выходные каскады 135 с тремя состояниями.

. Рассмотрим назначение блоков и основных функциональньк элементов ПСПЭ. I

Блок 1 служит для задания адресов

модуля с целью идентификации при передаче информации в систолическом массиве,

Блок 2 предназначен .для программирования модуля на требуемый алгоритм.

Блок 3 служит для приема данных от восьми соседних модулей и ограни- зации их циклического обслуживания по принципу Первым пришел, первым обслужен.

Блок 4 предназначен для определения наименее загруженного направления в кагкдом секторе возможной передачи информации.

Блок 5 служит для определения и модификации направления передачи данных.

Блок 6 предназначен для промежуточного хранения данных при их анализе в блоке 5 передачи данных на обслуживание в умножитель 8 и выдачи данных к соседним модулям массива.

Блок 7 служит для задания последовательности микрокоманд, управл5пощих работой умножителя 8.

Умножитель 8 предназначен для операционной обработки поступающих чисел.

Регистр 9 результата слунсит для хранения результата с умножителя 8 перед выдачей его из модуля.

Счетчик 10 этапов вычислений предназначен для индикации числа выполненных операций в модуле.

Демультиплексор 11 служит для разрешения прохождения микрокода алгоритма на блок 2 в режиме программирования модуля.

Генератор 12 предназначен для задания двух противофазных последовательностей импульсов, которые задают синхронизацию модуля.

Триггер 13 предназначен для запрещения работы генератора 12.

Первьш 14 и второй 15 элементы ИЛИ служат для сборки сигналов соответственно инициации и запрещения работы генератора 12.

Элемент И 16, одновибратор 17 и обусловленные ими связи предназначены для прекращения работы генератора 12

при завершении обслуживания всех операндов Егходной очереди, отсутствии первого операнда на промежуточном хранении в блок 6 и завершении операции в блок 8.

Регистр 29 (фиг, 4) служит для хранения кода строки модуля.

Счетчик 30 предназначен для инкре- ментации и хранения кода столбца при задании адресов модуля в массиве.

Первый элемент 31 задержки предназначен для задания синхронизации записи информации в регистр 29 и счетчик 30 только после их обнуления.

Второй элемент 32 задержки служит для увеличения содержимого счетчика 30 на единицу только после завершения в него записи информации.

Третий элемент 33 задержки обусловлен временем переходных процессов счетчика 30 при его инкременте.

Память 34 алгоритмов сл /окит для хранения слов информации, определяющих функционирование модуля на соответствующих алгоритмах,

.Регистр 35 алгоритма предназначен для хранения слов информации, определяющих работу модуля на соответствующих алгоритмах, после программи- .рования модуля.

Элемент И 36 предназначен для разрешения выборки слова из памяти 34 алгоритмов.по второму тактовому импульсу при приходе на входы 19 и 20 модуля единичных сигналов.

Элемент ИЛИ 37 для индикации наличия информации в регистре 35 алгоритма.

Одновибратор 38 предназначен для обнуления регистра 35 алгоритма в начале программирования модуля.

Элемент 39 обусловлен временем задержки памяти 34 алгоритмов„

Группы блоков 40.1-40,8 памяти Первым пришел, первьш обслужен (фиг.6) предназначены для организации очередей данных, поступающих от восьми соседних модулей и шадикации коэффициента загрузки.этих очередей,

Счетчик 41, дешифратор 44, первый Одновибратор 50 по срезу импульса и обусловленные ими связи служат дпя организации цикличесвгого опроса очередей блоков 40.1-40,8 памяти,

Группа элементов И 46.-46.8,первый элемент ИЛИ 47 и обусловленные ими связи предназначень для открытия.

3434218

мультиплексоров 43, 90 и 9 (фиг.6, | 10)-, если обслуживаемая входная очередь не пуста.

Элемент 48 служит для инверсной индикации наличия информации в группах блоков 40.1-40.8 памяти,

Второй элемент ИЛИ 49 предназначен для сборки сигналов обнуления

счетчика 4I,

Второй Одновибратор 51 по срезу импульса предназначен для установления триггера 42 К,3-типа в единичное состояние при приходе первой информа- ции в очереди блоков 40.1-40,8 памяти.

Третий Одновибратор 52 по фронту импульса служит для обнуления трих-ге- ра 42 при завершении обслулсизания всех входных данных.

Триггер 42 R,S-THna предназначен для разрешения последовательного опроса входных очередей блоков 40.1- 40.8 памяти, если они не пусты, и запрещения опроса - в противном случае.

Элемент 53 слухшт для задержки импульса синхронизации считывания опе-- рандов из блоков 40.Ь-40,8 памяти на время переходных процессов счетчика 41, дешифратора 44, открытия мл ль- типлексоров 43, 90 и 91 (фиг„6,,0).

Регистры 54 Л-54, п сл-уясат для хранения поступающих операндов (фиг, 7),

Счетчик 55 загрузки предназначен для индикации длины заполнения очереди в регистрах 54Л-54.П,

Первая группа блоков 56,1-56оП и вторая группа блоков 57„1--57,п элементов И, группа блоков 58.1-58. элементов РШИ, группа элементов И 61, и (Обусловленные; ими связи: предназначены для организации режима работы Первьм пришел,, первым обслужен,

Первьш 62 и второй 63 элементы И для задания считывания и занесения информации из очереди соответ- ственно по первому и второму тактовым импульсам.

Третий 64 и четвертьш 65 элементы И задают работу счетчика 55 загрузки,

Группа компараторов 66.1-66 Л 6 чисел служит для сравнения коэффициентов загрузки направлений в секторах возможной передачи информации.

7 , 1

Первая группа 67.1-67.16 и вторая группа 68.1-68.16 элементов ИЛИ предназначены для формирования сигналов модификации направления передачи и выдачи их в блок 5.

Однословный блок 69 памяти предназначен для хранения кода числа 1 (фиг. 9).

Первый 70 и второй 71 вычитатели, первый 72 и второй 73 компараторы чисел, первьш 80, второй 81 и третий 8 элементы И, элемент ИЛИ 83 предназначены для формирования единичного сигнала, если операнд, которьй анализируется, предназначен соседнему модулю.

Наличие элемента 84 обусловлено временем формирования этого сигнала.

Третий 7А и четвертьй 75 кокпара- торы чисел предназначены для сравнения адреса модуля адреса анализируемого операнда по строкам и столбцам соответственно.

Элементы И 76.1-76.8 группы 76.9 предназначены для формирования направления передачи шформации без модификации.

Элемент И 76.9 группы 76.1-76.9 служит для формирования единичного сигнала, если адрес модуля и адрес операнда совпали.

Вторая группа элементов И 77.1- 77.8 служит для формирования сигнала направления передачи при разрешении модификации.

Группа блоков 78.1-78.8 выполняет модификацию выбранного направления информации с выхода блока 4.

Группа элементов ИЛИ 79.1-79.8 служит для.сборки сигналов направления передачи с модификацией или без модификации по соответствующим направлениям выдачи информации.

Регистр 86 адреса и регистр 85 операнда предназначены для хранения операнда и его адреса соответственно при его анализе в блоке 5 на направление передачи (фиг. Ю).

Регистр 87 первого операнда и регистр 88 второго операнда служат для последовательной перезаписи соответствующих операндов в случае, если их адреса и адрес модуля совпадают.

Счетчик 89, дешифратор 92, второй 96, третий 97, четвертый 98, пятый 99 и шестой 100 элементы И и обусловленные ими связи предназначены для задания ра боты мультиплексоров

5

0

5

0

5

0

5

0

5

адресов 90 и.операндов 91 по опреде-. ленным входам в зависимости от необходимости передачи обрабатываемой информации.

Мультиплексор 90 адресов служит для выбора поступающей на вход регистра 85 информации в зависимости от необходимости выдачи из модуля первого операнда, второго операнда или результата.

Мультиплексор 91 операндов служит для прохождения на регистр 86 результата вычислений модуля с регистра 9 в случае необходимости выдачи результата из модуля.

Группа блоков 93.1-93.8 предназначена для выдачи информации из модуля по определенному направлению в зависимости от информации с выхода блока 5.

Шинньм формирователь 94 с тремя состояниями служит для запрещения прохождения информации с выхода регистра 88 на выход регистра 132 до завершения выдачи результата из блока 8 в регистр 9 с целью обеспечения организации двунаправленной передачи данных по третьему информационному входу блока 8 (фиг. 3, 10 и 12).

Первйй элемент И 95, третий эле- мент ИЛИ 106, четвертый элемент 117 задержки и обусловленные ими связи предназначены для блокировки записи информации в регистр 86 в случае необходимости дальнейшей передачи в массив первого и второго операндов.

Седьмой 101 и восьмой 102 элементы И и обусловленные ими связи предназначены для организации последовательной записи первого и второго операндов соответственно в регистры 87 и 88.

Элемент И-НЕ 103 и второй одновиб- ратор 1I3 по срезу импульса и обусловленные ими связи служат для инициации работы блока 7 и блока 8 при условии отсутствия их загрузки.

Первьш элемент ИЛИ 104 предназначен для сборки сигналов, инициирующих возможную выдачу из модуля первого операнда, второго операнда или результата.

Первый элемент 114 служит для задания одного момента прихода относительно такта сигнала с второго выхода блока 5 и конца выполнения микропрограммы с второго выхода блока 7 на входы первого элемента ИЛИ 104.

Четвертый элемент ИЛИ 107, пятый элемент -118 заде1 жки и обусловленные ими связи служат для блокировки в случае необходимости продвижения очередей блоков 40.1-40.8 и для задания соответствующего режима работы мультиплексоров 90 и 91.

. Пятый элемент ИЛИ 108 служит для сборки сигналов обнуления регистров 87 и 88.

Шестой элемент ИЛИ 109 предназначен для сборки сигналов, разрешающих работу мультиплексоров 90 и 91.

Седьмой элемент ИЛИ 110 предназна чен для индикации наличия информации в регистре 88.

Элемент ИЛИ-НЕ 111 служит для инверсной индикации наличия информации в регистре 87.

Первый одновибратор 112 по фронту импульса с задержкой предназначен для обнуления счетчика 89 после полного завершения выдачи результата в случае ее необходимости из модуля.

Первый элемент 114 задержки служит для задержки сигнала окончания микропрограммы блока 7 на время переходных: процессов блока 5 с целью корректной организации синхронизации при выдаче результата из модуля.

Второй элемент 115 задержки предназначен дня задержки первого тактового импульса, которьш синхронизирует запись в регистры 85 и 86, на время срабатывания блока 3 по считывани информации и открытия мультиплексоров 90 и 91.

Третий элемент 116 задержки обусловлен переходными процессами счетчика 89 и дешифратора 92.

Шестой элемент 119 задержки предназначен дпя задержки обнуления регистров 87 и 88 на время перезаписи из них информации соответственно в регистры 131 и 132 блока 6 (фиг. 10 и 12).

Управляющая память 120 (фиг. П) предназначена для хранения микропрограмм, задающих работу блока 8.

Счетчик 121 адреса служит для задания естественной адресации выборки информации из управляющей памяти 120 Триггер 122 К,5-типа предназначен для индикации функционирования блока 7.

Элемент И 123 служит для разрешения прохождения вторых тактовых импульсов на вход считывания управлята

0

0

5

5

0

5

0

5

0

5

щей памяти 120 после инициации работы блока 7.

Первый элемент ИЛИ 124 предназначен для сборки сигналов обнуления счетчика 121 адреса.

Второй элемент ИЛИ 125 служит для сборки сигналов обнуления триггера 122.

Первьш элемент 126 задержки предназначен для задержки установки на счетчике 121 нового адреса на время выдачи микрокоманды из управляющей памяти 120.

Второй элемент 127 задержки обусловлен переходными процессами считывания из управляющей памяти 120.

Третий элемент 128 задержки служит для задержки обнуления счетчика 121 и триггера 122 на время выдачи результата из модуля.

Матрица 129 умножения и сумматор 130 блока 8 (фиг. 12) предназначены для реализации операций умножения и сложения.

Регистр 131 первого операнда и регистр 132 второго операнда (фиг. 12) служат для приема на обработку соответственно первого и второго операндов из регистров 87 и 88 блока 6 (фиг. 10).

Регистр 133 управления служит для приема микрокоманд из блока 7 (фиг. 12-).

Выходной регистр 134 предназначен для хранения промежуточных и конечного результатов.

Выходные каскады 135 с тремя состояниями спужат для подключения к внешней шине данных.

Рассмотрим работу процессорного модуля.

Перед началом функционирования каждому модулю в массиве присваивается адрес. Это происходит следующим образом. На входе 20 модуля (фиг. 3) устанавливается нулевой сигнал, тем самым определяется работа мультиплексора 11 по первому выходу. Адресация модуля в массиве происходит по строкам. На входы 18 и 19 левых граничных модулей в массиве подаются соответственно код данной строки с нулевым кодом столбца и единичный импульс синхронизации, которые,проходя через мультиплексор 11, поступают на первый информационньй и второй вход блока 1. Код соответствующей строки поступает на вход регистра 29, а нулевой код

П134342112

столбца - на вход счетчика 30 блока 1, ля 8 происходит по вторым импульсам запись в которые синхронизируется им- тактов работы модуля. Запись информа- пульсом с второго входа блока I, за- дни в очереди блоков 40.-40.8 блодержанным на время обнуления регистра 29 и счетчика 30 (фиг. 4). Затем через время задержки элемента 32, равное времени установления переходных процессов записи информации в регистре 29 и счетчике 30, содержимое счетчика 30 увеличивается на единицу и на выходах регистра 29 и счетчи-- ка 30 индицируется код -адреса даннока 3 происходит по импульсу информации с соседних моделей, т.е. по второму импульсу такта работы модуля в массиве, что задается синхронной работой всех модулей в систолических 10 процессорах в отличие от волновых матриц с асинхронной обработкой информации. Временные диаграммы работы основных блоков модуля без учета принципиальных для его функционирова- мя работы модуля может быть использо- ig ния задержек показаны на фиг. 13. ван с второго информационного выхода Рассмотрим режимы функционирования блока 1. Далее единичный импульс, за- модуля более подробно, держанный на элементе 33 задержки на Режим программирования. В этом режиме происходит программирование мо- 2Q дуля на выполнение определенных функций, обусловленьпзК конкретными этапами алгоритма, на которых используются различные модули в массиве, Программирование всех модулей в массиве лям в массиве адреса устройство гото- 25 - необходимый алгоритм происходит во к дальнейшему функционированию. прохождением одного микрокода через

систолический массив. Этот режим инициируется установлением на входе 2U устройства (фиг. 3 ) единичного сигго модуля в массиве, который во вревремя инкремента счетчика 30, и выходная информация с выходов регистра 29 и счетчика 30 поступают на соседний в строке модуль, и процесс адресации продолжается аналогичным образом. После присвоения всем модуРабота модуля состоит из трех основных режимов: режима программирования; режима транзитной передачи информации без обработки; режима обработки операндов, адресованных данному модулю.

Все три режима могут выполняться в модуле одновременно, что позволяет достичь параллельной работы отдельных блоков модуля и повысить производительность как модуля, так и всего систолического процессора.

Синхронизация работы модуля происходит по импульсам, которые формируются на первом и втором вьжодах генератора 12 и представляют собой две противофазные импульсные последовательности. Такт работы модуля состоит из первого и второго тактовых импульсов, вьщаваемых соответственно с первого и второго выхода генератора 12 (фиг. 13). По первому импульсу такта происходит считывание информации из входных очередей и ее запись в регистры 85 и 86 блока 6 для дальнейшего анализа направления и передачи информации. По второму импульсу такта осуществляется выбор направле ния передачи поступившей информации и ее выдача в другие модули массива, а также в случае адресации операндов данному модулю запуск блоков 7 и 8. Синхронизация работы блока 7 и умножите35

40

30 нала, организзпощего работу демультип- лексора 11 по второму выходу, и подачей единичного импульса на вход 23 модуля, который устанавливает триггер 13 в единичное состояние, разрешая работу генератора 12. Микрокод алгоритма и единичньй импульс программирования подаются на входы 18 и 19 модуля соответственно и, проходя через демультиплексор 11, поступают на соответствующие входы блока 2. По фронту единичного импульса программирования с помощью одновибратора 38 регистр 35 алгоритма устанавливается в нулевое состояние (фиг. 5). Появив g шийся нулевой сигнал на выходе элемента ИПИ 37 открьшает элемент И 36 и по импульсу со второго выхода генератора 12 происходит считьшание информации об алгоритме блока 34 в регистр 35 блока 2. После записи информации в регистр 35 алгоритма на выходе элемента ИПИ 37 появляется единичный сигнал, который закрывает элемент И36, запрещая прохождение импульсов с геР-с нератора 12 и единичного сигнала программирования на синхровход блока 34. Затем снимается единичньш сигнал программирования и микрокод алгоритма с входов 19 и 18 устройства соответст50

ка 3 происходит по импульсу информа

нала, организзпощего работу демультип- лексора 11 по второму выходу, и подачей единичного импульса на вход 23 модуля, который устанавливает триггер 13 в единичное состояние, разрешая работу генератора 12. Микрокод алгоритма и единичньй импульс программирования подаются на входы 18 и 19 модуля соответственно и, проходя через демультиплексор 11, поступают на соответствующие входы блока 2. По фронту единичного импульса программирования с помощью одновибратора 38 регистр 35 алгоритма устанавливается в нулевое состояние (фиг. 5). Появившийся нулевой сигнал на выходе элемента ИПИ 37 открьшает элемент И 36 и по импульсу со второго выхода генератора 12 происходит считьшание информации об алгоритме блока 34 в регистр 35 блока 2. После записи информации в регистр 35 алгоритма на выходе элемента ИПИ 37 появляется единичный сигнал, который закрывает элемент И36, запрещая прохождение импульсов с генератора 12 и единичного сигнала программирования на синхровход блока 34. Затем снимается единичньш сигнал программирования и микрокод алгоритма с входов 19 и 18 устройства соответст

13

1 к следуювенно, подготавливая модуль этапу программирования.

Программирование модуля может происходить как до решения задачи, так и в-процессе выполнение алгоритма, В первом случае выполняется алгоритм, который не требует перепрограммирования систолического массива в ходе, решения задачи, например матричное ум- ножение с динамическими промежуточными результатами, которые так же как и данные продвигаются в массиве и могут выводиться из него через граничные модули. Программирование в коде решения задачи может понадобиться, например, при выводе из систолического процесса конечного результата мат- рично-векторного умножения с неподвижными накапливаюыщмися во время решения промежуточными скалярньгми результатами.

В этом случае системньй контроллер, анализируя состояния счетчика 10, которьш хранит число выполненных операций данным модулем, на определенном этапе выполнения алгоритма произведет перепрограммирование модулей в массиве 5 что может происходить

с обработкой .операндов в накапливаю- ЗО ления передачи, восемь значений котощем умножителе В и транзитной передачей операндов через модули.

Таким образом, программирование модуля позволяет настраивать систолический процессор на выполнение различных алгоритмов преимущественно цифровой обработки сигналов, что объясняется возможностью работы систолических процессоров в реальном масштабе времени за счет высокой параллельности вычислений и высокой регулярности связей между модулями с возможностью динамической адаптации алгоритма обработки и маршрутов -передачи данных.

Ре}ким транзитной передачи информации без обработки. Подача данных в массив модулей может происходить, например, из граничных элементов памяти массива, храняш;их операнды, весовые коэффициенты и другую необхо..ци- мую информаци о, по командам системного контроллера или управляющей ЭВМ, которые производят выбор необходимых данных и ее адресацию в соответствии с выполняюш,имся алгоритмом. Перед началом подачи данных в систолический массив на вход 21 модуля подается единичный импульс, обнуляющий все ди™

2

намические элементы памяти модуля кроме блоков 1 И 2.Информация с восьми соседних модулей может поступать одновременно по входам 22, 1-22.8 устройств (фиг, 3). На третий вход блока 3 поступает сигнал блокировки с третьего выхода блока 6, равный единице тольк в случае необходимости выдачи операнда, , пришедшего на обработку данным модулем, или в случае необходимости выдачи результата вычисления из данного модуля в массив, что ведет к временному запрещению продвижения очередей Первым пришел, первым обслужен в блоках 40,1-40.8 блока 3 до завершения выдачи информации из регистров 85 и 86 (фиг, 6 и 10). На червертьй вход блока 3 поступавот первые тактовые импульсы с первого выхода генератора 12, по которым происходит . выдача информации из.последовательно опрашиваемых блоков 40.1- 40,8 на анализ в блоке 6,

Постунающая информация от восьми соседних модулей на вторые информационные входы блока 3 состоит из трех основных частей (фиг. 6): кода коэффициента загрузки данного направ5

0

1рых образуют первый информационный выход блока 3 и поступают на анализ в блок 4 (фиг, 6 и 8); значения операнда с адресом его передачи и ши- пульса синхронизации записи этой информации в соответствующую память магазинного типа первый пришел, первый обслужен блоков 40.1-40,8 блока 3 ( фиг , 6 ), Эта информация поступает соответственно на второй инфор- мационньй и третизй вход блоков 40.1- 40.8, первые входы обнуления которых соединены с первым входом блока 3, четвертый вход является входом считывания из очереди (, или продвижения очереди ), а пятые входы блоков 40.1- 40.8 являются входами синхронизации. С первьЕх; информационных выходов блоков 40.1-40.8 будет последовательно считываться занесенная информация, с вторых информационных выходов будет постоянно подаваться на восемь соседних модулей код загрузки соответствующих для них направлений, а третьи g выходы блоков свидетельствуют о наличии в них информации (фиг, 6 и 7).

При поступлении информации хотя бы от Одного соседнего модуля и загрузке ее в определенньй блок 40.1-40.8

5

0

на третьем выходе готовности этого блока устанавливается единичньй сигнал, который через элемент ИЛИ-НЕ 48 и одновибратор 51 перебросит триггер 42 в единичное состояние, обну- ленный подачей импульса на вход 2 Г модуля через элемент ИЛИ-НЕ 48 и одновибратор 52 (фиг. 3 и 6 ). Единичный сигнал с прямого выхода тригге- ра 42, поступая на первый вход элемента И 45, открывает его (при отсутствии сигнала блокировки на третьем входе блока 3 )для прохождения тактовых импульсов -с первого выхода гене- ратора 12, и по первому его импульсу содержимое счетчика 41 увеличивается на единицу, тем самым устанавливается адрес очередного считывания из co ответствующего блока 40.1-40.8 . (фиг. 6). Код этого адреса с выхода счетчика 41 поступает на управляющий вход мультиплексора 43 и определяет его работу по входу обслуживаемой очереди блоков 40.1-40.8. Одновремен но с этим дешифратор 44 преобразует этот адрес в унитарньй код, которьш поступает на соответствующие входы блоков 40.1-40.8, разрешая считывание из определенной очереди,а через группу элементов И 46.1-46.8 и элемент ИЛИ 47, поступая на синхррвход мультиплексора 43, разрешает прохождение через него информации только при ненулевом сигнале готовности с третьего выхода соответствующего блока 40.1-40.8 группы. Работа счетчика 41 организована по модулю 8 и задает последовательный опрос очередей блоков 40.1-40.8. После заверше- ния опроса последнего блока 40.8 одновибратор 50, соединенньш с восьмым выходом дешифратора 44, вырабатывает импульс, который, проходя через элемент ИЛИ 49, обнуляет счетчик 41, переводя его на опрос очереди первого блока 40.1.

Тактовые импульсы с первого выхода генератора 12 в случае отсутствия блокировки блока 3 по третьему его выходу, задержанные на элементе 53 задержки на время переходных процессов счетчика 42 и дешифратора 44, поступают на пятые входы блоков 40.I 40.8 и синхронизируют работу блока З Счетчики 55 каждого блока 40.1-40.8 (фиг. 7 ) индицируют на своем выходе коэффициенты загрхузки соответствующих направлений, которые по пятому

информационному выходу блока 3, по десятому информапион)юму входу блока 6 и по определенным вторым информационным выходам 28.1-28.8 устройства подаются на соответствующие информационные входы соседних модулей, организация которых там происходит аналогично рассмотренному.

В случае обслуживания всех запросов в очередях блоков 40.1-40.8 появившийся единичный сигнал на выходе элемента РШИ 48 через одновибратор 52 обнуляет триггер 42, запрещая тем самым опрос блоков 40.1-40.8 до следующего прихода операндов в модуль. По приходу операндов происходит процесс активизации блока 3 аналогично рассмотренному, и по импульсу с первого выхода генератора 12 происходит считывание информации из блока 3 и запись ее в регистры 85 и 86 блока 6 (фиг. 6, 10 и 13).

Работа мультиплексора 90 адресов и мультиплексора 91 операндов в этом случае происходит по первым входам, что обусловлено нулевыми сигналами на управляющих входах и единичным сигналом на их синхровходах. Нулевой код на управляющих входах мультиплексора 90 задается счетчиком 89, находящимся в нулевом состоянии, и закры- тьми элементами И 96 и 97, а нулевой сигнал на управляющем входе мультиплексора 91 определяется нулевым сигналом с выхода элемента ИЛИ 107, который обусловлен нулевым состоянием счетчика 89, и, следовательно, нулевыми сигналами на втором, третьем и четвертом выходах дешифратора 92. Единичный сигнал на синхровходах мультиплексоров 90 и 91 определяется единичным сигналом, проходящим через элемент ИЛИ 109 блока 6 с выхода элемента ИЛИ 47 блока 3, которьй является шестым выходом блока 3 и тринадцатым входом блока 6 (фиг. 3, 6 и 10).

Сдвиг очереди в блоках 40.1-40.8 блока 3 и запись информации сдвига с выхода определенного блока 40.1- 40.8 через мультиплексоры 43, 90 и 91 в регистры адреса 85 и операнда 86 происходят по одному тактовому имг пульсу с первого выхода генератора 12 который задерживается на элементах 53 и 115 задержки на время обусловленное переходными процессами счетчика 41, дешифратора 44, мультиплексоров 43, 90 и 91. Операнд записывается в регистр 85 операнда, а адрес операнда - в регистр 86 адреса (фиг. 6, 10 и 13).

В каждый момент времени информация О коэффициентах загрузки всех направлений передачи проходит с пятых информационных входов 22,1-22,В через блок 3 на информационный вход блока 4, где в. процессе сравнения на группе компараторов 66.1-66;16 чисел происходит сравнение коэффициентов загрузки трех направлений для всех восьми возможных секторов передачи данных и с помощью двух групп элементов ИЛИ 67.1-67.16,и 68.1-68,16 происходит выработка сигналов идентификации наименее загруженного направления для каждого сектора возможной передачи и выдача их (по шесть линий на каждое направление ) на третий ин- формационньй вход блока 5, на второй информационный вхоц которого подает- ся адрес операнда с выхода регист-- ра 85 блока 6 по первому информацион- ному выходу блока 6„ На первом информационном входе блока 5 присутствует собственный адрес данного модуля., подающийся с выхода регистра 29 и счетчика 30 по второму информацион- ному выходу блока 1 (фиг. 3, 4, 8, 9 .и 10).

По второму тактовому импульсу с второго выхода генератора 12 инициируется процесс сравнения, модифН1сации и Определения направления передачи данных, находящихся в регистрах 86 и 85 операнда блока 6, Тактовый m-i- пульс с второго выхода генератора 12 поступает по четвертому входу БВН на синхровходы первого 70 и второго 71 вычитателей, разрешая их работу, и на вход считывания однословного блока памяти ПЗУ 69, которое постоянно хранит (без разрушения информации ) код единицы. Однословное постоянное запоминающее устройство 69 может быть организовано путем фш сснрованной подачи постоянного адреса, по которому хранится код единицы, на простое ПЗУ Вычитатели 70 и 71 могут быть организованы на основе традиционных сукгма- торов-вычитателей или АЛУ, на управляющие входы которого может быть подана постоянная комбинация, соответ- ствующая операции вычитания ь Возможные организующие сигналы для ПЗУ 69 и вычитателей 70 и 71 на фиг. 9 не показаны. Вычитатели 70 и 71 вычисляют

абсолютную разность (выходной разряд заема не учитывается) между кодами строк и столбцов собственного и прошедшего адреса компараторов 72 и 73 чисел, на вторые входы которых подается код единицы с ,ыхода ПЗУ 69, а также элементов И 80-82, на выходе элемента ИЛИ 83 формируется единичный сигнал, говорящий о том, что пришедший операнд предназначен одному из восьми соседних модулей. Этот сигнал служит для запрещения модификации передачи информации с учетом коэффициента загрузки направлений, если адресуемый модуль - соседний.

Одновременно с этим третий 74 и четвертью 75 компараторы чисел вырабатывают сигналы сравнений собственного и поступившего адреса по строкам и столбцам соответственно. Эти сигнал), поступая соответствующим образом на элементы И 76.1-76.8 и 77.1-77.8, организуют направления передачи соответственно без модификации и с модификацией, учитывающей загрузку направления. Элемент И 76.9 служит для выдачи единичного импульса при совпадении адресов в случае, если пришедший операнд предназначен данному модулю. Информация модификации с учетом загрузки направлений поступает из блока 4 в блок 5 на первые I. -

пары входов соответствующих элементов И блоков 78.1-78,85 задавая тем самым модификацию передачи информации в зависимости от загрузки направ- лений. Импульс с второго выхода генератора 12, задержанньш на элементе 84 задержки на время возможного формирования на выходе ИЛИ 83 единичного сигнала запрещения модификации, поступает на третьи входы элементов И 76Л-76.8 и 77.1-77.8, и, в зависимости от того, предназначен ли текущий адрес соседнему модулю или нет, выдача сигнала направления происходит на один из элементов группы ИЛИ 79.1-79.8 либо непосредственно с выхода соответствующего элемента И 76.1-76.8, минуя группу блоков элементов И 78.1-78.8 (если операнд адресован соседнему модулю ), либо с выхода соответствующего элемента И 77,1-77.8 через группу блоков элементов И 78.1-78.8 (если операнд адресован не соседнему и не данному модулю),

19

Если анализ направления в компараторах 74 и 75 чисел соответствует, например, направлению Восток (В ) и если операнд адресован не соседнему модулю, то в зависимости от загрузки направлений В, С-В и Ю-В может произойти модификация направления выдачи операнда и замена направления В на направление IO-B или С-В дпя данного сектора направлений. Аналогичная модификация в зависимости от загрузки направления может происходить во всех восьми секторах передачи информации. Если операнд адресован соседнему мо- дулю, то он передается на него непосредственно без модификации (фиг.1 2, 9 и 10).

Таким обрйзом, по импульсу с второго выхода генератора 12 блок 5 формирует сигнал направления выдачи операнда (фиг. 1 З) и выдает его на второй информационньй вход блока 6, если операнд предназначен для транзитной передачи на другой модуль в мае- сиве без обработки на данном модуле, и на 11-й вход блока 6, если операнд предназначен для данного модуля с дальнейшей передачей или без передачи на другие модули в систолическом про- цессе (фиг. 3). В первом случае информация направления, сформированная на выходе блока 5, поступает по второму информационному входу блока 6 на входы открытия блоков элементов И 93. 93.8 и производит выдачу информации из регистров 85 и 86 на один из восьми четвертых информационных выходов модулей 28.1-28.8, которые.являются соответствующими информационными вхо- дами для восьми соседних модулей.

Таким образоь, для данного модуля транзитная передача информации без обработки происходит за время одного такта, в котором формируются два импульса на соответствующих выходах генератора 12 (фиг. 13).

Режим обработки операндов, адресованных данному модулю. Если операнд, занесенньй в регистр 86 из блока 3, имеет адрес данного модуля, то по второму импульсу того же такта на втором выходе блока 5 появляется еди- ничньй сигнал, которьй, поступая на одиннадцать вход блока 6, производит следующие действия. Поступая на от- крытьй нулевым состоянием регистра 87 первого операнда элемент И 101 ,единич- Hbrfi сиг нал синхронизирует запись пршпед

15

20 25зо 1- Q

45 0gg 2120

шего операнда с выхода регистра 86 в регистр 87 (фиг. 10 и 13. Это приводит к установлению нулевого сигнала, на выходе элемента ИПИ-НЕ 110, которьй запрещает запись в регистр 87, закрывая элемент И 101, и подготавливает к открытию элемент И 102, а следовательно, и к записи регистр 88 второго операнда. Поступая через элемент ИЛИ 104 на суммируюп1ий вход счетчика 89, единичньй сигнал увеличивает его содержимое на единицу и устанавливает в единичное состояние , что приводит к появлению на втором выходе дешифратора 92 единичного сигнала. Единичньш сигнал на выходе элемента И 98 будет сформирован лишь в том случае, если на его второй вход поступает единичньй сигнал (говорящий о дальнейшей передаче первого операнда в массиве модулей )с поля 35.2 регистра 35 алгоритма блока 2 (фиг. 5 через первый информационньй выход блока 2 и третий информационньй вход блока 6 (фиг. 3, 5 и Ю). Единичкьй сигнал с второго выхода блока 5, за- держанньй на элементе П6 задержки на время формирования очередного сигнала на выходе дешифратора 92, проходит через открытый элемент И 98 (в случае необходимости дальнейшей передачи в массив первого операнда ) и через элементы ИЛИ 106 и 107 на элементы 117 и 118 задержки соответственно.

I

На элементе 117 задержки импульс

задерживается до прихода первого импульса следующего такта на синхро- входы регистров 85 и 86. На элементе 118 задержки импульс задерживается до момента времени формирования генератором 12 на своем первом выходе первого импульса следующего такта работы модуля (фиг. 13 ). После чего этот импульс с выхода элемента 118 задержки через элементы И 96 и 97 задает работу мультиплексора 90 адресов по второму входу, куда подается информация адреса передачи первого операнда, хранимая для данного алгоритма в поле 35.1 регистра 35 блока 2 (фиг. 5); переводит мультиплексор 91 операндов также на работу по второму входу;через элемент ИЛИ 109 открывает эти мультиплексоры; и, поступая на второй инверсный вход элемента И 45 по третьему выходу блока 6 и третьему входу блока 3, блокирует

21

продвижение очередей н считывание информации из блоков 40.1-А0.8,

Первый импульс следующего такта с генератора 12 синхронизирует новую запись адре са только в регистр 85 ад- деса, в то время как единичный сигнал с элемента задержки блокирует на элементе И 95 синхронизацию новой залиси в регистр 86 операндов, т.е. его содержимое не изменяется. Таким образом, происходит только за- мев(ение адресной его части в регистре 85 из регистра 35 блока 2 по второму входу мультиплексора 90.

После записи нового адреса в регистр 85 по второму импульсу текущего такта с второго выхода генерато13

(фиг.З, 10 и 11). По этому нулевому сигналу открывается шинный формирователь 94 с тремя состояниями и одно- вибратор 113 формирует импульс, который, проходя с седьмого выхода блока 6 на третий вход блока 7, синхронизирует запись кода операции с выхода поля 35.7 регистра 35 блока 2 в счетчик 121 блока 7 (фиг.З, 5 и I); поступая на четвертый вход блока 8, синхронизирует запись первого и второго операндов из регистров 87 и 88 блока 6 в регистры 131 и 132 блока 8 соответственно, подготавливая блок 8 к работе, которая начнется в следующем такте под управлением блока 7j и, задерживаясь на элементе 119 задержки на время, необходимое для зара 12 происходит анализ и модификация

направления дальнейшей выдачи, а так-, несения информации в счетчик 121 бложе выдача этой инфорамции через груп- ка 7 ив регистры 131 и 132, проходит

пу блоков элементов И 93.1-93,8 на один из соседних модулей аналогично рассмотренному в режиме транзитной

через элемент ИЛИ 108 и обнуляет регистры 87 и 88 блока 6, подготавливая их к следующему приему информапередачи без обработки информации на 25 Ции (фиг.10). данном модуле (фиг.13).Второй единичный сигнал на втором

В данном модуле работа накапливаю- выходе блока 5, проходя через элемент ИЛИ 104, увеличивает содержимое

счетчика 89 блока 6 на единицу, уста-

щег.о умножителя и его микропрограммного блока управления инициируется только по приходу обоих операндов и записи их в регистры 87 и 88 первого и второго операндов блока 6 (фиг.10- 13). Возможен как последователысьй приход -пары операндов на обработку данным модулем, так и нерегулярный их приход, т.е. между приходом первого и второго операндов может произойти . несколько транзитных передач через данньш модуль без обработки приходящей информации на нем аналогично рассмотренному (фиг.13).

При приходе второго операнда на обработку данным модулем по второму импульсу такта на втором выходе блока 5 появляется второй единичньй сигнал.

Единичный сигнал поступает на открытый элемент И 102 и синхронизирует запись второго операнда из регистра 86 в регистр 88 блока 6, что приводит к появлению единичного сигнала на выходе элемента ИЛИ 110, который в случае отсутствия работы блока 7 (единичньй сигнал с инверсного выхода триггера 122 по третьему выходу блока 7 и по двенадцатому входу блока 6 поступает на второй вход элемента И-НЕ юз) устанавливает на выходе элемента И-НЕ I03 нулевой сигнал

35

40

45

50

55

навливая на его выходе код числа 2. На третьем выходе дешифратора 92 появляется единичньй сигнал, которьй в случае необходимости передачи второго операнда на дальнейшую обработку в массив (единичньй сигнал поля 35.4 регистры 35 блока 2 поступает через второй информационньй выход блока 2 и четвертьй информационный вход блока 6 на второй вход элемента И 99)инициирует появление единич-. ного сигнала на выходах элементов ШШ 106 и 107. Эти сигналы организуют модификацию адреса и вьщачу второго операнда на дальнейшую обработку в массив аналогично первому операнду, как это было рассмотрено, лишь с той разницей, что новый адрес в регистр 85 блока 6 для второго операнда записывается с поля 35.3 регистра 35 блока 2 через третий вход мультиплексора 90, работу которого задает счетчик 89 и дешифратор 92 блока 6 (фиг.З, 5, 10 и 13).

После занесения кода операции в счетчик 121 блока 7 триггер 122 устанавливается в единичное состояние, которое разрешает прохождение тактовых импульсов через элемент И 123 с чет- вевтого входа блока 7 на вход синхро- 5 34342122

(фиг.З, 10 и 11). По этому нулевому сигналу открывается шинный формирователь 94 с тремя состояниями и одно- вибратор 113 формирует импульс, который, проходя с седьмого выхода блока 6 на третий вход блока 7, синхронизирует запись кода операции с выхода поля 35.7 регистра 35 блока 2 в счетчик 121 блока 7 (фиг.З, 5 и I); поступая на четвертый вход блока 8, синхронизирует запись первого и второго операндов из регистров 87 и 88 блока 6 в регистры 131 и 132 блока 8 соответственно, подготавливая блок 8 к работе, которая начнется в следующем такте под управлением блока 7j и, задерживаясь на элементе 119 задержки на время, необходимое для за10

15

через элемент ИЛИ 108 и обнуляет регистры 87 и 88 блока 6, подготавливая их к следующему приему информасчетчика 89 блока 6 на единицу, уста-

5

0

5

0

5

навливая на его выходе код числа 2. На третьем выходе дешифратора 92 появляется единичньй сигнал, которьй в случае необходимости передачи второго операнда на дальнейшую обработку в массив (единичньй сигнал поля 35.4 регистры 35 блока 2 поступает через второй информационньй выход блока 2 и четвертьй информационный вход блока 6 на второй вход элемента И 99)инициирует появление единич-. ного сигнала на выходах элементов ШШ 106 и 107. Эти сигналы организуют модификацию адреса и вьщачу второго операнда на дальнейшую обработку в массив аналогично первому операнду, как это было рассмотрено, лишь с той разницей, что новый адрес в регистр 85 блока 6 для второго операнда записывается с поля 35.3 регистра 35 блока 2 через третий вход мультиплексора 90, работу которого задает счетчик 89 и дешифратор 92 блока 6 (фиг.З, 5, 10 и 13).

После занесения кода операции в счетчик 121 блока 7 триггер 122 устанавливается в единичное состояние, которое разрешает прохождение тактовых импульсов через элемент И 123 с чет- вевтого входа блока 7 на вход синхронизации считывания управляющей памяти 120 (фиг. П). Эти же- импульсы, задержанные на элементе 126 на время, необходимое для выполнения одной микрокоманды в блок 8, увеличивают адрес счетчика 121 на единицу - тем самым задается микропрограммное управление с естественной адресацией операции, код которой определяется начальным адресом, занесенным на установочный вход счетчика 121 блока 7, Так как набор выполняемых операций блока 8 невелик и, как правило, жестко задан

10

23134342124

из регистра 88 блока 6, так и выдача, определенной части результата с вы- . ходных каскадов 135 с тремя состояниями. Развязку двунаправленной передачи данных осуществляют вьшодные каскады 135 блока 8 и шинные формиро- . ватели 94 с тремя состояниями блока 6 (фиг. 10 и 12). В качестве блока 8 может быть использован, например, серийно выпускаемьш матричньп умножитель в виде СБИС.

Последняя микрокоманда, которая индицируется единичным сигналом на в соответствий со спецификой алгорит- 15 втором выходе блока 7 (признак-метка мов цифровой обработки сигналов, мик- конца микропрограммыJ, содержит ин- 1ропрограммы блока 7 могут содержать фиксированные короткие наборы микрокоманд, которые выполняются в процес-. се алгоритмов без ветвлений, что су- 20 щественно упрощает блок 7 для бло-;; ка 8. В принципе, без существенного изменения структуры предлагаемого ПСПЭ возможно использование вместо умножителя 8 более мощного АЛУ или микропроцессора с дополнительной внутренней оперативной памятью, в которую перед решением задачи могут загружаться многократно используемые данные, например весовые коэффициенты ядра свертки и др. Это позволит повысить универсальность модуля за счет увеличения набора выполняемых операций, но может привести к снижению производительности, что неприем- шения выполнения операции в блок 8 лемо для многих задач цифровой обра- сигнал окончания микропрограммы по- ботки сигналов, требующих решения в ступает по второму выходу блока 7 и реальном масштабе времени.девятому входу блока 6 на элемент 114

Операционные микрокоманды, считы- задеряски блока 6 и задерживается в ваясь на управляющей памяти 120, по- Q нем на время переходных процессов ступают по первому информационному блока 5 с целью одинакового времени выходу блока 7 и второму информацион- формирования сигналов, поступающих ному входу блока 8 (фиг. 3, 11 и 12) на суммирующий вход счетчика 89 че- на регистр 133 управления блока 8 и рез элемент ИЛИ 104 блока 6 Этот сиг- определяют процесс обработки двух чи- нал с выхода элемента 114 задержки , занесенных, как было показано через элемент ИЛИ 104 поступает на

формацию о выводе результата блока 8 в регистр 9 (фиг. 3, П и 12). Эта запись, в случае ее необходимости, синхронизируется в регистр 9 сигналом окончания микропрограммы с второго выхода блока 7. По этому же сигналу, задержанному на элементе 128 задержки на время записи в регистр 9, 25 происходит обнуление счетчика 121 и триггера 122, тем самым блок 7 подготавливается к следующему приему кода операции. До завершения операции в блоке 8 с целью обеспечения правильного функционирования счетчика 89 блока 6 модуля блок 7 не может принимать операнды на обработку, а производит лишь их транзитную передачу на другие модули в массиве. После завер30

сел,

ранее, в регистры 131 и 132 операндов блока 8. Сигналы, поступающие с регистра 133 на управляющие входы матрицы 129 умножения, сумматора 130, выходного регистра 134 и выходных каскадов 135 с тремя состояниями, организуют умножение и накопление чисуммирующий. вход счетчика 89), увеличивая его содержимое на единицус На выходе счетч1жа 89 индицируется код числа 3, соответственно на четвертом выходе дешифратора 92 появляется еди- ничньй сигнал.

В случае необходимости передачи результата на другой модуль в массиВ случае необходимости передачи результата на другой модуль в массисел, а также выдачу результата в регистр 9 (фиг. 3, 11 и 12), когда это . ве (систолическая обработка с продви- I требует алгоритм. Работа блока 8 ор- жением результата )в поле 35о6 реги- ганизована так, что по третьему ин- стра 35 блока 2 хранится единица (в формационному входу может происходить противном случае - ноль ), а в по- как загрузка операнда в регистр 132 ле 35.5 - адрес модуля, которому неПоследняя микрокоманда, которая индицируется единичным сигналом на 5 втором выходе блока 7 (признак-метка конца микропрограммыJ, содержит ин- 0 шения выполнения операции в блок 8 сигнал окончания микропрограммы по- ступает по второму выходу блока 7 и девятому входу блока 6 на элемент 114

формацию о выводе результата блока 8 в регистр 9 (фиг. 3, П и 12). Эта запись, в случае ее необходимости, синхронизируется в регистр 9 сигналом окончания микропрограммы с второго выхода блока 7. По этому же сигналу, задержанному на элементе 128 задержки на время записи в регистр 9, 5 происходит обнуление счетчика 121 и триггера 122, тем самым блок 7 подготавливается к следующему приему кода операции. До завершения операции в блоке 8 с целью обеспечения правильного функционирования счетчика 89 блока 6 модуля блок 7 не может принимать операнды на обработку, а производит лишь их транзитную передачу на другие модули в массиве. После завер0

суммирующий. вход счетчика 89), увеличивая его содержимое на единицус На выходе счетч1жа 89 индицируется код числа 3, соответственно на четвертом выходе дешифратора 92 появляется еди- ничньй сигнал.

В случае необходимости передачи результата на другой модуль в массиве (систолическая обработка с продви- жением результата )в поле 35о6 реги- стра 35 блока 2 хранится единица (в противном случае - ноль ), а в по- ле 35.5 - адрес модуля, которому необходимо передать результат. Анало- г ичиая информация хранится для первого и второго операндов обработки на данном модуле в полях 35.1, 35.2 и 35,3, 35,4 соответственно (фиг. 5). Едипичньп сигнал с поля. 35.6 регистра 35 блока 2, поступая на второй вход элемента И 100, открывает его по сигналу окончания микропрограммы, и на выходе элемента ИЛИ I О/ появляется единичньй сигнал.

Единичньш сигнал с выхода элемента ИЛИ 107, задержанньй до появления первого импульса следующего такта на первом выходе генератора 12, выполняет следующие действия: разрешает прохождение кода числа 3 с выхода счетчика 89 через элементы И 96 и 97 на управляющий вход мультиплексора 90 адресов, определяя его работу по четвертому входу; поступая на управляющий вход мультиплексора 91 операндов, задает его работу по второму входу; поступая через элемент ИЛИ 10.9, разрешает функционирование мультиплексоров 90 и 92; поступая на инверсный вход элемента И 45 блока 3 через третий выход блока 6 и третий вход блока 3, блокирует на один такт сдвиг очереди блоков 40.1-40.8 и выдачу информации из блока 3 в блок 6.

Информация об адресе передачи результата поступает с поля 35.5 регистра 35 БПА 2 через четвертый вход мультиплексора 90 на информационньй вход регистра 85, а результат с выхода ре1гистра 9 через второй вход мультиплексора 9 -на информационньй вход регистра 86. Синхронизация этой записи происходит по первому импульсу следузощего такта на первом выходе генератора 12. Информация результата в этом случае записьшается в оба регистра 85 и 86, так как на инверсном входе элемента И 95 присутствует разрешающий нулевой сигнал с выхода элемента ИЛИ 106 блока 6.

Дальней лий анализ с модификацией адреса и выдача результата в систолический массив происходи аналогично рассмотренному. Завершение генерации генератора 12 происходит при одновременном выполнении следующих условий: все очереди блоков 40. блока 3 пусты; выполнение микропрограммы блока 7 завершено;.регистр 87 первого операнда блока 6 пуст. Сигналы этих условий поступают соответственно с

инверсного выхода элймента ИЛИ 111 блока 6 на входы элемента И 16 блока си1гхронизации (фиг. 3J, При выполнении этих условий по появившемуся единичному сигналу на выходе элемента И 16 блока синхронизации одновиб- ратор 17 сформирует импульс, который через элемент ИЛИ 15 обнулит три1-

гер 11 запуска, запрещая тем самым работу генератора 12. Работа модуля может быть также остановлена по внешнему сигналу прерывания на седьмом входе 24 модуля. После завершения генерации генератор 12 модуля прекращает данньй цикл своей работы. При подаче на шестой вход 23 модуля .единичного сигнала или по приходу информации с соседних модудей на пятые информационные входы 22. 1-22.8 (в общем случае окончание работы различных модулей может происходить неодновременно ) одновибратор 51 блока 3 сформирует импульс, который через элемент ИЛИ 14 установит триггер 11 запуска в единичное состояние, инициирует тем самьм работу генератора 12 и следующий цикл функционирования модуля .

Далее работа модуля происходит аналогично рассмотренному.

Формула изобретения

Процессорньй модуль, содержащий блок микропрограммного управления, первьй операционньй блок, регистр результата, бло1 стековой памяти и блок памяти результата, причем информационньй выход первого операционного блока соединен с информационным входом регистра результата, отличающийся тем, что, с целью по- . вьшгения производительности, он содержит блок формирования адреса, блок памяти программ, демультиплексор,второй операционньй блок, блок сравнения, счетчик этапов вычислений и блок синхронизации, при этом первый

и второй информационные входы, вход разрешения выборки, с первого по чет- вертьй информационные выходы демуль- типлексора соединены соответственно с первым информационным входом, входом синхронизации и входом задания режима модуля, информационным входом и входом синхронизации блока формирования адреса, адресным входом и первым входом разрешения обращения блока памяти программ, первый и второй информационные выходы и выход признака сопровождения блока формирования адреса подключены соответственно к первому информационному выходу модуля, первому информационному входу операционного блока и выходу признака сопровождения информации модуля, вход сброса, информационный вход, вход признака блокировки, вход синхронизации и пер Ьый информационньш выход блока стековой памяти соединены соответственно с входом начальной установки и вторым информационным входом модуля, выходом признака блокировки продвижения блока памяти результатов, первым выходом блока синхронизации и входом блока сравнения, второй и третий информационные входы вход синхронизации, информационный выход и выход признака результата второго операционного блока подключены соответственно к первому информационному выходу блока памяти резуль- татов, выходу блока сравнения, второму выходу блока синхронизации, первому информационному входу и входу разрешения приема операнда блока памяти результатов, второй вход разрешения обращения, выход адреса первого операнда, выход адреса второго операнда выход адреса результата и выход поля операции блока памяти программ соединены соответственно с вторым выходом блока синхронизадии, вторым, третьим и четвертым информационными входами блока памяти результатов и входом кода операции блока микропрограммного управления, вход сброса, тактовый вход и выход счетчика этапов вычислений подключены соответственно к вхои

ду начал-ьной установки модуля, выходу признака окончания операции блока микропрограммного управления и второ- му информационному выходу модуля, вход сброса, пятьш, шестой и седьмой информационные входы, вход синхронизации, вход признака окончания операции, вход признака выполнения опера-

ции, вход признака продвижения очереди, второй, третий и четвертьп информационные выходы, выход признака первого операнда и выход признака начала операции блока памяти результатов соединены соответственно с входом начальной установки модуля, вторым информационным выходом блока стековой памяти, выходом регистра результата, третьим информационным выходом блока стековой памяти, первым выходом блока синхронизации, выходом признака окончания операции и выходом признака выполнения операции блока микропрограммного управления, выходом признака продвижения очереди стековой памяти, третьим информационным выходом модуля, первым и вторым информационными входами первого операционного блока, первым входом задания режима блока синхронизации и входами запуска первого операционного блока и блока микропрограммного управления, вход сброса, вход синхронизации и операционный выход которого подключены соответственно к входу начальной установки модуля, второму выходу 6JJO- ка синхронизации и входу кода операции первого операционного блока, вход сброса, информационный вход и вход синхронизации регистра результата соединены соответственно с входом начальной установки модуля, четвертым информационным выходом блока памяти результатов и выходом признака окончания операции блока микропрограммного управления, первый и второй входы запуска блока синхронизации подключе ны соответственно к выходу признака состояния очереди блока стековой памяти и входу запуска модуля,вход останова блока, синхронизации соединен с входом останова модуля, а второй и третий входы задания режима блока синхронизации соединены соответственно с выходом признака отсутствия очереди блока стековой памяти и выходом признака вьтолнения операции блока микропрограммного управления.

Х. I УУ

pjLy y-l xX-JuX -j -Фиг./

XIX

jL XX-A-Xx

о

XMNriV

xX-JuX -j -«еXj-jLXx

хтхтх

Фиг. 5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство формирования маршрута сообщения в однородной вычислительной системе | 1985 |

|

SU1287172A1 |

| МОДУЛЬ МУЛЬТИМИКРОПРОГРАММНОЙ СИСТЕМЫ | 1997 |

|

RU2116665C1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1352483A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1997 |

|

RU2111528C1 |

| Устройство для обмена данными в распределенной вычислительной системе | 1988 |

|

SU1580382A1 |

| Устройство для программного управления | 1989 |

|

SU1656498A1 |

| Ячейка однородной вычислительной среды | 1986 |

|

SU1386987A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении высокопроизводительных систолических матричных процессоров с программируемой динамической адаптацией алгоритма обработки и маршрута передачи данных, например, при цифровой обработке сигналов и изображений. Целью изобретения является повышение пpoизвoдитeJJь- ности. С этой целью в модуль, содержащий блок 7 микропрограммного управления, операционньй блок 8, регистр 9 результата, блок 3 стековой памяти и блок 6 памяти результата, введены блок 1 формирования адреса, блок 2 памяти программ, демультиплексор II, второй операционньй блок 5, блок 4 Ф О) со 4: СО 4 Ю Й/г.5

СЗт

т:

81

тг

73

J

11

;

й

CS,W

ISS I

:4

м

Р

§FS

(pus. 10

Фиг11

(Pu2.i2

ti til ii S fiTf/(7 ti,

Фаг. 13

Редактор В.Данко

Составитель Г.Виталиев

Техред М. Дидык-Корректор С. Черни

Заказ 4825/30 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Патент США № 4314349, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

| СМАЗОЧНО-ОХЛАЖДАЮЩАЯ ЖИДКОСТЬ ДЛЯ МЕХАНИЧЕСКОЙ ОБРАБОТКИ МЕТАЛЛОВ РЕЗАНИЕМ | 1996 |

|

RU2129589C1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

Авторы

Даты

1987-10-07—Публикация

1985-09-30—Подача