Выполнения алгоритма Волдера, оно содержит первый и второй коммутаторы, причем первые информационные входы первого и второго коммутатор подключены к выходам первого и второго сумматоров соответственно, втрые информационные входы первого и второго коммутаторов подключены к выходам четвертого и третьего регистров сдвига соответственно, управляющие входы первого и второго коммутаторов подключены к выходам блока управления с восьмого по одинадцатый, третий управляющий вход блока управления является входом задания режима работы устройства.

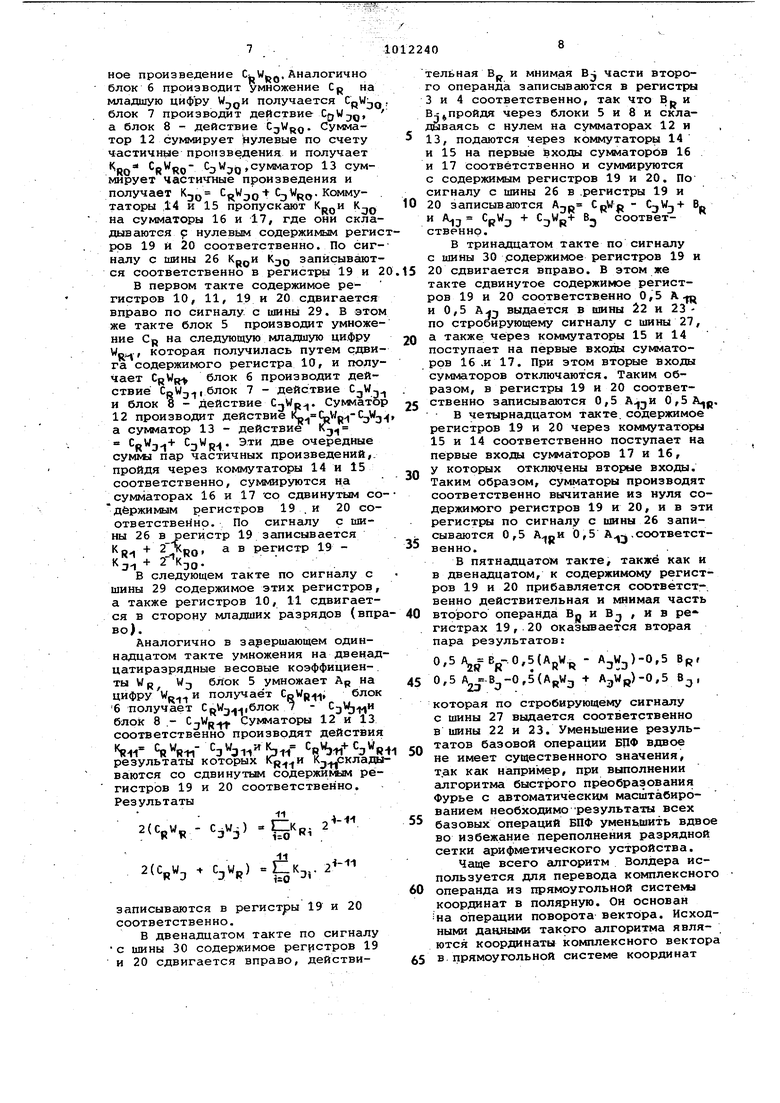

2. Устройство по п. 1, о т л ич ающеес я тем, что блок управления состоит из счетчика, шестнадцати элементов И и пяти элементов ИЛИ, причем счетный вход счетчика является тактовым входом блока управления, установочный вход счетчика является первым уп- . равляющим входом блока управления, выход первого разряда счетчика подключен к первым инверсным входам первого, второго, третьего элементов И и к прямьии входам четвертого и пятого элементов И, выход второго разряда счетчика подключен к вторым инверсным входам первого, второго и третьего элементов И, к первым инверсным входам шестого и седьмого элементов И, к первым прямым входам восьмого и девятого элементов И, выход третьего разряда счетчика подключен к третьим инверсным входам второго и третьего элементов И, к второму инверсному входу шестого элемента И, к первому инверсному входу восьмого элемента И, к первым прямым входам первого, седьмого, десятого, одиннадцатого и двенадцатого элементов выход четвертого разряда счетчика подключен к четвертым инверсным входам первого и второго элементов И, к третьему инверсному входу шестого элемента И, к первым прямым входам третьего и тринадцатого элементов И, к вторым прямым входам седьмого, восьмого, десятого и одиннадцатого элементов И выход пятого разряда счетчика подключен к четвертым инверсным входам первого и шетого элементов И, к пятому инверсному входу второго элемента И, к второму прямому входу третьего элемента И, к третьим прямым входам седьмого, восьмого, десятого и одиннадцатого элементов И и к первому прямому входу четырнадцатого элемента И, первый прямой вход пятнадцатого элемента И является вторым управляющим входом блока управления и подключен к инверсному входу шестнадцатого элемента И, пятый инверсный вход первого элемента И является третьим управляющим входом блока управления и подключен к четвертому инверсному входу третьего элемента И, к первому инверсному входу пятого и одиннадца.того элемента И, к вторым-инверсным входам седьмого и восьмого элемен. тов И, к вторым прямым входам девятого, двенадцатого, тринадцатого, четырнадцатого и пятнадцатого элементов И, а также к прямому входу шестнадцатого элемента И, выходы первого и второго элементов И подключены к входам первого элемента ИЛИ, выхода второго и третьего элементов И подключены к входам второго элемента ИЛИ, выходы седьмого, восьмого и девятого элементов И подключены к входам третьего элемента ИЛИ, выходы одиннадцатого и пятнадцатого элементов и подключены к входам четвертого элемента ИЛИ, выходы одиннадцатого и шестнадцатого элемен- тов И подключены к входам пятого элемента ИЛИ, выход шестого элемента И подключен к первому инверсному входу четвертого элемента И и к второму инверсному входу пятого элемента И, выход десятого элемента И подключен к второму инверсному входу четвертого элемента Ник третьему инверсному входу пятого элемента И, выход первого разряда счетчика выходы первого, второго элементов ИЛИ, четвертого, пятого элементов И, четвертого,.пятого и.третьего элементов ИЛИ, двенадцатого, тринадцатого и четырнадцатого элементов И являются соответственно первым, втЬрым, третьим, четвертым, пятым, шестым, седьмым, восьмым, девятым, десятым и одиннадцатым выходами блока управления L

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1982 |

|

SU1141399A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| Устройство для выполнения операций умножения и деления | 1980 |

|

SU955038A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU911519A1 |

| Устройство для быстрого преобразования Фурье | 1988 |

|

SU1524066A1 |

| Процессор для цифровой обработки сигналов | 1985 |

|

SU1257662A1 |

| УСТРОЙСТВО ВЫРАВНИВАНИЯ ПОРЯДКОВ ОПЕРАНДОВ | 1992 |

|

RU2006910C1 |

| Устройство для быстрого преобразования Фурье | 1984 |

|

SU1206802A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МЕСТ ПОВРЕЖДЕНИЯ НАПОРНОГО ТРУБОПРОВОДА | 1992 |

|

RU2046251C1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1985 |

|

SU1315969A1 |

1. АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО, содержащее два регистра, пять регистров сдвига, четыре блока элементов И, пять сумматоров, блок памяти и блок управления, причем информационные входы первого и второго регистров являются входом действительной и мнимой частей операнда устройства, информационные входы первого и второго регистров сдвига подключены к выходам групп разрядов блока памяти, соответствующих действительной и мнимой частям коэффициента, выход первого регистра подключен к информационным входам первого и второго блоков элементов И, выход второго регистра подключен к информационным входам третьего и четвертого блоков элементов И, последовательный выход первого регистра сдвига подключен к .управляющим входам первого -и четвертого блоков элементов И, последовательный выход второго регистра сдвига подключен к управляющим входам второго И третьего блоков элементод И, выходы первого и третьего блоков элементов И подключены к входам первого сумматора, выходы второго и четвертого блоков элементов И подключены к входам второго сумматора, выходы третьего, четвертого и пятого сумматоров подключены к информационным входам третьего, четвертого и пятого ре гистров сдвига, соответственно, .выходы третьего, четвертого и пятого регистров сдвига, являющиеся выходами действительной и мнимой частей и угла поворота вектора результата устройства, подключены к первым информационным входам третьего, четвертого и пятого сумматоров соответственно, второй информацион- ный вход пятого сумматора подключен к выходу группы разрядов блока памяти, соответствующей углу поворота вектора коэффициента, тактовый и первый управляющий входы блока управления являются тактовым и уста- ; (Л новочным входами устройства, второй управляющий вход блока управления подключен к выходу знакового разряда третьего регистра сдвига, первый выход блока управления подключен к управляющим входам записи третьего, четв.ертого ипятого регистров рдвига, второй выход блока управления подключен к управляющим входам выдачи .третьего, четвертого и пятого ре1С ю гистров сдвига, третий выход блока управления подключен к управляющим входам записи первого и второго ре4;ib гистров, а также первого и второго, регистров сдвига, четвертей выход блока управления подключен к входу управления сдвигом пятого регистра сдвига, пятый выход блока управления подключен к входам управления сдвигом первого, второго, третьего и четвёртого регистров сдвига, Diecтой выход блока управления подключен к управляющему входу третьего сумматора, седьмой выход блока управления подключен к управляющим входам четвертого и пятого сумматоров, отличающееся тем, что, с целью расширения функциональных возможностей устройства .а счет

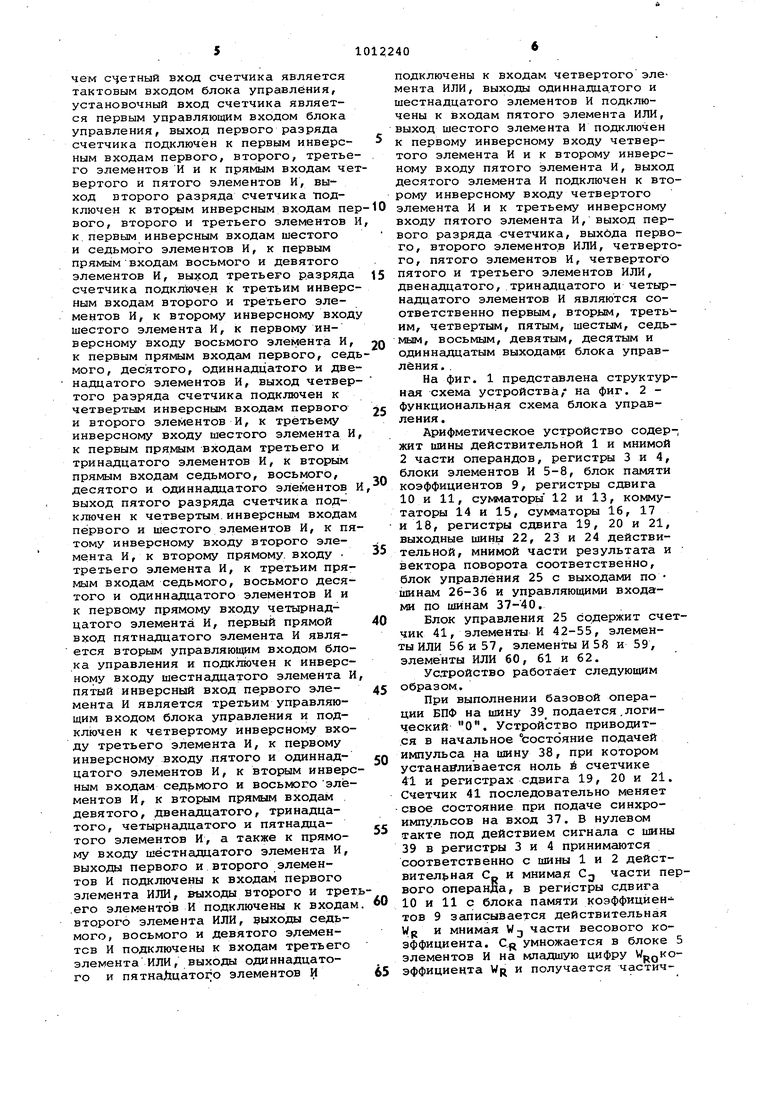

I

Изобретение относится к области автоматики и вычислительной техники и может быть; использовано для выполнения операций над комплексными числами, в частности при выполнении алгоритма быстрого преобразования Фурье. Известно арифметическое устройство, содержащее входные и выходные шины, сумматоры, сдвиговые регистры, логические умножители и обеспечивающее вычисление двухточечного преобразования Фурье и операцию поворота вектора С13. Недостатком известного устройства является его сложность. Наиболее близким к предложенному по техническому решению является арифметическое устройство, содержащее два регистра, пять регистров сдвига,, четыре блока элементов И, пять сумматоров, блок памяти .и блок управления 21. Известное устройство производит вычисление базовой операции быстрого преобразования Фурье (вПФ) по фор мулам : CjWj + Вр; A-, CfiWj + CpWR + Вэ; (CRWR - C-,W-,)+ BR; (CRW3 + CJWR) B-,; Bo многих случаях арифметическое устройство должно дополнительно про изводить операцию перевода комплекс ного вектора из прямоугольной системы координат в полярную, обычно, выполняемую с помощью алгоритма Вол Дёра. . . . Однако известное устройство не способно решать данную задачу, что сужает его функциональные возможнос ти. .Целью изобретения является расши рение функциональных возможностей устройства. Поставленная цель достигается тем, что арифметическое устройство содержащее два регистра, пять регистров сдвига, четыре блока элемен тов И, пять сумматоров, блок памяти и блок управления, причем информационные входы первого и второго регистров являются входом действительной и мнимой частей операнда ус ройства, информационные входы первого и второго регистров сдвига под ключены к выходам прупп разрядов блока памяти, соответствующих дейст вительной и мнимой частям коэффициента, выход первого регистра подклю чен к информёщионным входам первого и второго блоков элементов И, выход второго регистра подключен- к информационным входам третьего и четвертого блоков элементов И, последовательный выход первого регистра сдви га подключен к управляющим входам, первого и четвертого блоков элементов И, последовательный выход второ го регистра сдвига подключен к уп равляющим входам йторого и третьего блоков элементов И, выходы первр го и третьего блоков элементов И подключены к входам первого сумматора, выходы второго и четвертого блоков элементов И подключены к входам второго сумматора, выходы третьего, четвертого и пятого сумматоров подключены к информационным входам третьего, четвертого и пятого регистров сдвига соответственно, выходы третьего, четвертого и пятого регистров сдвига являющиеся выходами действительной и мнимой частей и угла поворота вектора результата уст ройства, подключены к первым информационным входам третьего, четвертого и пятого сумматоров соответственно, второй информационный вход пятого сумматора подключен к выходу 17РУППЫ разрядов блока памяти, соответствующей углу поворота вектора коэффициента, тейстовый и первый управляющий входы блока управления являются тактовым и установочным входами устройства, второй управляющий, вход блока управления подключен к выходу знакового разряда третьего регистра сдвига, первый выход блока управления подключен к управляющим входам записи третьего, четвертого и пятого регистров сдвига, второй выход блока управления подключен к управляющим входам выдачи третьего, четвертого и пятого регистров сдвига, третий выход блока управления подключен к управляющим входам записи первого и второго регистров, а также первого и второго регистров сдвига, четвертый выход блока-управления подключен к входу управления сдвигом пятого регистра сдвига, пятый выход блока управления подключен к входам управления сдвигом первого, второго, третьего и чет.вертого регистров сдвига, шестой выход блока управления подключен к управляющему даходу третьего сумматора, седьмой выход блока управления подключен к управляющим входам четвертого и пятого сумматоров, содержит первый и второй коммутаторы, причем первые информационные входы первого и второго коммутаторов подключены к выходам первого и вто-. рого сумматоров соответствеино, вторые информа1и1рнные входы первого и второго коммутаторов подключены к выходам четвертого и третьего регистров сдвига соответственно, управляющие входы первого и второго коммутаторов подключены к выходам блока управления с восьмого по одинна;вдатый, третий управляющий вход блока управления является входом задания режима работы устройства. Кроме того, блок упргшления состоит из счетчика, шестнадцати элементов И и пяти элементов ИЛИ, причем счетный вход счетчика является тактовым входом блока управления, установочный вход счетчика является первым управляющим входом блока управления, выход первого разряда счетчика подключен к первым инверс ным входам первого, второго, треть го элементов Инк прямым входам ч вертого и пятого элементов И, выход второго разряда счетчика тюдключен к вторым инверсным входам п вого, второго и третьего элементов к первым инверсным входам шестого и седьмого элементов И, к первым прямым входам восьмого и девятого элементов И, выход третьего разряд счетчика подключен к третьим инвер ным входам второго и третьего элементов И, к второму инверсному вхо шестого элемента И, к первому инверсному входу восьмого элемента И к первым прямым входам первого, сед мого, десятого, одиннадцатого и дв надцатого элементов И, выход четвер того разряда счетчика подключен к четвертым инверсным входам первого и второго элементов И, к третьему инверсному входу шестого элемента к первым прямым входам третьего и тринадцатого элементов И, к вторым прямым входам седьмого, восьмого, десятого и одиннадцатого элементов выход пятого разряда счетчика подключен к четвертым.инверсным входам первого и шестого элементов И, к пя тому инверсному входу второго элемента И, к второму прямому, входу . третьего элемента И, к третьим прямым входам седьмого, восьмого десятого и одиннадцатого элементов И и к первому прямому входу четырнадцатого элемента И, первый прямой вход пятнадцатого элемента И является вторым управляющим входом блока управления и подключен к инверсному входу шестнадцатого элемента И пятый инверсный вход первого элемента И является третьим управляющим входом блока управления и подключен к четвертому инверсному входу третьего элемента И, к первому инверсному входу пятого и одиннад цатого элементов И, к вторым инверс ным входам седьмого и восьмого элементов И, к вторым прямым входам . девятого, двенадцатого, тринадцатого, четырнадцатого и пятнадцатого элементов И, а также к прямому входу шестнадцатого элемента И, выходы первого и второго элементов И подключены к входам первого элемента ИЛИ, выходы второго и трет .его элементов И подключены к входам ВТОРОГО элемента ИЛИ, еыходы седьмого, восьмого и девятого элементов И подключены к входам третьего элемента ИЛИ, выходы одиннадцатого и пятнадцатого элементов И подключены к входам четвертогоэлемента ИЛИ, выходы одиннадцатого и шестнадцатого элементов И подключены к входам пятого элемента ИЛИ, выход шестого элемента И подключен к первому инверсному входу четвертого элемента И и к второму инверсному входу пятого элемента И, выход десятого элемента И подключен к второму инверсному входу четвертого элемента И и к третьему инверсному входу пятого элемента И, выход первого разряда счетчика, выхбда первого, второго элементов ИЛИ, четвертого, пятого элементов И, четвертого пятого и третьего элементов ИЛИ, двенадцатого, тринадцатого и четырнадцатого элементов И являются соответственно первым, вторым, третьим, четвертым, пятым, шестым, седьмым, восьмым, девятым, десятым и одиннадцатым выходами блока управления. . На фиг. 1 представлена структурная схема устройства,- на фиг. 2 функциональная схема блока управления . Арифметическое устройство содер-, жит шины действительной 1 и мнимой 2 части операндов, регистры 3 и 4, блоки элементов И 5-8, блок памяти коэффициентов 9, регистры сдвига 10 и 11, сумматоры 12 и 13, коммутаторы 14 и 15, сумматоры 16, 17 и 18, регистры сдвига 19, 20 и 21, выходные шины 22, 23 и 24 действительной, мнимой части результата и вектора поворота соответственно, блок управления 25 с выходами по шинам 26-36 и управляющими входами по шинам 37-40, Блок управления 25 содержит счетчик 41, элементы И 42-55, элементы ИЛИ 56 и 57, элементы И 58 и 59, элементы ИЛИ 60, 61 и 62. Устройство работает следующим образом. При выполнении базовой операции БПФ на шину 39 подается.логический О. Устройство приводится в начальное состояние подачей импульса на шину 38, при котором устанавливается ноль и счетчике 41 и регистрах сдвига 19, 20 и 21. Счетчик 41 последовательно меняет свое состояние при подаче синхроимпульсов на вход 37. В нулевом такте под действием сигнала с шины 39 в регистры 3 и 4 принимаются соответственно с шины 1 и 2 действител|зная С,, и мнимая C-j части первого операнда, в регистры сдвига 10 и 11 с блока памяти коэффициентов 9 Зошисывается действительная WP и мнимая W-J части весового коэффициента. Cjj умножается в блоке 5 элементов И на младшую цифру WJ KOэффициечта WR и получается частичное произведение . Аналогично блок 6 производит умножение С на младшую цифру получается блок 7 производит действие CgW-jQ, а блок 8 - действие . Сумматор 12 суммирует йулевые по счету частичные произведения и получает Ro C W p-CjWjQ, сумма тор 13 суммирует частичные произведения и получает К.,о ,o+С-,. Коммутаторы ,14 и 15 пропускают K-j на сумматоры 16 и 17, где они складываются 9 нулевым содержимым регисров 19 и 20 соответственно. По сигналу с шины 26 K-JQ записываются соответственно в регистры 19 и 2

В первом такте содержимое регистров 10, 11, 19 и 20 сдвигается вправо по сигналу с шины 29. В этом же такте блок 5 производит умножение Сд на следующую младшую цифру КЛ которая получилась путем сдвига содержимого регистра 10, и получает CfjW, блок б производит действие Сри-,,блок 7 - действие .j и блок 8 - Действие C-jWp. Сумматор 12 производит действие ijWjj -C.jW.j

а сумматор 13 - действие очередные суммл пар частичных произведений,, пройдя через коммутаторы 14 и 15 соответственно, суммируются на сумматорах 16 и 17 со сдвинутым содёржимым регистров 19 , и 20 соответственнр. По сигналу с шины 26 в регистр 19 записывается

Кои + 2 Кот а в регистр 19 If J-

K-j + K,-,g.

В следующем такте по сигналу с шины 29 содержимое этих регистров, а также регистров 10, 11 сдвигается в сторону младших разрядов (вправо).

Аналогично в зарершающем одиннадцатом такте умножения на двенадцатиразрядные весовые коэффициен-. ты WR W-, блок 5 умножает Лц на цифру W(j и получает CoWf, блок 6 получает ,,блок 7 - С-, блок 8 .- C-jW Су1 1аторы 12 и 13 соответственно производят действия

NJ11° a Qi-l ISi-r йЧ) результаты которых К кладываются со сдвинутым содержимым регистров 19 и 20 соответственно. Результаты

.

2( - C.,W)

Ri

H-11

C-jWp)

Ji

записываются в регистры 19 и 20 соответственно.

В двенадцатом такте по сигналу с шины 30 содержимое регистров 19 и 20 сдвигается вправо, действительная В и мнимая Bj части второго операнда записываются в регистры 3 и 4 соответственно, так что Вр и B.J пройдя через блоки 5 и 8 и складываясь с нулем на сумматорах 12 и

5 13, подаются через коммутаторы 14 и 15 на первые входы сумматоров 16 и 17 соответственно и суммируются с содержимым регистров 19 и 20. По сигналу с шины 26 в .регистры 19 и

0 20 записываются А-.р CpWp - C-,W,+ В NJ + Ъ соответ- ственнр.

В тринадцатом такте по сигналу с шины 30 .содержимое регистров 19 и 5 20 сдвигается вправо. В этом же

такте сдвинутое содержимое регистров 19 и 20 соответственно 0,5 А и 0,5 Aj-j выдается в шины 22 и 23 по стробирующему сигналу с шины 27,

Q а также через коммутаторы 15 и 14 поступает на первые входы сумматоров 16 .и 17. При этом вторые входы сумматоров отключаются. Таким образом, в регистры 19 и 20 соответственно записываются 0,5 0,5 ,

В четырнадцатом такте, содержимое регистров 19 и 20 через коммутаторы 15 и 14 соответственно поступает на первые входы сумматоров 17 и 16,

0 У которых отключены вторые входы. Таким образом, сумматоры производят соответственно вычитание иэ нуля содержимого регистров 19 и 20, и в эти регистры по сигналу с шины 26 запи. сываются 0,5 0,5 h - -coo-metci5 венно.

В пятнадцатом такте, также как и в двенадцатом, к содержимому регистров 19 и 20 прибавляется соответст-. венно действительная и мнимая часть

0 второго операнда Вп и В- , и в регистрах 19,20 оказывается вторая пара результатов:

0 R

5 0,5 A,B.j-0,5( + АзМд)-0,5 8,

которая по стробирующему сигналу с шины 27 выдается соответственно в шины 22 и 23. Уменьшение результатов базовой операции БПФ вдвое

50 не имеет существенного значения, так как например, при выполнении сшгоритма быстрого преобразования Фурье с автоматическим масштабированием необходимо результаты всех

5 базовых операций БПФ уменьшить вдвое во избежание переполнения разрядной сетки арифметического устройства.

Чаще всего алгоритм Волдера используется для перевода комплексного

0 операнда из прямоугольной система координат в полярную. Он основан на операции поворота вектора. Исходными дааными такого алгоритма являются координаты комплексного вектора

65 в прямоугольной системе координат

х Ajj, YQ- Aj и начальный угол а1лгоритма G О, В каждой операции алгоритма производятся действия

2- У .

i

V - Р 2 X

У X, ,

141

в. -I- Е а ГС t g 2

в 1 + 1

Г+1 при у- О i

где bi

1 при у 0.

Результатами алгоритма.яв модул1ь комплексного BeKTOpja

, и его фазае -Qrctffгде К ci 1,647.

При выполнении алгоритма Волдера на шину 39 подается уровень 1, а на шину 38 - импульс установки в начальное состояние. В нулевом такте по сигналу с шины 28 в регистры 3,и 4 соответственно принимаются дейст-г вительная An и мнимая А-, части комплексного операнда с входных шин 1 и 2. Выход регистра 10 выдает 1,

а выход регистра 10 - О

Таким

образом, Aj и A;j проходят неизменными через блоки 5 и 8 соответственно, сумматоры 12 и 13, входы коммутаторов 14 и 15 и сукматор4я 16 и 17 и по сигналу с шины26 записываются соответственно в регистры 19 и 20 как X(j и YQ. В первом такте XQ из -регистра 19 проходит через коммутатор15 на вход сумматора 17. взавиСимЬсти от знака CQ операнда Уд сумматор 17 по с шины 32 склэдывает х с YQ или вычитает -л, из у, Аналогично на сумматоре 16 из XQ вычитается или прибавляется Уд по сигналу с шины 31. Из блока 9 памяти коэффициентов выдается число равное arctg 2°, которое вычитается или с..; складывается в зависимости от знака БО с нулевым содержимым регистра 21 на сумматоре 18. Результаты первой операции алгоритма

VSo2%r .

0 eo+eo«rct«f2

соответственно записываются в регистры 19, 20 и 21 по сигналу с шины 26. Таким же образом во втором такте в регистры 19, 20 и 21 соответственно записыв цотся результаты второй операции

ei24. ,,

ejse +E oirctef 2

Йри этом кок1Мутаторы 14 и 15 пропускают операнды сдвинутыми на один разряд вправо, или то же самое уменьшенными на Z, число arctg 2 выдается блоком 9 памяти коэффициентов. Итак, в двенадцатом такте содержимое регистров 19 и 20 соответственно x-f-| и проходит через коммутаторы 15 и 14 со сдвигом одиннадцать разрядов и как t-f алгебраически суммируется на сумматорах 17 и 16 с содерзкимЕлм.регистров

20 и 19. Из блока памяти коэффициентов выдается число arctg ,которое суммируется на сумматоре 18 с содержимым регистра 21. Результаты последней операции

1

rll

,1«- Н2

по сигналу с шины 26 записываются соответственно в регистры 19, 20 и 21.

В тринадцатом такте сигнал с шины 27 стробирует выдачу результатов алго)итма Волдера

,А

и

45

(Собтветственно в шьлы 22 и 24.

Таким образом, предложенное устройство выполняем оба стандартных алгоритма, что расширяет его функцио Q нальные возможности.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Арифметическое устройство | 1978 |

|

SU706846A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 2860043/18-24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-04-15—Публикация

1981-11-23—Подача