1

Изобретение относится к запоминающим устройствам.

Известно запоминающее устройство с само.контролем, содержащее накопитель, регистры адреса и слова, блок управления, блок контроля 1.

Недостатком зтого устройства являются большие аппаратурные затраты.

Наиболее близким техническим решением к изобретению является запоминающее устройство с самоконтролем, содержащее накопитель, подключенный к регистру адреса и ретистру слова, соединенному с блоком контроля и блоком кодирования, блок управления, блок декодирования 2. Однако реализация корректирующих кодов, исправляющих многократные ошибки, требует значительной избыточности памяти, т.е. числа дополнительных разрядов дпя исправления ошибок и больших аппаратурных затрат на блоки кодирювания и декодирования, что снижает надежность устройства.

Если подавляющее большинство ошибок вызвано отказами типа генератор О и генератор 1, то коррекция ошибок может быть

осуществлена с меньшей избыточностью накопителя.

Целью изобретения является повышение надежности устройства при корре.кции многократных ошибок.

Достигается это тем, что запоминающее устройство содержит регистр сдвига, элементы И, коммутатор и последовательно соединенные дополнительные накопители, вход одного из которых соединен с выходом регистра

10 адреса, выход другого дополнительного накопителя подключен к первому входу коммутатора, вход регистра сдвига соединен с выходом блока управления а - с вторым входом коммутатора, выход которого подклю15чен к одному из входов регистра слова, входБ элементов И соединены с выходами регистра слова, а выходы - с выходами устройства.

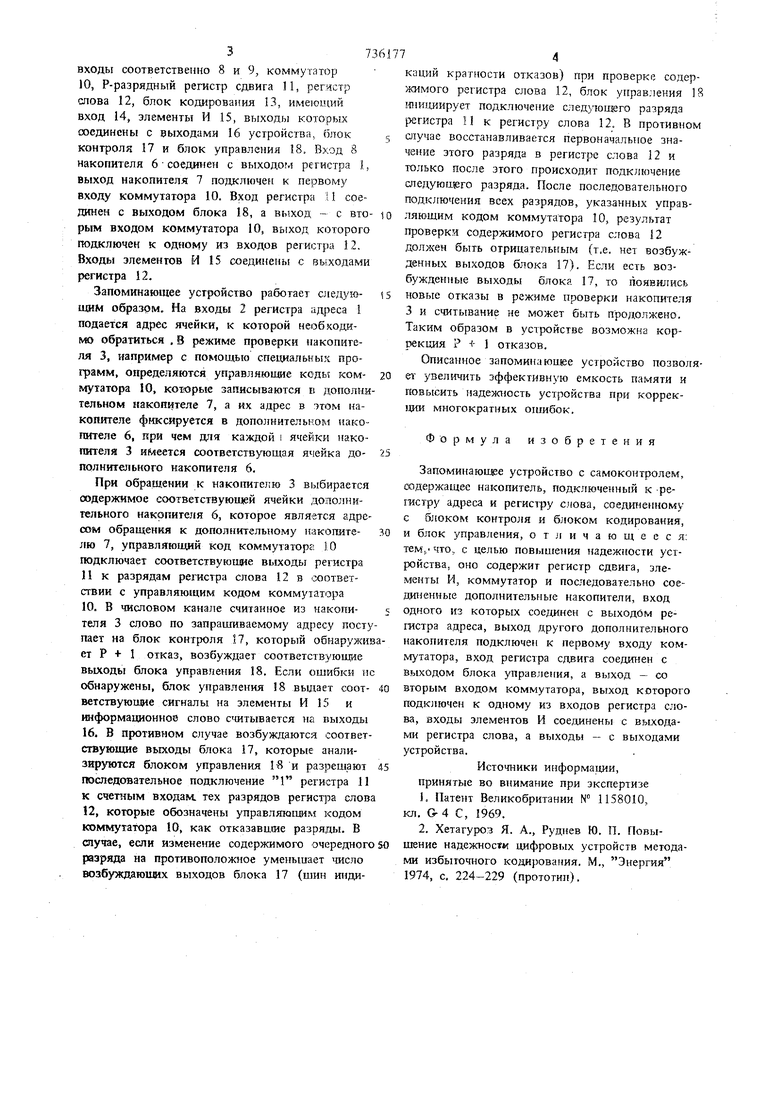

На чертеже изображена блок-схема предлагаемого устройства.

20

Устрюйство содержит регистр адреса 1 с входами 2, накопитель 3 с входами 4 и вы ходами 5, последовательно соединенные дополнительные накопители 6 и 7, имеющие ВХОДЫ соответственно 8 и 9, коммутатор 10, Р-разрядный регистр сдвига 11, регястр слова 12, блок кодирования 13, имеющий вход 14, элементы И 15, выходы которьгх отединены с выходами 16 устройства, блок контроля 17 и блок управления 18. Вход 8 накопителя 6 соединен с выходом регистра 1, выход накопителя 7 подключен к первому входу коммутатора 10. Вход регистра И соединен с вььходом блока 18, а выход - с вторым входом коммутатора 10, которого подключен к одному из входов регистра 12. Входы элементов И 15 соединень с вьЕходами регистра 12, Запоминающее устройство работает следующим образом. На входы 2 регистра адреса 1 подается адрес ячейки, к которой необкодилда обратиться , В режиме проверки накопителя 3, например с помощью специальных программ, определяются управляющие коды коммутатора 0, котярые записываются в дополни тельном накопителе 7, а их адрес в этом накопителе фиксируется в дополнительном накопителе 6, при чем для каждой i ячейки накопителя 3 имеется соответствующая ячейка дополнительного накопителя 6. При обращении к накопителю 3 выбирается содержимое соответствующей ячейки дополнительного накопителя 6, которое является адресом обращения к дополнительному наколителю 7, управляющий код коммутатора 10 подключает соответствующие выходы регистра 11 к разрядам регистра слова 12 в соответствии с управляющим кодом коммутатора 10. В числовом канале считанное из накопителя 3 слово по запрашиваемому адресу посту пает на блок контроля 17, который обнаружи ет Р + I отказ, возбуждает соответствуюиие выходы блока управления 18. Если ошибк н обнаружены, блок управления 18 вьщает соответствуюшие сигналы на элементы И 15 и информационное слово считывается а выходы 16. В противном случае возбуждаются соответ ствующие выходы блока 17, которые анализируются блоком управления 1-8 и разрешают последовательное подключение 1 регистра 11 к счетным входам, тех разрядов регист1:а слов 12, которые обозначены управляющим кодом коммутатора 10, как отказавише разряды, В случае, если изменение содержимого очередног разряда на противоположное уменьшает число возбуждаюиих выходов блока 17 (шин инди734 каций кратности отказов) при проверке содержимого регистра слова 12, блок управления 18 Ш ивдирует подключение следующего разряда регистра 1 к регистру слова 12. В противном случае восстанавливается первоначальное значение этого разряда в регистре слова 12 и только после этого происходит подключение следую 1 ;го разряда. После последовательного подключения всех разрядов, указанных управляющим кодом коммутатора 10, результат проверки содержимого регистра слова 12 быть отрицательным (т.е. нет возбужденнь х выходов блока 17). Если есть возбужденные выходы блока 17, то появились новые Отказы в режиме проверки накопителя 3 и считывание не может быть продолжено. Таким образом в устройстве возможна коррекция Р + 1 отказов. Описанное запоминающее устройство позволяет увеличить эффективную емкость памяти и гюБысить надежность устройства при коррекции многократных опшбок. Формула изобретения Запоминающее устройство с самоконтролем, содержащее накопитель, подключенный к -регастру адреса и регистру слова, соединенному с блоком контроля и блоком кодирования, и блок управления, отличающееся; тем,. что, с целью повышения адежности устройства, оно содержит регистр сдвига, элементы И, коммутатор и последовательно соединенные дополнительные накопители, вход одного из которых соединен с выходом регистра адреса, выход другого дополнительного накопителя подключен к первому входу коммутатора, вход регистра сдвига соединен с выходом блока управления, а выход - со вторым входом коммутатора, выход которого подключен к одному из входов регистра с.Юва, входы элементов И соединены с выходами регистра слова, а выходы - с выходами устройства. Источники информации, принятые во внимание при экспертизе 1.Патент Великобритании № 1158010, кл. 0-4 С, 1969. 2.Хетагуроз Я. А., Руднев Ю. П. Повыщение надежности цифровых устройств методами избыточного кодирования. М., Энергия 1974, с. 224-229 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1981 |

|

SU972600A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU964737A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU955212A2 |

| Запоминающее устройство с самоконтролем | 1976 |

|

SU600618A1 |

| Запоминающее устройство с самоконтролем | 1975 |

|

SU608202A1 |

| Запоминающее устройство с самоконтролем | 1976 |

|

SU618799A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1133623A2 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| Запоминающее устройство с исправлением ошибок | 1983 |

|

SU1133624A1 |

| Запоминающее устройство с коррекцией ошибок | 1982 |

|

SU1075312A1 |

Авторы

Даты

1980-05-25—Публикация

1977-11-09—Подача