Изобретение относится к запоминающим устройствам и может найти приме нение в цифровых вычислительных машинах, выполненных на функциональных узлах с большой степенью интеграции.

Известно Запоминающее устройство с самоконтролем, содержащее накопитель с адресными и разрядными цепями, регистр адреса, регистр слова, блок кодирования и схему коррекции 13.

Недостатком этого устройства является низкая надежность, обусловленная малой корректирующей способностью применяегиых в нем кодов.

Наиболее близким к изобретению является запоминающее устройство с обнаружением и исправлением ошибок, содержащее кодер, процессор декодер. Кодер состоит из множества сумматоров по модулю два, входы которых соединены со всеми разрядами байта, и множества сумматоров по модулю-два, входы которых соединены с разрядами слова, согласно принципу образования применяемого кода. . .

Декодер состоит из двух вычислителей синдрома из аналогичных множеств сум}латоров по модулю два, вычислителя критериев корректора ошибок 2.

. Недостатками известного устрой ства. являются низкая обнаруживеиощая и корректирующая способность, так как имеется возможность исправлять ошибку только в пределах одного байта и большие затраты оборудования на реализацию применяемого кода. Указанные обстоятельства снижают надежность устройства. .

10

Цель изобретения - повышение надежности запоминающего устройства.

Поставленная цель достигается тем, что в запоминающее устройство с самоконтролем, содержащее накопитель,

15 подключенный к адресному блоку, вход которого соединен с выходом регистра адреса, и разрядному блоку, вход и выход которого подключены соответственно к первым выходу и входу

20 регистра прямого числа, вторые вход и выход которого соединены соответственно с первыми выходом и входом блока кодирования - декодирования, введены регистр инверсного числа, буфер25ный регистр, схема сравнения, счетчик и распределитель сигналов, входы которого подключены к выходу счетчика и первому выходу схемы сравнения, la выход соединен с третьим входом

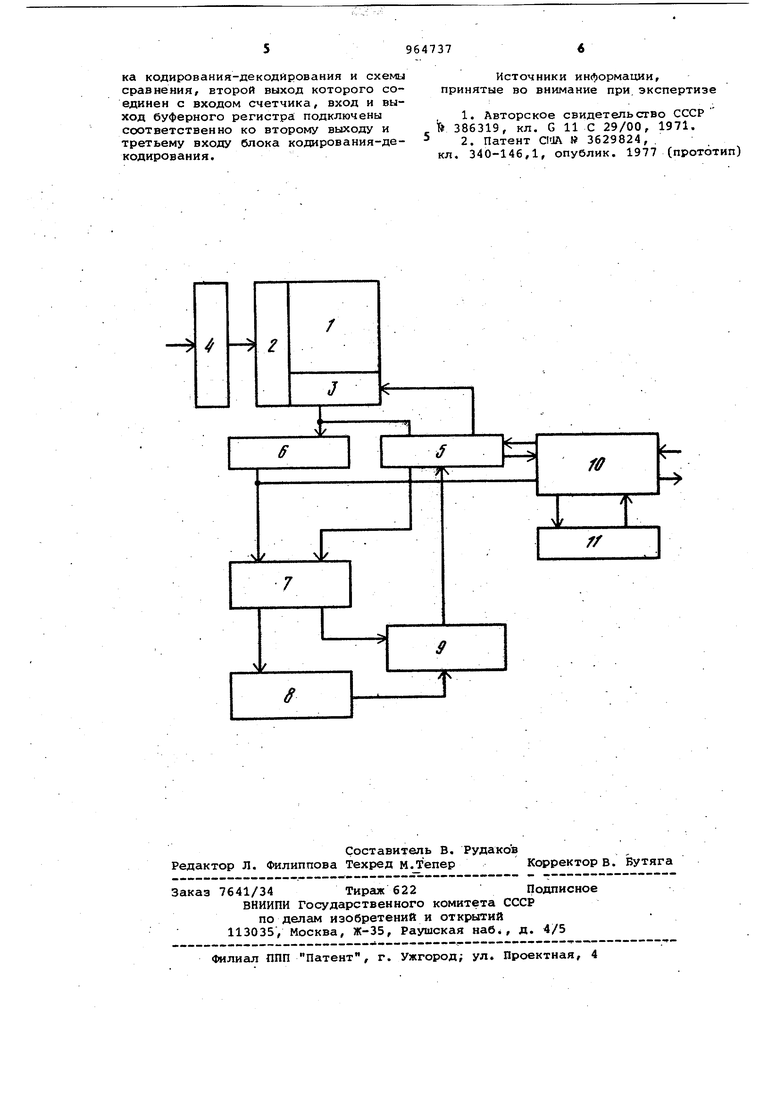

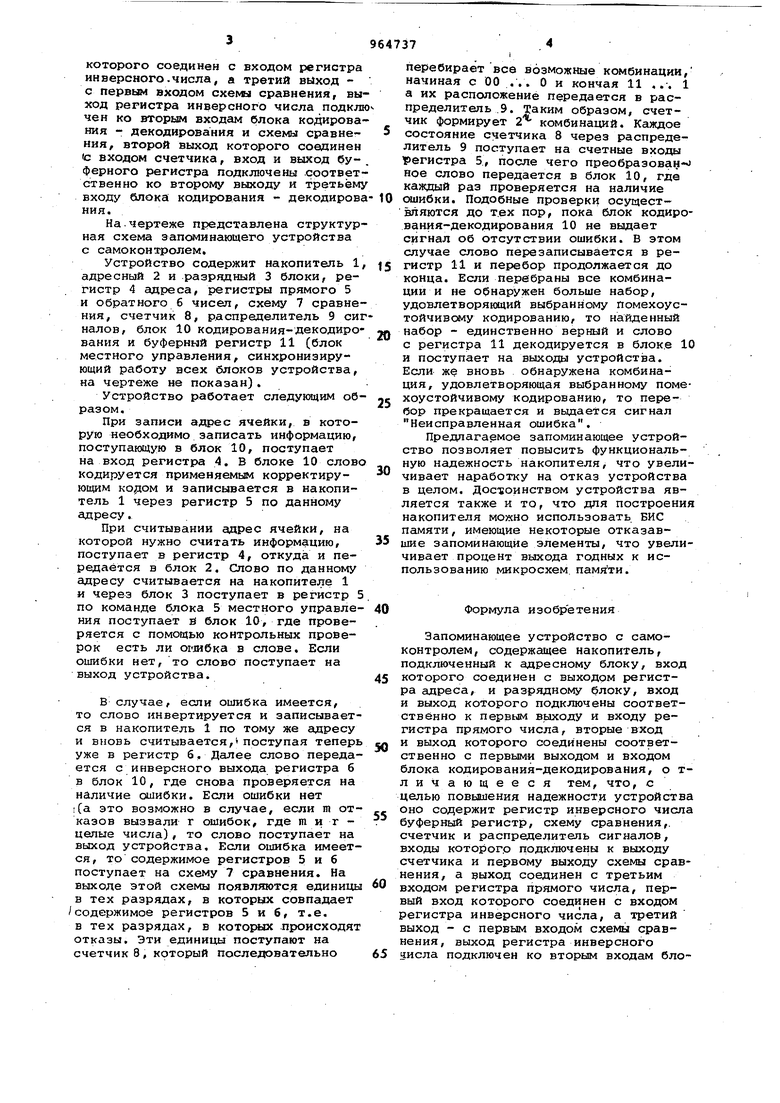

30 регистра прямого числа, первый вход которого соединен с входом регистра инверсного.числа, а третий выход с первым входом схем сравнения, вы ход регистра инверсного числа подкл чей ко вторым входам блока кодирова ния - декодирования и схемы сравнеНИН, второй выход которого соединен с входом счетчика, вход и выход буферного регистра подключены .соответ ственно ко второму выходу и третьему входу блока кодирования - декодирова ния. На.чертеже представлена структур ная схема запоминающего устройства с самоконтролем. Устройство содержит накопитель 1 адресный 2 и .разрядный 3 блоки, регистр 4 адреса, регистры прямого 5 и обратного 6 чисел, схему 7 сравнения, счетчик 8, распределитель 9 сиг налов, блок 10 кодирования-декодировакия и буферный регистр 11 (блок местного управления, синхронизирующий работу всех блоков устройства, на чертеже не показан). Устройство работает следующим образом. При записи адрес ячейки, в которую необходимо записать информацию, поступающую в блок 10, поступает на вход регистра 4. В блоке 10 слово кодируется применяемым корректирующим кодом и записывается в накопитель 1 через регистр 5 по данному адресу. При считывании адрес ячейки, на которой нужно считать информацию, поступает в регистр 4, откуда и передаётся в блок 2. Слово по данному адресу считывается на накопителе 1 и через блок 3 поступает в регистр 5 по команде блока 5 местного управления поступает в блок 10, где проверяется с помощью контрольных проверок есть ли о1Шбка в слове. Если ошибки нет, то слово поступает на выход устройства. В случае, если ошибка имеется, то слово инвертируется и записывается в накопитель 1 по тому же адресу и вновь считывается,поступая теперь уже в регистр б. Далее слово передается с инверсного выхода регистра б в блок 10, где снова проверяется на наличие оиибки. Если ошибки нет ;(а это возможно в случае, если m отказов вызвали г ошибок, где m и г целые числа), то слово поступает на выход устройства. Если ошибка имеется, то содержимое регистров 5 и б поступает на схему 7 сравнения. На выходе этой схемы появляются единицы в тех разрядах, в которых совпадает /содержимое регистров 5 и б, т.е. в тех разрядах, в которых происходят отказы. Эти единицы поступают на счетчик 8 , который последовательно перебирает все возможные комбинации, начиная с 00 ... О и кончая 11 ... 1 а их расположение передается в распределитель .9. Таким образом, счетчик формирует комбинаций. Каждое состояние счетчика 8 через распределитель 9 поступает на счетные входы Регистра 5, после чего преобразован-о ное слово передается в блок 10, где каждый раз проверяется на наличие ошибки. Подобные проверки осуществляются до т.ех пор, пока блок кодирования-декодирования 10 не выдает сигнал об отсутствии ошибки. В этом случае слово перезаписывается в регистр 11 и перебор продолжается до конца. Если перебраны все комбинации и не обнаружен больше набор, удовлетворяющий выбранному помехоустойчивому кодированию, то найденный набор - единственно верный и слово с регистра 11 декодируется в блоке 10 и поступает на выходы устройства. Если же вновь обнаружена комбинация, удовлетворяющая выбранному помехоустойчивому кодированию, то перебор прекращается и выдается сигнал Неисправленная ошибка. Предлагаемое запоминающее устройство позволяет повысить функциональную надежность накопителя, что увеличивает наработку на отказ устройства в целом. Достгоинством устройства является также и то, что для построения накопителя можно использовать БИС памяти, имеющие некоторые отказавише запоминающие элементы, что увеличивает процент выхода годных к использованию микросхем, памяти. Формула изобретения Запоминающее устройство с самоконтролем, содержащее накопитель, подключенный к адресному блоку, вход которого соединен с выходом регистра адреса, и разрядному блоку, вход и выход которого подключены соответственно к первым вьаходу и входу регистра прямого числа, вторые вход и выход которого соединены соответственно с первьми выходом и входом блока кодирования-декодирования, о тличающееся тем, что, с целью повышения надежности устройства Оно содержит регистр инверсного числа буферный регистр, схему сравнения,, счетчик и распределитель сигналов, входы которого подключены к выходу счетчика и первому выходу схемы сравнения, а выход соединен с третьим входом регистра прямого числа, первый вход которого соединен с входом регистра инверсного числа, а третий выход - с первым входом схемы сравнения, выход регистра инверсного числа подключен ко вторым входам блока кодирования-декодирования и схемы сравнения, второй выход которого соединен с входом счетчика, вход и выход буферного регистра подключены соответственно ко второму выходу и третьему входу блока кодирования-декодирования.

Источники информации, принятые во внимание при. экспертизе

1. Авторское свидетельство СССР ft 386319, кл. G 11 С 29/00, 1971. 2. Патент США 3629824,

кл. 340-146,1, опублик. 1977 (прототип)

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1157575A1 |

| Запоминающее устройство | 1988 |

|

SU1531175A1 |

| Запоминающее устройство | 1972 |

|

SU448480A1 |

| Запоминающее устройство с самоконтролем | 1979 |

|

SU855730A1 |

| Запоминающее устройство с тестовым самоконтролем | 1986 |

|

SU1396160A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1048520A1 |

| Запоминающее устройство с самоконтролем | 1978 |

|

SU746744A1 |

| Запоминающее устройство с автономным контролем | 1991 |

|

SU1837363A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО„. -..,-•. ."р л С^аог^'-.---'^--:: '•^k^Vfi''-'- | 1973 |

|

SU375675A1 |

| Запоминающее устройство с самоконтролем | 1975 |

|

SU608202A1 |

-

fO

Г

//

Авторы

Даты

1982-10-07—Публикация

1981-01-09—Подача