Изобретение относится к запоминающим устройствам.

Известно запоминающее устройство с самоконтролем, в котором при появлении ошибок, вызванных отрезками в основных ячейках памяти, происходит обращение в резервные ячейки памяти, число которых ограничено 1.

Недостатком этого устройства является низкая надежность.

Наиболее близким техническим решением к изобретению является запоминающее устройство с самоконтролем, содержащее регистр адреса, соединенный с двумя дешифраторами адреса, которые подключены к двум адресным накопителям, соединенным с выходным регистром, причем к накопителям подключены два основных регистра слова, соединенные со схемой равенства кодов, которая через схему И подключена к первому основному регистру слова, и группой схем ИЛИ, подключенной к выходному регистру, каждый из основных регистров слова также связан с одним из двух дополнительных регистров слова и с одной из двух схем поразрядной проверки, с которыми соединены и дополнительные регистры слова, а схемы поразрядной проверки

через Группы элементов И подключены к основным регистрам слова, блок управления связан с регистром адреса, накопителями, основными регистрами слова, схемой И, дополнительными регистрами слова, группами схем и выходным регистром 2.

Недостатками известного устройства являются невысокое быстродействие

10 и ошибочность работы при возникновении отказов в одноименных разрядах одноименных ячеек накопителей, так как при выдаче информации с основных регистров слова одноименные

15 разряды заблокированы, что снижает надежность устройства.

Цель изобретения - повышение быстродействия и надежности устройства.

20

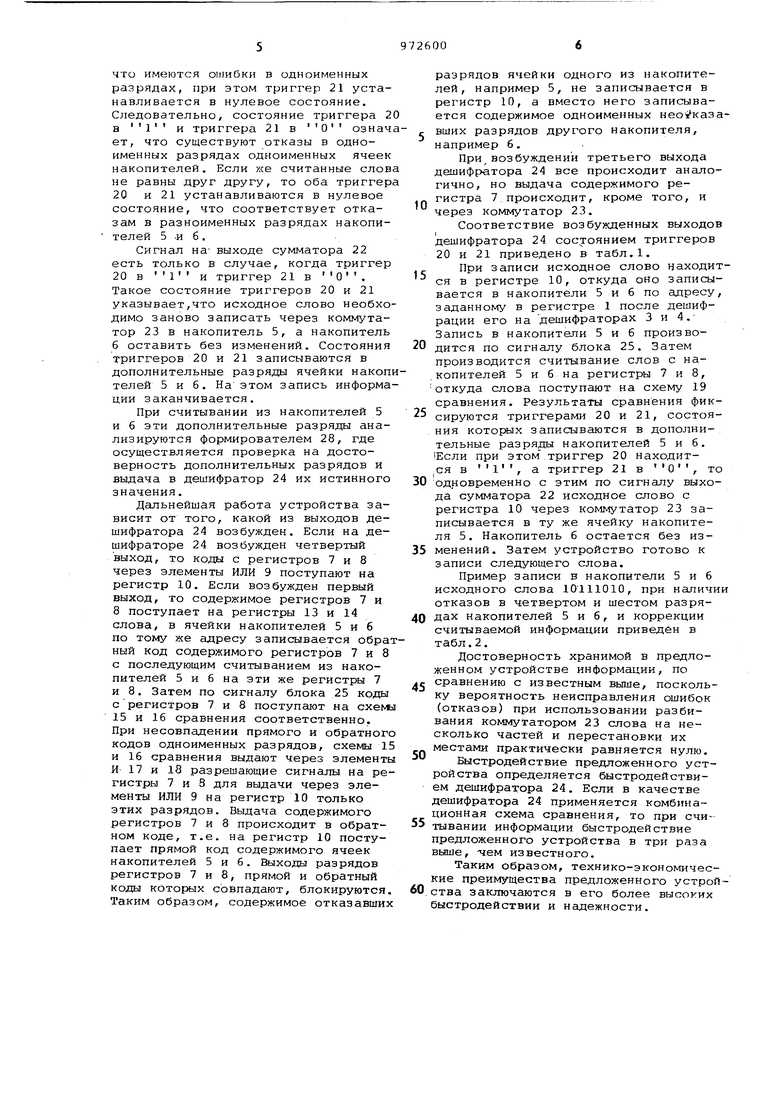

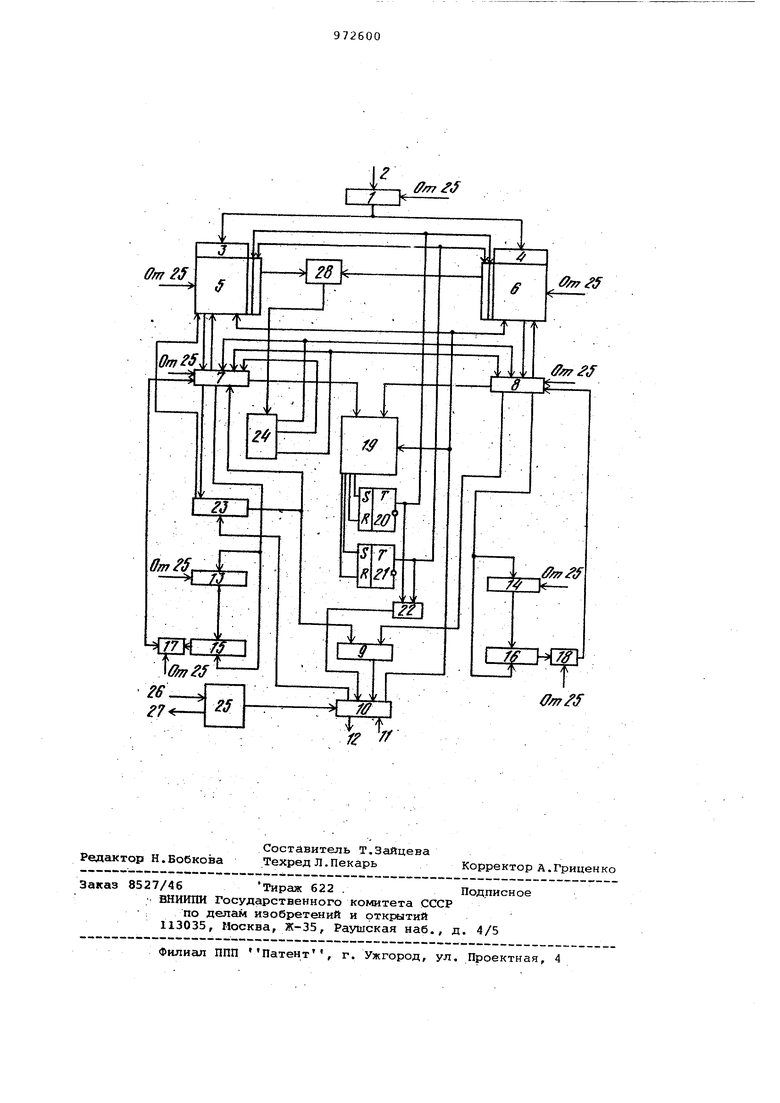

Поставленная цель достигается тем, что и запоминающее устройство с самоконтролем, содержащее регистр адреса, выходы которого соединены с входами первого и второго дешифрато25ров, выходы которых подключены к адресным входам первого и второго накопителей, регистры слова, cxeNH сравнения, элементы ИЛИ и элементы И, причем первые входы и выходы перво30го и второго регистров слова соединены с одними из информационных выходов и входов первого и второго накопителей, другие информационные входы которых подключены к первому выходу третьего регистра слова, вто рые выходы первого и второго регист ров слова соединены соответственно с входами четвертого регистра слова и одними из входов первой схемл сра нения и с входами пятого регистра слова и одними из входов второй схе мы сравнения, другие входы первой и второй схем сравнения подключены соответственно к выходам четвертого и пятого регистров слова, а выходы к первым входам первого и второго элементов И, выходы которых соедине ны соответственно с вторыми входами первого и второго регистров слова, третьи выходы которых подключены соответственно к первому и ко второ му входам третьей схемы сравнения, третий вход которой соединен с первым выходом третьего регистра слова первый вход которого подключен к выходу элемента ИЛИ, первый вход ко торого соединен с четвертым выходом второго регистра слова, управляющие входы регистра адреса, накопителей, регистров слова и вторые входда элем тов И подключены к выходам блока управления, вторие вход- и вь:ход третьего регистра слова являются ин формационными входами и выходом уст ройства, введены триггеры, сумматор по модулю два, коммутатор, третий дешифратор и формирователь контроль ных сигналов, причем входы триггеров подключены к выходам третьей схемы сравнения, выход первого триг ра соединен с первыми контрольными входами накопителей и первым входом сумматора по модулю два, выход которого подключен к третьему входу третьего регистра слова, а второй вход - к выходу второго триггера и вторым контрольным входам накопителей, другие информационные выходы которих подключены соответственно к первому и ко второму входам формирователя контрольных сигналов, выход которого соединен с входом третьего дешифратора, одни из выходов которого подключены соответст венно к третьим и к четвертым входам первого и второго регистров Флова и к пятому входу первого регистра слова, шестой вход которого соединен со вторым входом элемента ИЛИ и первым выходом коммутатора, первый и второй входы которого подключены соответственно к третьему выходу третьего регистра слова и к четвертому выходу первого регистра слова, второй выход коммутатора сое динен с контрольным входом первого накопителя. На чертеже изображена функциональая схема предложенного устройства. Устройство содержит регистр-1 адреса с входами 2, первый 3 и второй 4 дешифраторы, первый 5 и второй 6 накопители, первый 7 и второй 8 регистры слова, элементы ИЛИ 9, третий регистр 10 слова с информационными входами 11 и выходами 12, четвертый 13 и пятый 14 регистры слова, первую 15 и вторую 16.exeМ1Л сравнения, первый 17 и второй 18 элементы И, третью схему 19 сравнения, первый 20 и второй 21 триггеры, сумматор 22 По модулю два, коммутатор 23, третий дешифратор 24, блок 25 управления с входом 26 и выходом 27 и формирователь 28 контрольных сигналов . Устройство работает следующим образом. Информация одновременно записывается и считывается с обоих накопителей 5 и 6. При возникновении отказов в ячейках, для получения слова без ошибок используются неотказавшие разряды ячеек, а отказавшие блокируются. Но если отказы есть в одноименных разрядах, то при блокировке оказавших разрядов есть ошибка. Для устранения сшибок при блокировке отказавших одноименных разрядов записывается слово в один из накопителей 5 или 6 записывается без изменений, а в другой записывается через коммутатор 23, который разбивает исходное слово, например, на две части и меняет их местами. При считывании с обоих накопителей 5 и 6 оба слова имеют ошибки в одноименных разрядах, но слово, считанное из накопителя 5, необходимо снова пропустить через коммутатор 23, т.е. снова поменять местами части слова, вследствие чего ошибки окажутся в других разрядах по сравнению со словами, считанным из накопителя 6. Таким образом, произойдет разнесение ошибок в разноименные разряды, а, следовательно, теперь уже возможно получение правильного слова при помощи двух слов с ошибками. Для того, чтобы определить, когда имеют место отказы в одноименных разрядах, используются схема 19 сравнения, триггеры 20 и 21 и сумматор 22, Первоначальное исходное слово записывается в оба накопителя 5 и 6, затем производится считывание и сравнение считанных слов схемой 19. Если имеет место равенство, то триггер 20 устанавливается в единичное состояние. Также производится сравнение одного из считанных слов (поскольку они равны) с исходным словом,размещенным на регистре 10. Если не имеет места равенство, то это означает. что имеются ошибки в одноименных разрядах, при этом триггер 21 устанавливается в нулевое состояние. Следовательно, состояние триггера 2 1 и триггера 21 в ет, что существуют отказы в одноименных разрядах одноименных ячеек накопителей. Если же считанные слов не равны друг другу, то оба триггер 20 и 21 устанавливаются в нулевое состояние, что соответствует отказам в разноименных разрядах накопителей 5 -и 6 . Сигнал на- выходе сумматора 22 есть только в случае, когда триггер 20 в и триггер 21 в О. Такое состояние триггеров 20 и 21 указывает,что исходное слово необхо димо заново записать через коммутатор 23 в накопитель 5, а накопитель 6 оставить без изменений. Состояния триггеров 20 и 21 записываются в дополнительные разряды ячейки накоп телей 5 и 6. На этом запись информа ции заканчивается. При считывании из накопителей 5 и б эти дополнительные разряды анализируются формирователем 28, где осуществляется проверка на достоверность дополнительных разрядов и выдача в дешифратор 24 их истинного значения. Дальнейшая работа устройства зависит от того, какой из выходов дешифратора 24 возбужден. Если на дешифраторе 24 возбужден четвертый выход, то коды с регистров 7 и 8 через элементы ИЛИ 9 поступают на регистр 10. Если возбужден первый выход, то содержимое регистров 7 и 8 поступает на регистры 13 и 14 слова, в ячейки накопителей 5 и 6 по тому же адресу записывается обра ный код содержимого регистров 7 и 8 с последующим считыванием из накопителей 5 и б на эти же регистры 7 и 8. Затем по сигналу блока 25 коды с регистров 7 и 8 поступают на схем 15 и 16 сравнения соответственно. При несовпадении прямого и обратног кодов одноименных разрядов, схемы 1 и 16 сравнения выдают через элемент И 17 и 18 разрешающие сигналы на ре гистры 7 и 8 для выдачи через элементы ИЛИ 9 на регистр 10 только этих разрядов. Выдача содержимого регистров 7 и 8 происходит в обратном коде, т.е. на регистр 10 поступает прямой код содержимого ячеек накопителей 5 и 6. Выходы разрядов регистров 7 и 8, прямой и обратный коды которых совпадают, блокируются Таким образом, содержимое отказавших означ разрядов ячейки одного из накопителей, например 5, не записывается в регистр 10, а вместо него записывается содержимое одноименных нео казавших разрядов другого накопителя, например 6. При возбуждении третьего выхода дешифратора 24 все происходит аналогично, но выдача содержимого регистра 7 происходит, кроме того, и через коммутатор 23. Соответствие возбужденных выходов дешифратора 24 состоянием триггеров 20 и 21 приведено в табл.1. При записи исходное слово находится в регистре 10, откуда оно записывается в накопители 5 и 6 по адресу, заданному в регистре 1 после дешифрации его на дешифраторах 3 и 4.Запись в накопители 5 и 6 производится по сигналу блока 25. Затем производится считывание слов с накопителей 5 и 6 на регистры 7 и 8, откуда слова поступают на схему 19 сравнения. Результаты сравнения фиксируются триггерами 20 и 21, состояния которых записываются в дополнительные разряды накопителей 5 и 6. 1ЕСЛИ при этом .триггер 20 находита триггер 21 в одновременно с этим по сигналу выхода сумматора 22 исходное слово с регистра 10 через коммутатор 23 записывается в ту же ячейку накопителя 5. Накопитель 6 остается без изменений. Затем устройство готово к записи следующего слова. Пример записи в накопители 5 и 6 исходного слова lOlllOlO, при наличии отказов в четвертом и шестом разрядах накопителей 5 и 6, и коррекции считываемой информации приведён в табл.2. Достоверность хранимой в предложенном устройстве информации, по сравнению с известным выше, поскольку вероятность неисправления ошибок (отказов) при использовании разбивания коммутатором 23 слова на несколько частей и перестановки их местами практически равняется нулю. Быстродействие предложенного устройства определяется быстродействием дешифратора 24. Если в качестве дешифратора 24 применяется комбинационная схема сравнения, то при считывании информации быстродействие предложенного устройства в три раза выше, -чем известного. Таким образом, технико-экономические преимущества предложенного устройства заключаются в его более высоких быстродействии и надежности.

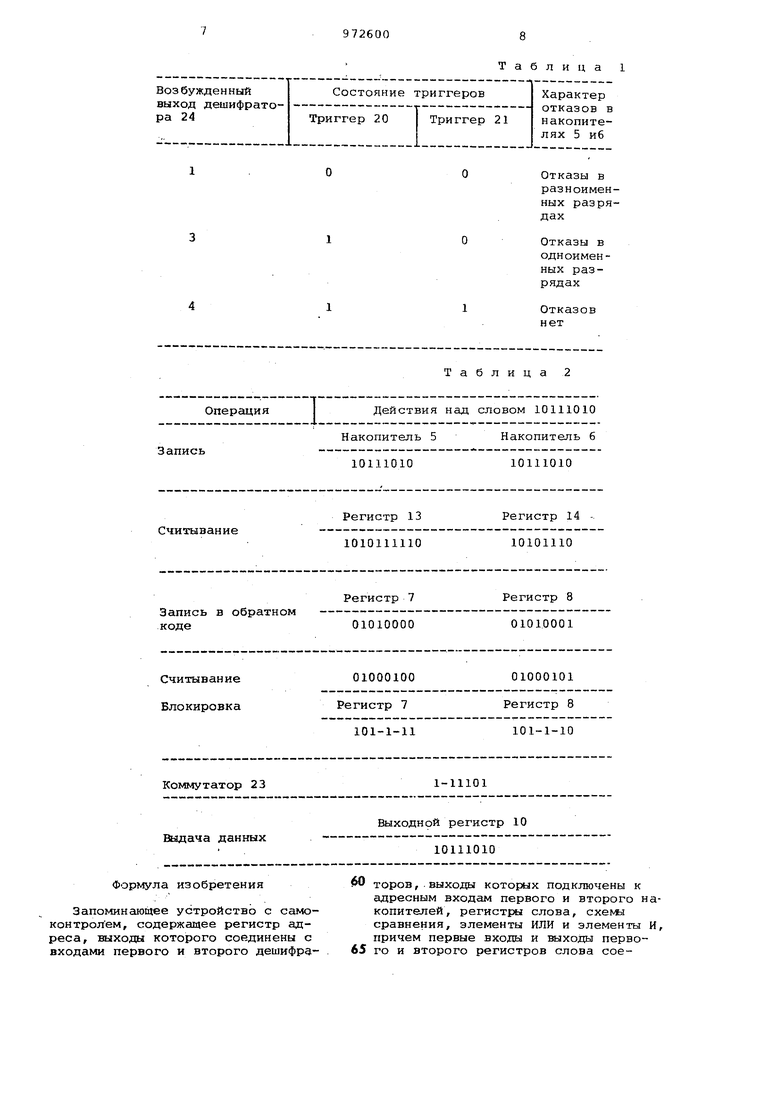

Состояние триггеров тоТриггер 20

Таблица

Характер отказов в

Триггер 21 накопителях 5 иб

Отказы в разноименных разрядах

Отказы в одноименных разрядах

Отказов нет

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1988 |

|

SU1531175A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1361624A2 |

| Постоянное запоминающее устройство | 1977 |

|

SU834768A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1374284A1 |

| Ассоциативное запоминающее устройство | 1972 |

|

SU477463A1 |

| Запоминающее устройство с коррекцией ошибок | 1987 |

|

SU1444898A1 |

| Устройство для кодирования и декодирования с исправлением ошибок | 1976 |

|

SU684547A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1164789A1 |

| Устройство для контроля постоянной памяти | 1979 |

|

SU824316A1 |

| Устройство для исправления ошибокВ блОКЕ пАМяТи | 1979 |

|

SU842976A1 |

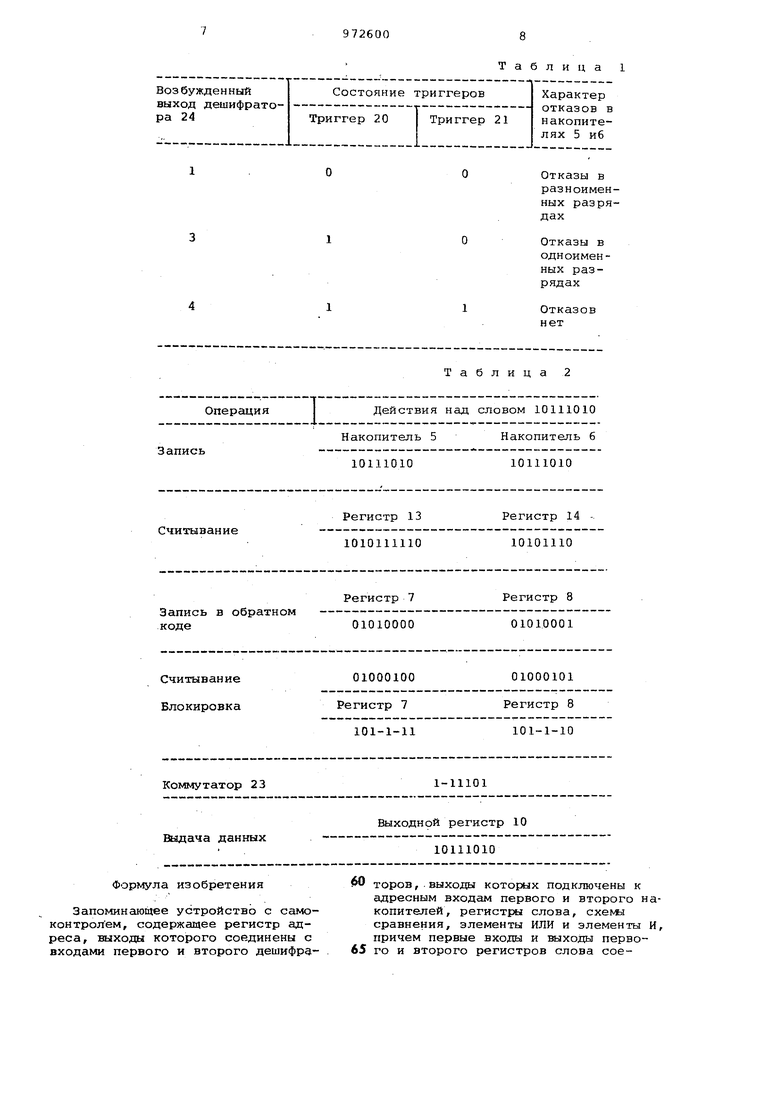

IДействия над словом 10111010

Накопитель 5Накопитель 6

Регистр 13 Регистр 14

101011111010101110

Регистр 7Регистр 8

м

0101000001010001

0100010001000101

Регистр 7Регистр 8

1-11101

Формула изобретения

Запоминающее устройство с самоконтролем, содержащее регистр адреса, выходы которого соединены с входами первого и второго дешифраТаблица 2

1011101010111010

101-1-11101-1-10

Выходной регистр 10

10111010

торов,.выходы которых подключены к адресным входам первого и второго накопителей, регистры слова, схемл сравнения, элементы ИЛИ и элементы И, причем первые входы и выходы первого и второго регистров слова соединеяы с одними из информационных выходов и входов первого ,и второго накопителей, другие информационные входы которых подключены к nepBoriy выходу третьего регистра слова, вторые выходы первого и второго регистров слова соединены соответственно с входами четвертого регистра слова и одними из входов первой схемы сравнения и с входами пятого регистра слова и одними из входов второй схемы сравнения, другие входы первой и второй схем сравнения подключены соответственно.к выходам четвертого и пятого регистров сл.ова а выходы - к первым входам первого и второго элементов И, выходы которых соединены соответственно с вторыми входами первого и: второго регистров слова, третьи выходы которых подключены соответственно к первому и к ВТОРОМУ входам третьей схемы сравнения, третий вход которой соединен с первым выходом третьего регистра слова первый вход которого подключен к вылэду элемента ИЛИ, первый вход которого соединен с четвертым выходом второго регистра слова, -управляющие входы регистра адреса, накопителей, регистров слова и вторле входы элементов И подключены к выходам блока управления, вторые вход и выход третьего регистра слова являются информационными входами и выходами устройства, о т личающееся тем,что,с целью повышения быстродействия и надежност устройства,в него введены триггеры, сумматор по модулю два, коммутатор,

третий дешифратор и формирователь контрольных сигналов, причем входы триггеров подключены к выходам третьей схемл сравнения, выход первого триггера соединен с. первыми контрольными входами накопителей и первым входом сумматора по модулю два, выход которого подключен к третьему входу третьего регистра слова а второй вход - к выходу второго триггера и вторым контрольным входам накопителей, другие информационные выходы которых подключены соотвественно к первому и ко второму входам формирователя контрольных сигналов, выход которого соединен с входом третьего дешифратора, одни из выходов которого подключены соответственно к третьим и к четвертым входам первого и в.торого регистров слова и к пятому входу первого регистра слова,шестой вход которого соединен с вторым входом элемента ИЛИ и первым выходом коммутатора, пер;вый и второй входы которого подключены соответственно .к третьему, выходу третьего регистра .слова и к четвертому, выходу первого регистра злова, второй выход коммутатора соединен с контрольным входом первого накопителя, .

. Источники информации, принятые во внимание при экспертизе

IL

ffm

Авторы

Даты

1982-11-07—Публикация

1981-04-21—Подача