Изоаретение относится к вычисли(Тельной технике.

По основному авт.св. № 91 1627 извес но запоминающее устройство с самоконтролем, содержащее накопитель,регистры числа, группы элементов ИЛИ, регистры адреса, счетчик адресов, блок контроля, блок управления, блок местного управления, коммутаторы, счетчик разрядов, а также последовательно соединенные формирователь контрольных сигналов, дешифратор и сумматор, причем выход накопителя подключен к первым входам первого, второго и четвертого регистров числа и к входу третьего регистра числа, входы накопителя соединены с выходами элементов ИЛИ, входы элементов ИЛИ первой группы подключены к вь1ходам первого регистра адреса и второго регистра адреса, вход которого соединен с выходом счетчика адресов, первый выход вторго регистра числа подключен к одним из входов второй группы элементов ИЛИ, вторые входы и выход второго регистра числа соедине.ны соответственно с выходом блока местного управления и первым входом блока контроля, второй вход которого соединен с выходом третьего регистра числа, выходы блока управления подключены к управляющим входам накопителя, регистров адреса, счетчика адресов, регистров числа блока контроля, блока местного управления и коммутаторов, второй вход четвер-. того регистра числа подключен к выходам первого коммутатора, а выходы - к другим входам элементов ИЛИ второй группы и первому входу второго коммутатора,выход которого соединен с вторым входом первого регистра числа, выход которого подключен к первому входу nepfeoro коммутатора, вторые и третьи входы первого и второго коммутаторов соеднены соответственно с первыми выходам блока контроля и счетчика разрядов, вторые выходы которых подключены соответственно к входам счетчика разрядов и блока управления, входы формирова теля контрольных сигналов подключены соответственно к выходам первого, второго и четвертого регистров числа, а выход подкл дачен к одним из входов элементов ИЛИ второй группы, выход дешифратора соединен с третьим входом блока

контроля, вход сумматора подключен к выходу второго регистра числа, а выход - к входам первого и четвертого регистров числа р , 5 В этом устройстве при последовательной записи линейного участка программы или массива чисел данные, подлежащие записи в отказавшие разряды ячеек, компануются на oтдeль

o ном регистре в слово и записываются в резервную I ячейку. При считывании программь или массива чисел вместо значений отказавших разрядов используются их истинные значения,

5 содержащиеся в резервной ячейке. Однако, если после записи программы или массива чисел появляется еще отказавшие разряды, то разряды резервной ячейки могут быть вставлены в места отказавших разрядов неверно. Это происходит в том случае, если появился отказ, значение которого совпадает со значением., соответствующего разряда хранимой кодовой комбинации. В 50% случаев такие отказы приводят к нарушению работоспособности устройства.

Таким образом, недостатком этого устройства является низкая надежность.,

Q Цель изобретения - повьш1ение надежности устройс тва.

Поставленная цель достигается тем, что в запоминающее устройство с самоконтролем введены блок свертки, блок анализа ошибок, группа элементов И, причем входы блока свертки

подключены к одним из выходов регистров числа, а выход соединен с одним из входов элементов ИЛИ второй группы и первым входом блока анализа ошибок, второй вход которого соединен с выходом формирователя контрольных сигналов, а третий вход - с другим выходом второго регистра числа, первый выход блока анализа .

ошибок подключен к первым входам элементов И группы, вторые входы которых соединены с выходами дешифратора, а выходы - с одними из входов первого регистра числа, второй

0 и третий выходы блока анализа ошибок соединены с четвертым и пятым входами блока контроля, один из выходов которого соединен с входом формирователя контрольных сигналов, четвертый выход блока контроля является контрольным выходом устройства.

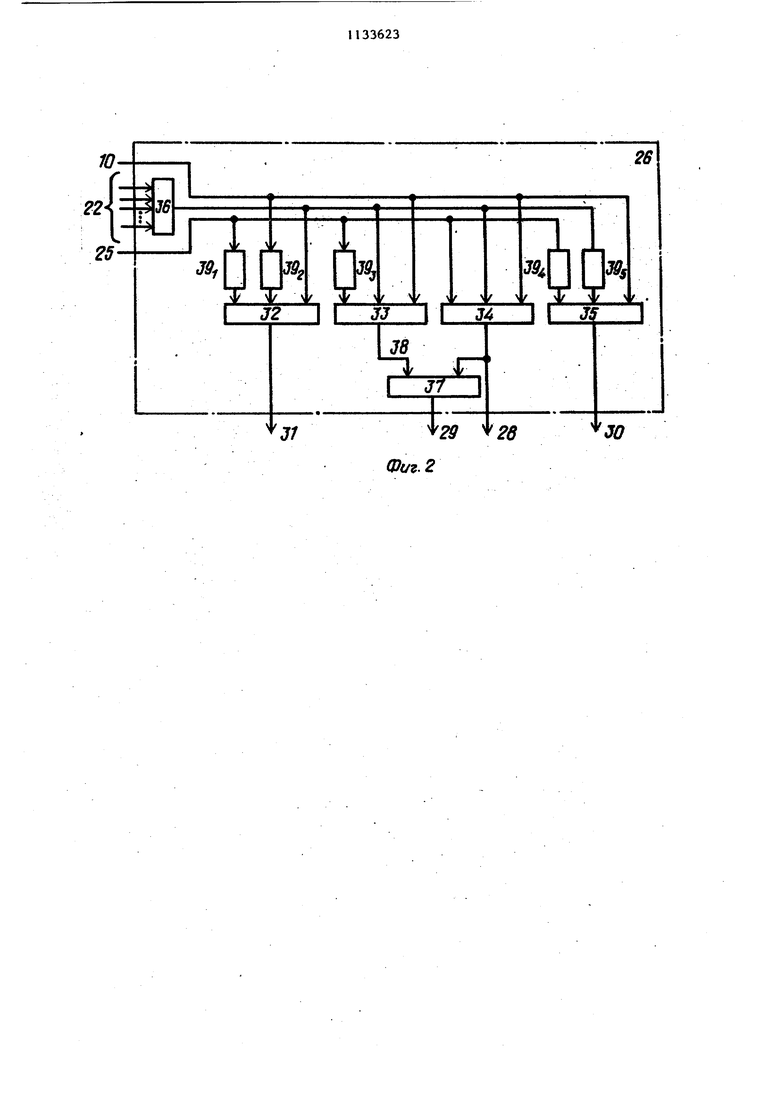

Блок анализа содержит элементы И с первого по четвертый, первый и второй элементы ИЛИ и элементы НЕ с первого по пятый, причем первые входы первого, второго и четвертого элементов И подключены соответственно к выходам первого, третьего и четвертого элементов НЕ,вторые входы первого и четвертого элементов И соеди нены соответственно с выходами второго и пятого элементов НЕ, вгыходы второго и третьего элементов И подключены к входам второго элемента ИЛИ, вькод которого и выходы первого, третьего и четвертого элементов И являются выходами блока, входы первого,третье го и четвертого элементов НЕ и первы вход третьего элемента И являются перзым входом блока, третий вход первого элемента И, вторые входы второго и третьего элементов И и вход пятого элемента НЕ подключены к выходу первого элемента ИЛИ,входы которого являются вторым входом Iблока, вход второго элемента НЕ и iтретьи входы второго,третьего и чет .вертого элементов И являются третьим входом блока. Блок контроля содержит регистр сдвига, группу элементов НЕ, элемент ШШ-НЕ и блоки сравнения, причем выходы элементов НЕ группы соединены с одними из входов блоков сравнения первые выходы которых соединены с входами элемента ИЛИ-НЕ, вторые выходы - с входами регистра сдвига, выход которого, выход элемента ИЛИНЕ и третьи выходы блоков сравнения являются выходами блока, входами которого являются вхбды элементов НЕ группы и другие входа блоков сравне ния. На фиг. 1 представлена структурна схема предложенного устройства; на фиг. 2 - функциональная схема блока анализа; на фиг. 3 - один из возмож ных вариантов блока контроля. Устройство содержит накопитель 1 имеющий вход 2, первую группу элементов ИЛИ 3, первый 4 и второй 5 регистры адреса, регистр 4 имеет вход 6, счетчик 7 адресов. К выхода 8 накопителя I подключены первые входы первого регистра 9 числа, вто рого регистра 10 числа, вход третье го регистра 1 числа и первый вход четвертого регистра 12 числа. Устройство содержит также вторую группу элементов ИЛИ 13, блок 14, контроля, первый 15 и второй 16 коммутаторы, счетчик 17 разрядов, блок 18 управления, блок 19 местног 1 3 управления-, вход 20 и выход 21 устройства, формирователь 22 контрольных сигналов, дешифратор 23, сумматор 24, представляющий собой группу сумматоров по модулю два, блок 25 свертки, блок 26 анализа, группу элементов И 27. Блок 26 анализа имеет выходы 28-31 с первого по четвертый.. Блок 26 анализа(фиг. 2 содержит первый 32, второй 33, третий 34 и четвертый 35 элементы И, первый 36 и второй 37 элементы ИЛИ, последний имеет вход 38. Устройство также содержит элементы НЕ 39,ЗЭс с первого по пятый. Блок 14 контроля(фиг. З)содержит регистр 40 сдвига, группу злементов НЕ 41, элемент ИЖ-НЕ 42 и блоки 43(- 4ЗУ сравнения (где к - разрядность хранимого в накопителе слова). Каждый блок 43 содержит сумматор 44 по модулю два, элементы И 45-50 и элементы ИЛИ 51 и 52. Устройство работает следующим образом. В исходном состоянии счетчик 17 обнулен. Для каждого линейного участка программы или для массива чисел, которые записываются и считывается последовательно, выделяются резервные ячейки накопителя i. В счетчик 7 при этом записывается адрес первой резервной ячейки, а на вход 6 регистра 4 поступает адрес первой ячейки записываемого или считываемого массива чисел. При записи число через вход 20 поступает в регистр 9, и содержимое регистра 4 через элементы ИЛИ 3 подается на вход накопителя 1. Обратный код из регистра 9 через элементы ИЛИ 13 записывается в ячейки накопителя. 1. Затем содержимое ячейки считывается на регистр И. После этого производится запись-считывание прямого кода числа на регистр 10. Причем при записи прямого кода одновременно с информационными разрядами записываются контрольные разряды корректирующего кода с расстоянием три, которые вырабатываются формирователем 22 и через элементы ИЛИ 13 поступают в накопитель I. Кроме того, с помощью блока 25 формируется дополнительный контрольный разряд, представляющий сумму по модулю два всех информационных и контрольных разрядов. Этот дополнительный контрольный ;разряд также одновременно с записью прямого кода числа через элементы ИЛИ 13 записьшается в накопитель 1, Для формирования дополнительного контрольного разряда достаточно иметь лишь информационные разряды, которые поступают на вход блока 25 из регистра 9. После записи-считывания прямого кода содержимое регистров 10 и 11 подается на блок 14. В случае, если отказавших разрядов в ячейке нет, то в регистр 4 подается следующий адрес, и аналогично производится запись второго числа. Если же в ячейке есть отказавшие разряды, то блок 14 и счетчик 17 вьщают на ком мутатор 15 сигналы по которым из регистра 9 в младшие разряды регист ра 12 передаются разряды числа, соот ветствующие отказавшим разрядам ячейки. Затем из блока 14 в счетчик 17 записьшается код, соответствующий количеству отказавших разрядов ячейки. Из блока 18 управления в блок 19 поступает сигнал, по которому в маркерный разряд ячейки накопителя через регистр 10 записьшается код 1. Одновременно код из блока 14, имеющий 1 в тех разрядах,которые отказали, поступает в формирователь 22, и полученные контрольньте разряды корректирующего кода записьшаются на место ранее записанных контрольны разрядов. Кроме того, из регистра 10 на вход блока 25 подается результат считывания прямоте .кода, и формирует ся дополнительный контрольный, разряд заносимый на место ранее записанного Аналогично производится запись числа во вторую отказавшую ячейку, только соответствующие разряды регистра 9 записываются в следующие младшие незанятые разряды регистра. 12. После того, как все разряды регистра 12 заполняются, счетчик разрядов вьщает сигнал заполнения в блок 18. Адрес резервной ячейки из счетчика 7 поступает ла регистр 5 адреса и через элементы ИЛИ 3 на вход 2 накопителя 1. Содержимое регистра 12 через элементы ИЛИ 13 записывается в первую резервную ячейку массива чисел. Одновременно в эту же ячейку записываются контрольные разряды корректирующего кода з формировател 22)и дополнительный контрольный разряд (из блока 25). После этого по сигналу из блока 18 в счетчике 7 1 3 формируется адрес следующей резервной ячейки. Чтение информации производится следующим образом. В регистр 4 по входу 6 подается адрес первой ячейки считываемого массива чисел, а в счетчик 7 записывается адрес первой резервной ячейки чисел. Счетчик 17 при этом находится в нулевом состоянии. По сигналу из блока 18 производится передача содержимого счетчика 7 через регистр 5 и элементы ИЛИ 3 на вход 2 накопителя 1. Производится чтение числа из первой резервной ячейки на регистр 10, из, которого число поступает в формирователь 22 И блок 25, где проверяется выполнение контрольных соотношений корректирующего кода. . При двойной ошибке по ненулевому синдрому с формирователя 22 и нулевому сигналу с блока 25 блок 26 анализа выдает сигнал о наличии некорректируемой ошибки на выход 31. При одиночной ошибке формирователь 22 вырабатывает также ненулевой синдром,а блок 25 - единичный сигнал. Синдром поступает на дешифратор 23, который управляет работой.сут матора 24. Скорректированное число поступает в регистр 12. Затем из регистра 4 поступает адрес первой ячейки считьшаемого массива чисел, и произврдится чтение на регистры 9 и 10. Если в маркерном разряде код О, то, следовательно, до записи числа в ячейке не было отказавших разрядов. Число из регистра 10 поступает в формирователь 22 и блок 25, и с помощью дешифратора 23 и сумматора 24 корректируется разряд , который мог отказать после записи числа в ячейку. После этого скорректированное число записывается в регистр 9, а затем поступает на выход 21. При возникновении двойной ошибки, как и при считывании слова из резервной ячейки, в блоке 26 анализа вырабатьшается сигнал наличия некорректируемой ошибки. Наличие кода 1 в маркерном разряде означает, что до записи числа в ячейке бьши отказавшие разряды. В этом случае производится запись и считывание на регистр 11 обратного кода числа. Содержимое регистров 10 и 11 поступает на входы блока 14, который выдает на формирователь 22 код, содержащий г в разрядах, соотг ветствующих отказавшим. Одновременно из регистра 10 на вход формирователя 22 поступают контрольные разряды корректирукщего кода, а на блок 25 информационные разряды. Далее возможно следующее. Пер вый случай. После записи данных в ячейке не было отказов. При этом с выхода блока 25 в блок 26 анализа поступает нулевой сигнал, формирова тель 22 вырабатывает нулевой синдром и на третьем выходе 30 блока 26 анализа формируется единичный сигнал, который поступает на вход блок 14. По сигналам из блока 14 и-счетч ка 17 через второй коммутатор 16 производится передача необходимого числа младших разрядов регистра 12 в регистр 9. После подмены тех разрядов ячейки, которые отказали до записи числа, содержимое регистра 9 поступает на вход 21. В счетчик 17 разрядов записывается код, соответствующий количеству использованных разрядов регистра 12. Если все разр ды регистра 12 будут использованы, на что указывает соответствующее состояние счетчика 17, то по сигнал из блока 18 управления в счетчике 7 формируется адрес следующей резервной ячейки. Содержимое резервной ячейки считьшается на регистр 10, корректируется и передается на регистр 12. Далее аналогично продол жается считывание массива чисел. Второй случай. После записи данных в ячейке появился один отказ, значение которого совпадает со значением соответствуницего разряда хранимой кодовой комбинации. При этом с выхода блока 23 в блок 26 анализа поступает нулевой сигнал, а с формирователя 22 ненулевой синд ром. На выходе 29 блока 26 анализа формируется единичный сигнал, котор поступает на вход блока 14. На соот ветствующем выходе дещифратора 23 появляется единичный сигнал, которы поступает на вход блока 14. По сигн лам из блока 14 и счетчика 17 через второй коммутатор 16 производится передача необходимого числа соответствующих разрядов регистра 12 в регистр 9. Причем в разряд, который ;отказал после записи числа,не передается информация с регистра 12. РазФядами резервной ячейки подменяются только те разряды ячейки, которые отказали до записи числа. После этого число из регистра 9 поступает на выход 21. В счетчик 17 записывается код, соответствующий количеству использованньк разрядов регистра 12. Третий случай. После записи данных в ячейке появился один отказ, значение которого не совпадает со значением соответствующего разряда хранимой кодовой комбинации. Блок 25 вьщает в блок 26 анализа единичный сигнал, а с формирователя 22 вьщается ненулевой синдром. На соответствующем выходе дешифратора 23 появляется единичный сигнал. На втором 29 и первом 28 выходах блока 26 анализа тпкже появляются единичные сигналы. По сигналам с выхода дешифратора 23 и с первого выхода 28 блока 26 анализа .через элементы И 27 инвертируется соответствующий разряд регистра 9, который отказал после записи данных и не совпадает со значением. : записанной информации. Аналогично как и во втором случае через второй коьжутатор 16 производится передача необходимого числа соответствукщих разрядов регистра 12 в регистр 9. Разрядами резервной ячейки подменяются только те разряды ячейки, которые отказали до записи числа. После этого число из регистр 9 поступает на выход 21. В счетчик 17 записывается кед, соответствующий количеству использованных разрядов регистра . 12.. Предложенное устройство, таким образом, в случае появления отказа после записи числа полностью сохраняет работоспособность,в то время как известное неработоспособно в 50% случаев.Следовательно,предлагаемое устройство имеет повышенную надежность.

Hi

Ю3622 25

3Qi

26

I f f f

I J2 I i JJ IT J4 I I J

J/

7 I

i

JO

29

26

Фиг. 2

О т 16 232930 10 П

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1980 |

|

SU911627A2 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU963109A2 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU888214A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1152044A2 |

| Запоминающее устройство с самоконтролем | 1979 |

|

SU883975A2 |

| Запоминающее устройство с самоконтролем | 1978 |

|

SU748515A1 |

| Резервированное запоминающее устройство | 1987 |

|

SU1513526A1 |

| Оперативное запоминающее устройство с блокировкой неисправных ячеек памяти | 1981 |

|

SU1014033A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU943843A1 |

| Устройство для записи информации в запоминающее устройство | 1980 |

|

SU951399A1 |

1. ЗАПОМЩАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ по авт.св. № 911627, . отличающееся тем, что, с целью повышения надежности устройства, в него введены блок свертки, блок анализа ошибок, группа элементов И, причем входы блока свертки подключены к одним из выходов регистров числа, а выход соединен с одним из входов элементов ИЛИ второй группы и первым входом блока анализа ошибок, второй вход которЬго соединен с выходом формирователя контрольных сигналов, третий вход - с другим выходом второго регистра числа, первый выход блока анализа ошибок соединен с первы ми входами элементов И группы,вторые входы которых соединены с выходами дешифратора, а выходы - с одними из входов первого регистра числа, второй и третий выходы блока анализа ошибок соединены с четвертым и пятым входами блока контроля, один из выходов которого соединен с входом формирователя контрольных сигналов, четвертый выход блока контроля является контрольным выходом устройства. 2. Устройство по п. 1, о т л ичающееся тем, что блок анализа содержит элементы И с первого по четвертый, первый и второй элементы ИЛИ и элементы НЕ с первого по.пятый, причем первые входы первого, второго и четвертого элементов И подключены соответственно к выходам первого, третьего и четвертого элементов НЕ, вторые входы первого и четвертого элементов И соединены соответственно с выходами второго и пятого элементов НЕ, выходы второго и третьего элементов И подключены к входам .второго элемента ИЛИ, выход которого и выходы первого, третьего и четверг того элементов И являются выходами блока, входы первого, третьего и четвертого элементов НЕ и первый вход третьего элемента И являются первым входом блока, третий вход (Л первого элемента И, вторые входы второго и третьего элементов И и вход пятого элемента НЕ подключены к выходу первого элемента ИЛИ, входы которого являются вторым входом блока, вход второго элемента НЕ и третьи входы второго, третьего и четвертого, :о :о элементов И являются третьим входом блока. 3. Устройство по п. 1, отли .чающееся тем, что блок конт О роля содержит регистр сдвига, группу э элементов НЕ, элемент ИЛИ-НЕ и блоки сравнения, причем выходы элементов НЕ группы соединены с одними из входов . блоков сравнения,первые выходы которых соединены с входами элемента ИЛИ-НЕ, вторые выходы - с входами регистра сдвига, выход которого, вы ход элемента ИЛИ-НЕ и третьи выходы блоков сравнения являются вь1 ходами блока, входами которого являются входы элементов НЕ группы и другие входы блоков сраьЛния.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU911627A2 |

| Солесос | 1922 |

|

SU29A1 |

Авторы

Даты

1985-01-07—Публикация

1983-09-14—Подача