(54) КОММУТАТОР Изобретение относится к вычислительной технике и может быть использовано для построения параллельных коммутационных устройств в универсальных вычислительных системах и структурс1х высокой производительности . Известны в вычислительных структурах и системах коммутаторы, которые могут быть использованы для перестраиваемых цифровых устройств с программным управлением 1. Обычно в таких устройствах время настройки и перестройки на решение конкретной задачи зависит от сложное ти коммутатора и числа элементов в нем. Оно резко возрастает при увеличении числа настраиваемых коммутацио ных элементов в системе. Известен также коммутатор, содержащий матрицу из MN электронных искателей-разъединителей, а также М эл ментов ИЛИ строки, выход каждого из которых соединен с информационными выходами электронных искателей-разъе динителей строки и соответствующей горизонтальной выходной информационной шиной коммутатора, один из входов элемента ИЛИ строки подключен к соответствующей шине управления, а

В П Т 6

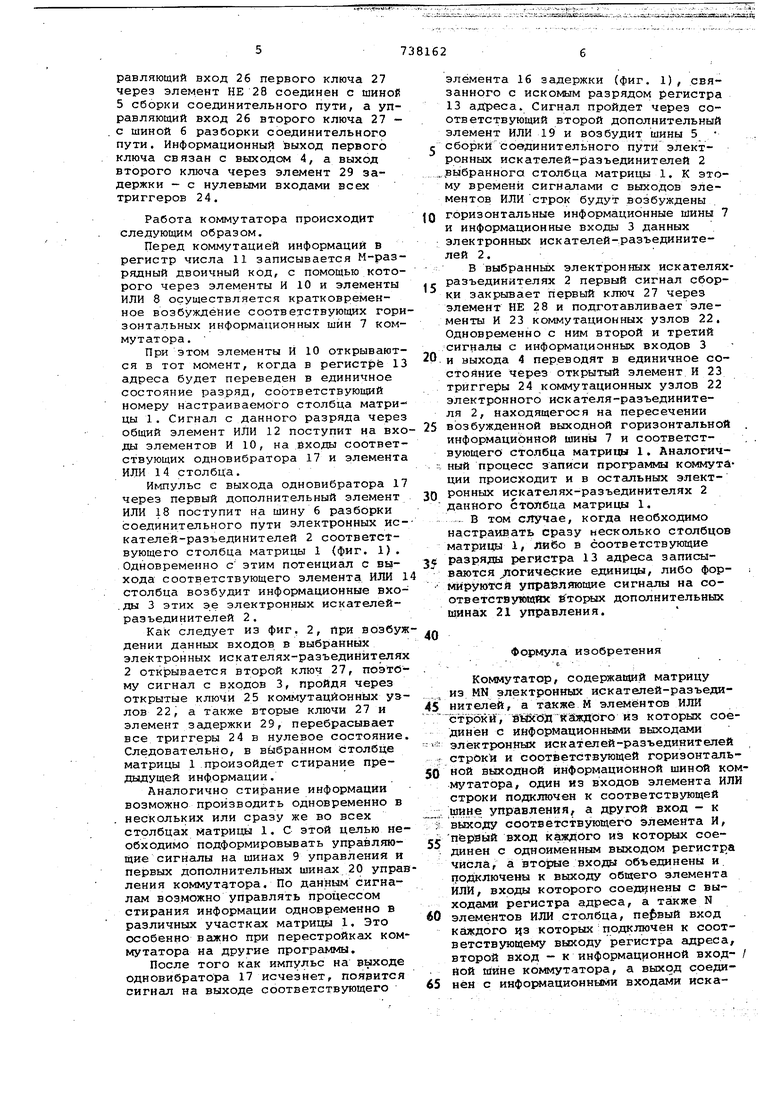

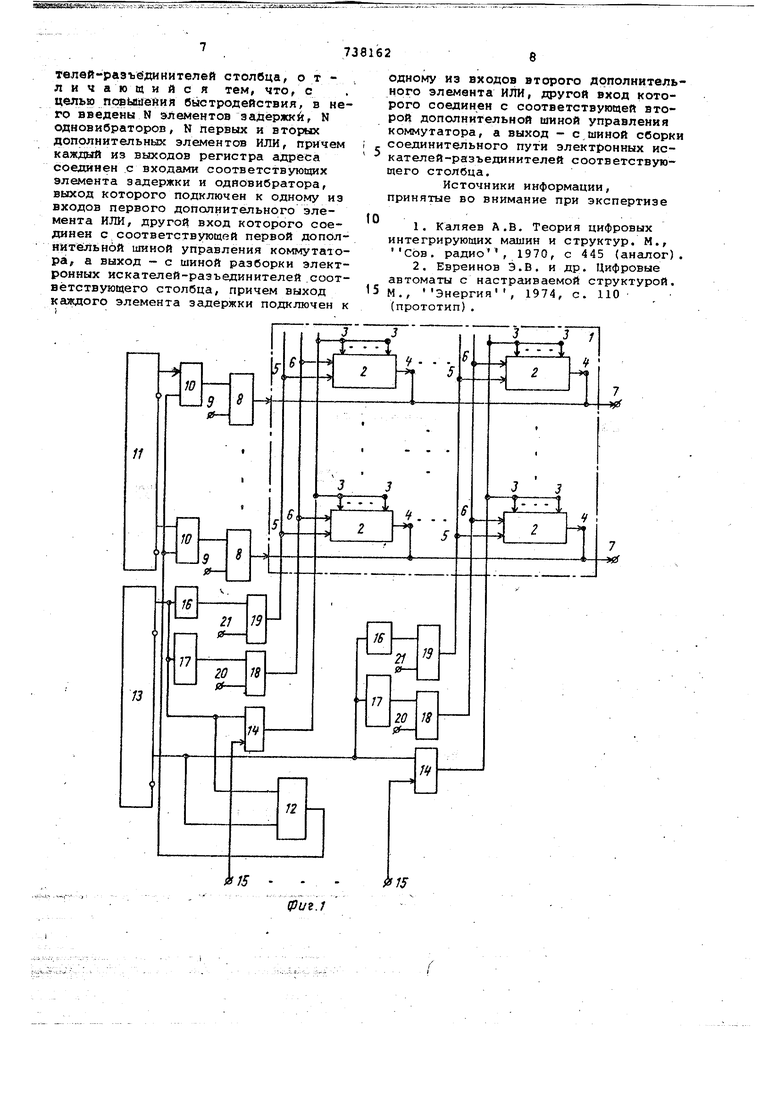

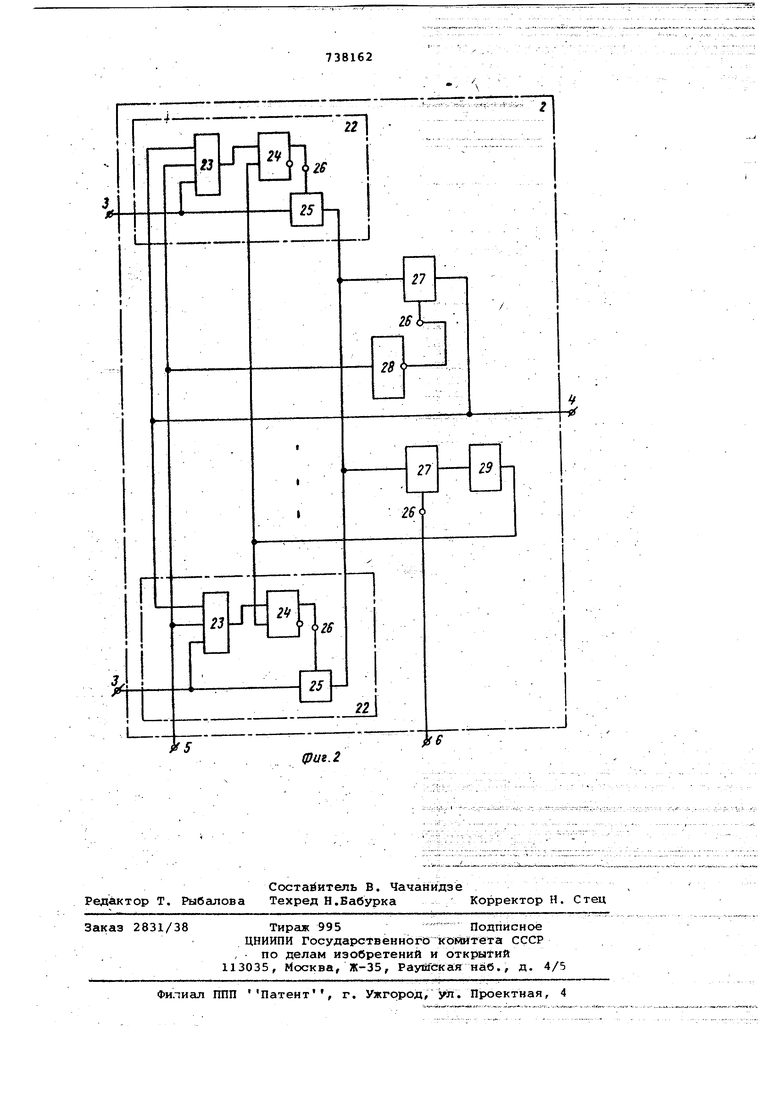

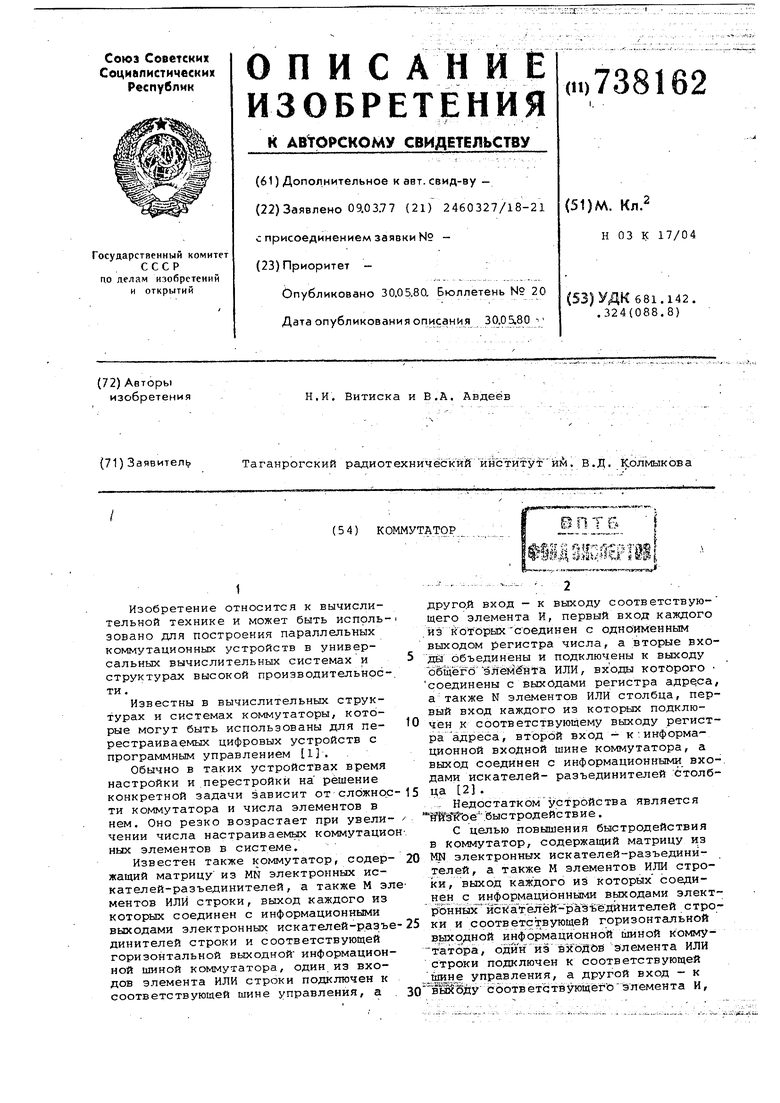

r 7v 7r -atp ДРУГО.Й вход - к выходу соответствующего элемента И, первый вход каждого из соединен с одноименным выходом регистра числа, а вторые объединены и подключены к выходу oBiiiefб ёлёЙёйГа или, входы которого соединены с выходами регистра адреса, атакже N элементов ИЛИ столбца, первый вход каждого из которых подключен ,к соответствующему выходу регистра адреса, второй вход - к .информационной входной шине коммутатора, а выход соединен с информационными вхо-, дами искателей- разъединителей Столбца 2 . . : Недостаткомустройства является .быстродействие, С целью повышения быстродействия в коммутатор, содержащий матрицу из MN электронных искателей-разъединителей, а также М элементов ИЛИ строки, выход каждого из которых соединен с информационными выходами элект ЗнньйГ йсйаТел тЁедани тел ей с троки и соответс:твующей горизонтальной выходной информационной шиной Kovn yтатора, йэ Bxogufi элемента ИЛИ строки подключен к соответствующей управления, а другой вход - к вШВЙУ С оотв етс ТВ ующёго емен т а И, гзэрвый вход каждого из которых соединен с одноименным выходом регистр числа, а вторые входы объединены и подключены к выходу общего элемента ИЛИ, входы которого соединены с выходами регистра адреса, а также N элементов ИЛИ столбца, вход каждого из котораох подключен к соответствующему выходу регистра адре са, второй вход - к информационной входной.шине коммутатора, а выход соединён с информационными входами искателей-разъединителей столбца, в него введены N элементов задержки, N однрвибраторов, N первых и вторых дополнительных элементов ИЛИ, приче каждый из выходов регистра адреса соединен с входами соответствующих элемента задержки и одновибратора, выход которого подключен к одному и входов первого дополнительного элемента ИЛИ, другой вход которого сое дйнен с соответствующей первой допол нительной шиной управления коммутатора, а выход - с шиной разборки электронных искателей-разъединителе соответствующего столбца, причем вы ход каждого элемента задержки подключен к одному из входоё второго д полнительного элемента ИЛИ, другой вход которого, соединен с соответствующей второй дополнительной шиной управления коммутатора, а выход - с шиной сборки соединительного пути электронных искателей-разъединителей сботве ствующего столбца. .На фиг. 1 представлена функционал ная схема предлагаемого коммутатора на фиг. 2 - схема основного элемент коммутатора - электронного искателя разъединителя. Коммутатор (фиг. 1) содержит матрицу 1 из MN электронных -искателейразъединителей 2, в каждой из котоf sx имеется k информационных входов 3, один информацибнный выход 4, шину 5 сборки соединительного пути и шину б разборки. Информационные выходы 4 электронных искателей-разъеди нйтелей одной строки матрицы 1 объеЛЙнейы между собой и подсоединены к соотве тствующей горизонтальной выход ной информационной шине 7 коммутатоspa Всего в |соммутаторе имеется м ВЕЛходных информационных шин, причем каждая такая шина подсоединена также к сбответсТВуйщему выходу одного из М элементов ИЛИ 8 строки. Один из ьхолов элемента ИЛИ 8 стрбкй ШДкйючей к одной из соответствующих шин 9 управления ксз1у 1утатора, а другой )вх6я - к выходу одного из соответствующих элементов И 10. Перрый вход ( каждого из них соединен с одноименным вьоходом регистра 11 числа, а вто рые их входы объединены и подключены к выходу общего элемента ИЛИ 12 коммутатора. Входы общего элемента или 12 соединены с выходами регистра 13 адреса, В коммутаторе имеется также N элементов ИЛИ 14 столбца, первый вход каждого из которых подключен к соответствующему выходу регистра 13 сшреса, второй вход - к информационной входной шине 15 коммутатора, в котором имеется всего N информационных входных .шин. Выход каждого из элементов ИЛИ 14 столбца в каждом столбце матрицы 1 соединен с соответствующими информационными входами 3 электронных искателей-разъединителей 2 , Для управления коммутатор содержит N элементов 16 задержки, N одновибраторов .17, N первых дополнительных элементов ИЛИ 18 и N вторых дополнительных элементов ИЛИ 19. Каждый из выходов регистра 13 адреса соединен с входами соответствующих элементов 16 задержки и одновибраторй 17, выход которого подключен к одному из входов первого дополнительного элемента ИЛИ 18, другой вход которого соединен ссоответствующей первой дополнительной шиной 20 управления коммутатора. Вс,его имеется N, первых дополнительных шин 20 управления коммутатора. Выход каждого первого дополнительного элемента ИЛИ 18 связан с соответствующей шиной б разборки злект- . ронных искателей-разъединителей 2 столбца матрицы 1. Причем выходкаждого элемента задержки 16 подключен к одному из входов второго дополнительного элемента ИЛИ 19, другой вход которого соединен с соответствующей второй дополнительной шиной управления 21 (всего N шин 21) коммутатора, а выход - с шиной сборки соединительного пути 5 электронных искателей-разъединителей 2 соответствующего столбца, матрицы 1 коммутатора. Показанная на фиг. 2 схема электронного искателя-разъединителя 2 содержит k коммутационных узлов 22, каждый из которых трехвходовый элемент И 23, триггер 24 и ключ 25. Информационные входы 3 электронного искателя-разъединителя 2 соединены одновременно с информационным входом ключа 25 и первым входом эл.емента И 23, второй вход которого подсоединен к информационному выходу 4, а третий шине 5 сборки соединит ельного пути. ; Выход элемента И 23 соединен с единичным входе триггера 24, единичный выход которого связан с- управлян щим входом .26 ключа 25 коммутационного узла 22, , Электронный искатель-разъединитель 2 содержит также два ключа 27, информационные входы KOTOJXJX соединены с объединенными выходами клю чей 25 коммутационных узлов 22, Управляющий вход 26 первого ключа 27 через элемент НЕ 28 соединен с шиной 5 сборки соединительного пути, а управляющий вход 26 второго ключа 27 с шиной 6 разборки соединительного пути. Информационный выход первого ключа связан с выходом 4, а выход второго ключа через элемент 29 задержки - с нулевыми входами всех триггеров 24.

Работа коммутатора происходит следующим образом.

Перед коммутацией информации в регистр числа 11 записывается М-разрядный двоичный код, с помощью которого через элементы И 10 и элементы ИЛИ 8 осуществляется кратковременное возбуждение соответствующих горизонтальных информационных шин 7 коммутатора.

При этом элементы И 10 открываются в тот момент, когда в регистре 13 адреса будет переведен в единичное состояние разряд, соответствующий номеру настраиваемого столбца матрицы 1. Сигнал с данного разряда через общий элемент ИЛИ 12 поступит на входы элементов И 10, на входы соответствующих одновибратора 17 и элемента ИЛИ 14 столбца.

Импульс с выхода одновибратора 17 через первый дополнительный элемент ИЛИ 18 поступит на шину 6 разборки соединительного пути электронных искателей-разъединителей 2 соответствующего столбца матрицы 1 (фиг. 1) . Одновременно с этим потенциал с выхода соответствующего элемента ИЛИ 1 столбца возбудит информационные вхо.ды 3 этих эе электронных искателейразъединителей 2.

Как следует из фиг, 2, при возбуждении данных входов в выбранных электронных искателях-разъединителях 2 открывается второй ключ 27, поэтбму сигнал с входов 3, пройдя через открытые ключи 25 коммутационных узлов 22, а также вторые ключи 27 и элемент задержки 29, перебрасывает все триггеры 24 в нулевое состояние. Следовательно, в выбранном столбце матрицы 1 произойдет стирание предыдущей информации.

Аналогично стирание информации возможно производить одновременно в нескольких или сразу же во всех столбцах матрицы 1, С этой целью необходимо подФормировывать управляющие сигналы на шинах 9 управления и первых дополнительных шинах 20 управления коммутатора. По данным сигналам возможно управлять процессом стирания информации одновременно в различных участках матрицы 1. Это особенно важно при перестройках коммутатора на другие программы.

После того как импульс на выходе одновибратора 17 исчезнет, появится сигнал на выходе соответствующего

738162

элемента 16 задержки (фиг. 1), связанного с искомым разрядом регистра 13 адреса. Сигнал пройдет через соответствующий второй дополнительный элемент ИЛИ 19 и возбудит шины 5 сборки соединительного пути электронных искателей-разъединителей 2 .рыбраннога столбца матрицы 1. к этому времени сигналами с выходов элементов ИЛИ строк будут возбуждены горизонтальные информационные шины 7

0 и информационные входы 3 данных электронных искателей-разъединителей 2.

В выбранных электронных искателяхразъединителях 2 первый сигнал сбор5ки закрывает первый ключ 27 через элемент НЕ 28 и подготавливает элементы И 23 коммутационных узлов 22. Одновременно с ним второй и третий сигналы с информационных входов 3

0 и выхода 4 переводят в единичное состояние через открытый элемент И 23 триггеры 24 коммутационных узлов 22 электронного искателя-раэъединителя 2, находящегося на пересечении

5 возбужденной выходной горизонтальной информациЬнйой шины 7 и соответствующего cfолбца матрицы 1, Аналогичный процесс записи программы коммутации происходит и в остальных электронных искателях-разъединителях 2

0 данного столбца матрищд 1.

. В том случае, когда необходимо настраивать сразу несколько столбцов матрицы 1, Либо в соответствующие разряды регистра 13 адреса записы5ваются логические единицы, либо формируются управляющие сигналы на соответствующих в торых дополнительных шинах 21 управления.

40

Формула изобретения

-. . с ,

Коммутатор, содержащий матрицу из MN электронных искателей-разъединителей, а также М элементов ИЛИ

5

строки, вьйсЪД каждого из которых соединен с информационными выходами электронных искателей-разъединителей строки и соответствующей горизонтальной выходной информационной шиной ком0мутатора, один из входов элемента ИЛИ строки подключен к соответствующей шине управления, а другой вход - к выходу соответствующего элемента И,

первый вход каждого из которвлх сое5динен с одноименным выходом регистра числа, а вторые входы объединены и. подключены к выходу общего элемента ИЛИ, входы которого соед1 нены с выходами регистра адреса, а также N

0 элементов ИЛИ столбца, первый вход каясдого 43 которых подключен к соответствующему выходу регистра адреса, второй вход - к информац 1онной вход- / ной шине коммутатора, а выход соеди5нен с инфо1 1ационными входами искателей-разъёдинителей столбца, о т личающийся тем, что, с целью првьыейия быстродействия, в него введены N элементов задержки, N одновибраторов, N первых и вторых дополнительных элементов ИЛИ, причем каждый из выходов регистра адреса соединен .с входами соответствующих элемента задержки и одновибратора, выход которого подключен к одному из входов первого допсхпнительного элемента ИЛИ, другой вход которого соединен с соответствующей первой дополнйтеяьной шиной управления коммутатора, а выход - с шиной разборки электронных искателей-разъединителей.соответствующего столбца, причем выход каждого элемента задержки подключен к

одному из входов второго дополнительного элемента ИЛИ, другой вход которого соединен с соответствующей второй дополнительной шиной управления коммутатора, а выход - с шиной сборки соединительного пути электронных искателей-разъединителей соответствующего столбца.

Источники информации, принятые во внимание при экспертизе

1.Каляев А.В. Теория цифровых интегрирующих машин и структур. М., Сов. радио , 1970, с 445 (аналог).

2.Евреинов Э.В. и др. Цифровые автоматы с настраиваемой структурой.

5м., Энергия, 1974, с. 110 (прототип).

ffS

фиг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный фотометр | 1987 |

|

SU1492224A1 |

| Устройство для оценки степени оптимальности размещения в многопроцессорных кубических циклических системах при направленной передаче информации | 2017 |

|

RU2727555C2 |

| Устройство для оптимизации работы параллельных процессов | 1988 |

|

SU1569844A1 |

| Многоканальный счетчик импульсов | 1987 |

|

SU1508342A1 |

| МНОГОКАНАЛЬНЫЙ КОММУТАТОР | 1991 |

|

RU2026605C1 |

| Устройство для сопряжения разнотипных вычислительных машин | 1986 |

|

SU1381526A2 |

| Устройство для редактирования информации | 1981 |

|

SU980099A1 |

| Микропроцессорное устройство для моделирования систем массового обслуживания | 1984 |

|

SU1196886A1 |

| Устройство для определения координат треков | 1985 |

|

SU1255976A1 |

| Устройство для подсчета минимального значения интенсивности размещения в многопроцессорных кубических циклических системах при однонаправленной передаче информации | 2018 |

|

RU2688236C1 |

Авторы

Даты

1980-05-30—Публикация

1977-03-09—Подача