(54) ДЕСЯТИЧНЫЙ СЧЕТЧИК

| название | год | авторы | номер документа |

|---|---|---|---|

| Десятичный счетчик с индикацией | 1983 |

|

SU1156254A1 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

| ДЕСЯТИЧНЫЙ СЧЕТЧИК | 1973 |

|

SU400037A1 |

| Управляемый делитель частоты | 1987 |

|

SU1522396A1 |

| Устройство для программного управления механизмами | 1986 |

|

SU1409972A1 |

| Декадный счетчик для семисегментных индикаторов | 1987 |

|

SU1451853A1 |

| Синхронный делитель частоты на 11 на @ -триггерах | 1983 |

|

SU1150759A1 |

| Многофункциональное счетное устройство | 1979 |

|

SU819969A2 |

| Синхронный делитель частоты на 9 на @ -триггерах | 1983 |

|

SU1148118A1 |

| Устройство для многоточечного контроля | 1987 |

|

SU1509966A1 |

1

Изобретение относится к вычислительной технике и может найти применение при построении дискретных счетчиков импульсов на интегральных схемах в промьпиленной электронике, на- 5 пример, в пересчетных устройствах намоточных станков .

Десятичный счетчик, содержасдай четыре JK-триггера, первый, второй и третий элементы И, установленные на Ю входах соответственно второго, третьего и четвертого триггеров, причем одни входы элементов И соединены с прямыми выходами соответственно первого, второго, третьего счетных триг-15 геров, а другой вход первого элемента И связан с инверсным выходом четвертого триггера 1.

Недостатком этого счетчика являет- . ся сравнительно низкая надежность. 20

Известен десятичный счетчик, содержащий четыре JK-триггера и три элемента И, тактовые входы JK-триггеров соединены с входом десятичногоо счетчика, J и К входы первого ак-триг25 гера соединены с единичной шиной, прямой выход первого JK-трИггера соединем с первым входом первого элемен- ; та- И, выход которого соединен о К Z взводом второго ОК-триггера, прямой 30

выход которого соединен с первым входом вTopibro.элемента И, ко:горого соединен с К входом третьего , JK-триггера и первым входом третьего элемента И, второй вход которого соединен с прямым выходом третьего JK-триггера 2.

Недостатком этого десятичного счетчика являетсяотносительно низкая надежность, так как выходы JK- нагру-жены неравномерно.

-Целью изобретения является повышение надежности.

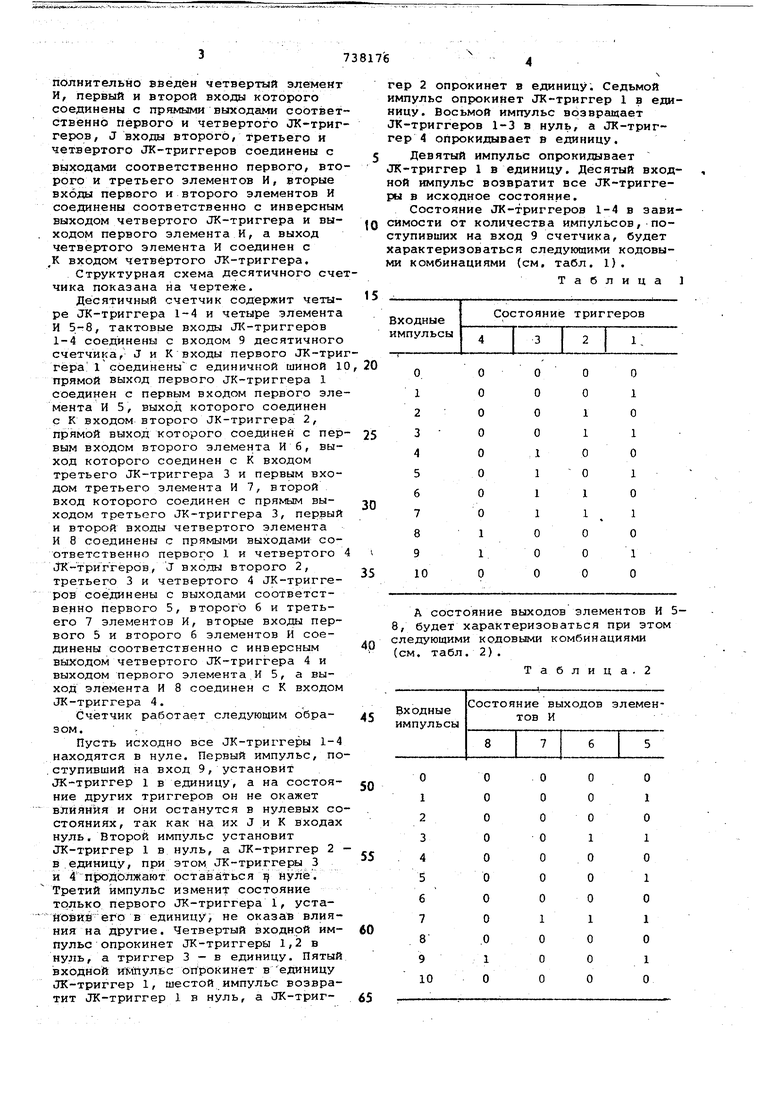

.Поставленная цель достигается тем, что в десятичный счетчик, содержащий четыре JK-триггера и три элемента И, такTOBbie входа JK-триггеров соединены с входом десятичного счетчИка, J иК выхода Нёрвого JK-триггёра соединены с единичной шиной, прямой выход первого JK-триггера соединен с LnepiBbiMвходом Tiet fiorD з лемента И, выход которого соединен с К входом вто рого JK-трйггера, прям6Й выход кото- jporo соединен с первым входом второго элемента И, выход которого соединен ;с К входом третьего JK-триггера к первым входом третьего элемента И, второй вход которого соединен с пряMbJM выходом трегьего JK-триггера, дополнительно введён четвертый элемент И, первый и второй входы которого соединены с прямытчи выходами соответственно первого и четвертого JK-триггеров, J входы второго, третьего и четвертого JK-триггеров соединены с выходами соответственно первого, второго и третьего элементов И, вторые входы первого и второго элементов И соединены соответственно с инверсным выходом четвертого JK-триггера и выходом первого элемента И, а выход четвертого элемента И соединен с К входом четвертого JK-триггера. Структурная схема десятичного счет чика показана на чертеже. Десятичный счетчик содержит четыре JK-триггера 1-4 и четыре элемента И 5-8, тактовые входы JK-триггеров 1-4 соединены с входом 9 десятичного счетчика, J и К входы первого JK-триг гера 1 соединены с единичной шиной 10 прямой выход первого JK-триггера 1 соединен с первым входом первого элемента И 5, выход которого соединен с К входом второго JK-триггера 2, прямой выход которого соединен с первым входом второго элемента И 6, выход которого соединен с К входом третьего JK-триггера 3 и первым входом третьего элемента И 7, второй вход которого соединен с прямым выходом третьего JK-триггера 3, первый и второй входы четвертого элемента И 8 соединены с прямыми выходами соответственно первого 1 и четвертого JK-триггеров, J входы второго 2, третьего 3 и четвертого 4 JK-триггеров соединены с выходами соответственно первого 5, второго б и третьего 7 элементов И, вторые входы первого 5 и второго б элементов И соединены соответственно с инверсным выходом четвертого JK-триггера 4 и выходом первого элемента И 5, а выход элемента И 8 соединен с К входом JK-триггера 4. Счетчик работает следующим образом. Пусть исходно все JK-триггеры 1-4 находятся в нуле. Первый импульс, по.ступивший на вход 9, установит JK-триггер 1 в единицу, а на состояние других триггеров он не окажет влияния и они останутся в нулевых со стояниях, так как на их J и К входах нуль. Второй импульс установит JK-триггер 1 в нуль, а JK-триггер 2 в единицу, при этом JK-триггеры 3 и 4 продолжают оставаться нуле. Третий импульс изменит состояние только первого JK-триггера 1, устайОёий его в единицу, не оказав влияния на другие. Четвертый входной импульс опрокинет JK-триггера 1,2 в нуль, а триггер 3 - в единицу. Пятый входной иг.шульс опрокинет в единицу JK-триггер 1, шестой импульс возвратит JK-триггер 1 в нуль, а JK-тригр 2 опрокинет в единицу. Седьмой пульс опрокинет JK-триггер 1 в едицу. Восьмой импульс всэзвращает -триггеров 1-3 в нуль, а JK-тригр 4 опрокидывает в единицу. Девятый импульс опрокидывает -триггер 1 в единицу. Десятый входй импульс возвратит все JK-триггев исходное состояние. Состояние JK-триггеров 1-4 в завимости от количества импульсов, поупивших на вход 9 счетчика, будет рактеризоваться следующими кодовыкомбинациями (см, табл. 1). Таблица А состояние выходов элементов И 5, будет характеризоваться при этом ледующими кодовыми комбинациями см. табл. 2). Таблица. 2 Состояние выходов элеменВходныетов И мпульсы

Таким образом, JK-триггеры 1-4 с элементгми И 5-8, производят пересчет импульсов в двоичном коде с исключением шести излишних состояний.

В десятичном счётчике прямой выход JK-триггера 1 нагружен двумя па раллельными входами элементов И 5 и 8 дополнительной логической связи, а прямой выход JK-триггера 2 - одним входом элемента и б, В результате этго общая нагрузка JK-триггера 1 и JK-триггера 2 уменьшается. В результате снижается относительный коэффициент интенсивности отказов. Это повышает надежность работы счетчика, а также его быстродействие.

Формула изобретения

Десятичный счетчик, содержащий четыре JK-триггера и три элемента И, тактовые входы JK-триггеров соединены с входом десятичного счётчика, J и К входы первого JK-триггера соединены с единичной шиной, прямой выход первого JK-триггера соединен с первым входом первого элемента И, выход которого соединен с К входом второго JK-триггера, прямой выход которого соединен с первым входом

второго элемента И, выход которого соединен с К входом третьего JK-триггера и первым входом третьего элемента И, второй вход которого соединен с прямым выходом третьего JK-триггера, о т л,и ч а ю и и и с я тем, что, с uejffera повьвиения надежности, в него дополнительно введен четвертый элемент И, первый и второй входа которого соединены с прякс ми выходами соответственно первого и четвертого

0 JK-триггеров, J входы второго, третьего и четвертого JK-триггеров соединены с выходами соответственно первого, второго и третьего элементов И, вторые входы первого и второго эле5ментов И соединены соответственно с инверсным выходом четвертого JK-триггера и вых6 ДйМперв6гЬ элемента И, а выход четвертого элемента И соединен с К входом четвёртого JK-тригге0ра.

Источники информации, принятые во внимание при экспертизе

5 с. 182, рис. 4.21 б.

Q

3, c. 127, рис V 2 (прототип).

738176

Ю

Авторы

Даты

1980-05-30—Публикация

1977-12-19—Подача