1 Изобретение относится к цифровой технике и может быть использовано, например, при построении хронизаторов, цифровых синтезаторов частоты электромузыкальных инструментов и т. Известен делитель частоты на 11, содержащий 5 Jk -триггеров ll. Недостатками данного делителя ча тоты являются его сложность, а такж то, что эта схема несинхронная. Р1аиболее близким к .предлагаемому является синхронный делитель частоты на 11 на ЛК-триггерах, работающий в коде 8-4-2-1. Известный синхронный делитель содержит четыре JK -триггера, два логических элемента И и два И-НЕ, счетные входы всехЛК-триггеров соеди нены между собой и с входной шиной устройства, входы R всех ЗК триггеров соединены между собой и с гаиной сброса устройства, J вход первого JK -триггера соединен с выходом первого элемента И-НЕ, два входа которого соединены с прямыми выходами второго и четвертого Jk триггеров соответственно, k вход первого ЗК -триггера соединен с шиной логической единицы, J вход т, второго JK -триггера соединен с Пр ,, мым выходом первого триггера, К вхо второго ЗК -триггера соединен с выходом второго элемента И-НЕ, два входа которого соединены с инверсными выходами первого и четвертого Зк-триггеров соответственно, и К входы третьего ЭК -триггера соединены с выходом первого элемента И, два входа которого соединены с прямыми вькодами первого и второго JKтриггеров соответственно, J вход четвертого Jf -триггера соединен с выходом, второго элемента И, три входа которого соединены с прямыми выходами первого, второго и третьего Jk -триггеров соответственно, К вход четвертого 3k-триггера соединен с прямьш выходом второго Зк триггера, прямой выход четвертого ЗК-триггера является выходом делителя 2 .

Недостатком известного делителя является сложность, приводящая к низкой надежно.сти и большой потребляемой мощности за счет большого количества элементов и цепей.

Цель изобретения - упрощение устройства.

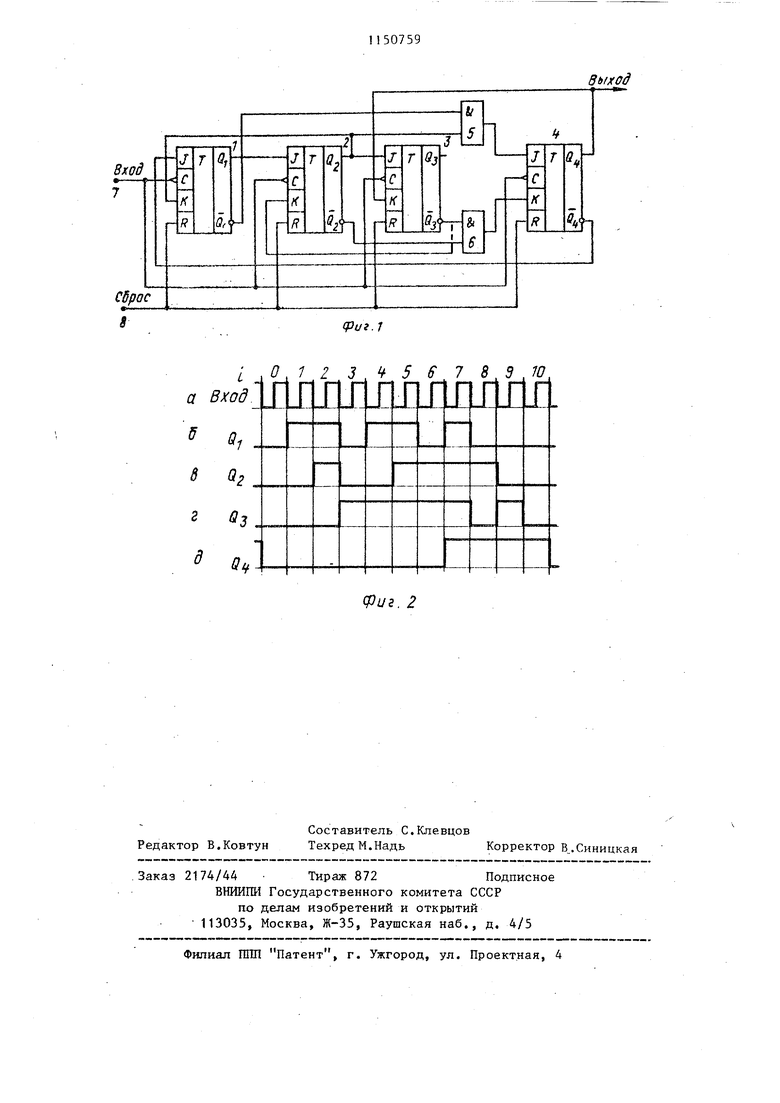

временные диаграммы устройства, где обозначено: а - входной сигнал на тактовой шине; б, в, г, д - сигнал на прямых выходах 3k -триггеров при поступлении входных импульсов с номерами i с О по 10-й.

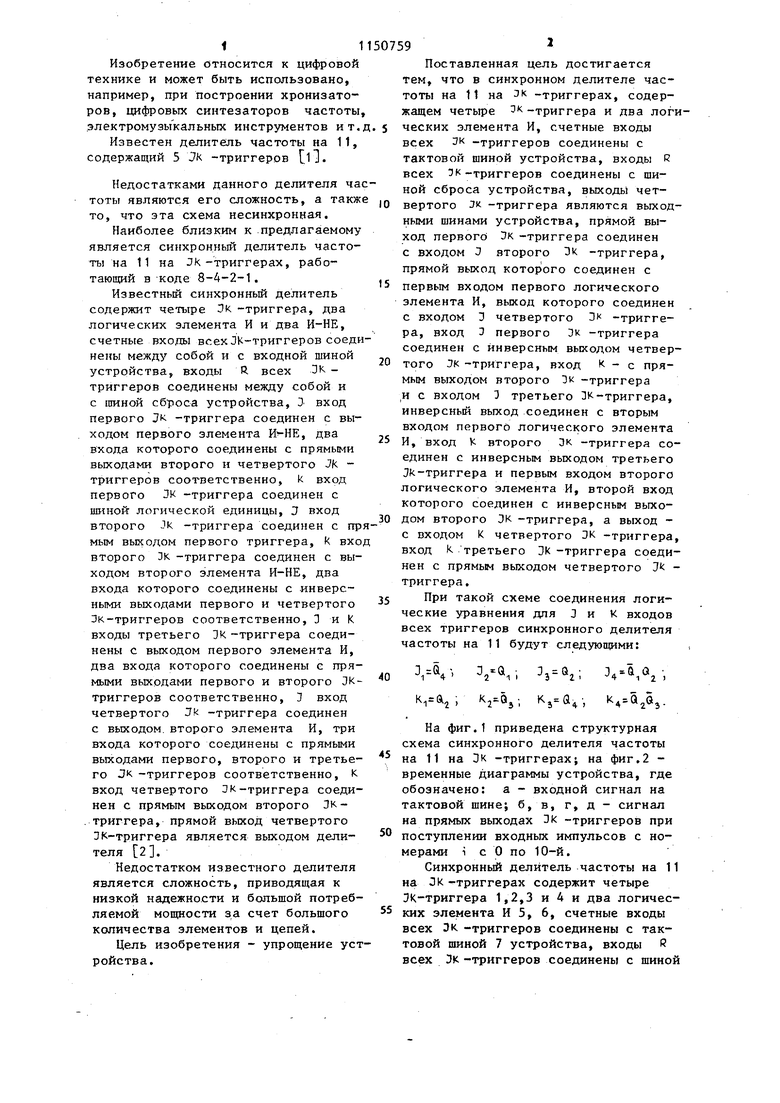

Синхронный делитель частоты на 11 на ЛК Триггерах содержит четыре ик-триггера 1,2,3 и 4 и два логических элемента И 5, 6, счетные входы всех JK -триггеров соединены с тактовой шиной 7 устройства, входы R всех DK -триггеров соединены с шиной 9 Поставленная цель достигается тем, что в синхронном делителе частоты на 11 на -триггерах, содержащем четыре -триггера и два логических элемента И, счетные входы всех эк -триггеров соединены с тактовой шиной устройства, входы R всех «-триггеров соединены с ши. сброса устройства, выходы чет ртого зк -триггера являются выходными шинами устройства, прямой выход первого Эк -триггера соединен с входом J второго k -триггера, прямой вькод которого соединен с первьм входом первого логического элемента И, выход которого соединен с входом Э четвертого Эк -триггера, вход 3 первого Эк -триггера соединен с инверсным выходом четвертого JK -триггера, вход К - с прямым вьгходом второго Зк -триггера ,и с входом О третьего ЗК--триггера, инверсный выход соединен с вторым входом первого логического элемента И, вход К второго ЭК -триггера соединен с инверсным выходом третьего Jk-триггера и первым входом второго логического элемента И, второй вход которого соединен с инверсным выходом второго jK -триггера, а выход - вылид с входом к четвертого JK -триггера i и и ipmiepd, ВХОД k третьего Dk -триггера соединен с прямьм выходом четвертого JK триггера. При такой схеме соединения логические уравнения дпя J и К входов всех триггеров синхронного делителя частоты на 11 будут следующими: 4 «2-, К4 а25эНа фиг.1 приведена структурная схема синхронного делителя частоты на 11 на Зк -триггерах; на фиг.2 эn

сброса устройства, выход четвертого ;)К -триггера является выходом устройства, прямой выход триггера 1 соединен с входом 3 триггера 2, прямой выход которого соединен с первым входом элемента И 5, вькод которого соединен с входом 3 триггера 4, вход

3 триггера 1 соединен с инверсным выходом триггера 4 вход К - с прямым выходом триггера 2 и с входом J триггера 3, инверсный выход - с вторым входом элемента И 5, вход К триггера 2 соединен с инверсным выходом триггера 3 и первым входом элемента И 6, второй вход которого соединен с инверсным выходом триггера 2, выход - с входом триггера 4, прямой выход которого соединен с входом К триггера 3,

Работа синхронного делителя частоты на 11 на DK -триггерах полностью описывается логическими уравнениями дпя J и К входов еготриггеров. Этими же уравнениями определяется и схема соединения 3 и k входов с соответствующими выходами соответствующих триггеров.

По сигналу Сброс на шине 8 все триггеры синхронного делителя частоты на 11 устанавливаются в исходное нулевое положение. При этом (см. диаграммы на фиг,2 б, в, г, .д при

i 0), состояния равны

Q.-0 -, Qj-O ; ; .

Fia основании логических уравнений для J и к входов триггеров состояния входов равны

3,V ; . .,

К,0 ; kj,l ; , K -l.

Поскольку эк -триггер по последующему импульсу (на фиг. 1 и 2 триггеры переключаются по отрицательному . перепаду сигнала на счетном входе) при J 0. и К 0 не изменяет своего состояния, при и - переключается в противопо59 „ „

ложное состояние, при , - переключается в состояние логической единицы и при 3 и - переключается в состояние логического нуля, то по первому входному импульсу первый триггер переключается в состояние логической единицы (фиг. 2 б), второй триггер подтверждается в состоянии логического нуля (фиг.2 в), третий триггер не изменяет своего состояния (фиг.2 г), четвертьм триггер остается в состоянии логического нуля (фиг.2 д). Таким образом, по срезу

первого входного импульса только триггер 1 переключается.в состояние логической единицы, а триггеры 2, 3 и 4 остаются в нулевом состоянии, и состояния выходов станут равны

; Q2 0 ; . При этом состоянии входов станут

1 л

1 -

3. о , Jj- 1 ,

К, - ; Ц-.

По второму входному импульсу схема переходит в свое второе состояние (см. диаграммы на фиг.2 б, в, г, д при ), в котором Q 1 ; -, .

3, V;

т - i

3j-V-.

J.-V; 1 ,

К.Ч.

к.

К- -( . 2 1

Рассматривая далее работу предлагаемого синхронного делителя частоты на 11 на эк. -триггерах таким же образом, получим все значения входов и выходов каждого триггера при всех.ч.

Из сравнения логических уравнеНИИ для Ли К входов триггеров прототипа и синхронного делителя -часто- ты на 11 на JK -триггерах видно, что последний имеет меньшее количество элементов и цепеД, что положительно сказывается на надежности, потребляемой мощности и упрощает схему синхронного делителя частоты на 11 на ЗК -триггерах.

Выход

| название | год | авторы | номер документа |

|---|---|---|---|

| Синхронный делитель частоты на 9 на @ -триггерах | 1983 |

|

SU1148118A1 |

| Синхронный делитель частоты на 16 | 1984 |

|

SU1225010A1 |

| Устройство для дискретной регулировки фазы | 1982 |

|

SU1027639A1 |

| Делитель частоты с целочисленным коэффициентом деления | 1983 |

|

SU1095414A1 |

| Резервированный делитель частоты импульсов | 1977 |

|

SU698130A2 |

| Частотный компаратор | 1982 |

|

SU1045376A1 |

| Устройство для дистанционного изменения выходного напряжения декодирующего преобразователя | 1980 |

|

SU928597A1 |

| Резервированный делитель частоты | 1983 |

|

SU1128389A1 |

| Синхронный делитель частоты на 21 | 1985 |

|

SU1267613A1 |

| Синхронный делитель частоты на 14 | 1985 |

|

SU1243130A1 |

СИНХРОННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ НА II НА :к-ТРИГГЕРАХ, содержащий четыре DK- -триггера и два логических .элемента И, счетные входы всех Пктриггеров соединены с тактовой шиной устройства, входы R всех JK триггеров соединены с шиной сброса устройства, выходы четвертого JK триггера являются выходными шинами устройства, прямой выход первого Л1стриггера соединен с входом J второго - -триггера, прямой выход которого соединен с первым входом первого логического элемента И, выход которого соединен с входом D четвертого 3k -триггера, отличающийся тем, что, с целью упрощения устройства, вход 3 первого ЗК триггера соединен с инверсным выходом четвертого JK -триггера, вход К - с прямым выходом второго -Тк триггера и с входом 3 третьего jK-триггера, инверсный выход соединен с вторым входом первого логического элемента И, вход К второго JK-триггера соединен с инверсным выходом третьего Зк -триггера и (Л первым входом второго логического элемента И, второй вход которого соединен с инверсным выходом второго : К-триггера, а выход - с входом к четвертого зк.-триггера, вход k третьего Jk -триггера соединен с прямым выходом четвертого ЗК -триг гера. ел о ч| ел 00

(риг.1

. 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Букреев H.FI., Мансуров Б.М., Горячев В.И | |||

| Микроэлектронные схемы цифровых устройств | |||

| М., Советское радио, 1975 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Будинский Я | |||

| Логические цепи в дафровой технике | |||

| Пер | |||

| с чешского под ред | |||

| Б.А.Калабекова | |||

| М., Связь, 1977 (прототип) | |||

Авторы

Даты

1985-04-15—Публикация

1983-10-10—Подача