(54) УСТРОЙСТВО СИНХРОНИЗАЦИИ АДАПТИВНОЙ Изобретение относится к многоканаяъ ным системам связи и предназначено для работы в адаптивных системак передачи дискретной информации. По основному авт. св.. NJ 566372 известно устройство синхронизации адаптивной системы связи Щ , содержащее фильтр тактовой частоты, подключенный входом к блоку высокой и промежу- точной частоты, а выходом через, первый, и второй ключевые блоки - к входам блоков сравнения, другие входы которых соединены с формирователем эталонного напряжения. Вьссод первого блока сравнения подключен к синхронизируемому входу рзаспределителя импульсов и к входу реле времени через элемент ИЛИ, а к первому входу триггера - непосредственно. Выход второго блока сравнения подсоединен к второму входу элемента ИЛИ через блок задержки и к второму входу реле времени непосредственно. Выход реле времени подключен к второму входу триггера, выходы которого соединены с управляющими СИСТЕМЫ СВЯЗИ чвходами ключевых блоков. Распределитель импульсов входом подключен к выходу Генератора опорной частоты, а выходом :к дешифратору кокаднд, вход которого соединен с входами фильтра тактовой частоты. и деши4ратора информации, а выход - со вторым входом триггера и синхронизиру емым входом дополнительного распределителя, соединенного также с генератором опорной частоты и дешифратором информации. Недостатком известного устройства является отсутствие необходимой помехоустойчивости и точности синхронизации. Цель изобретения - повышение помехоустойчивости и точности синхронизации. Для этого в устройство синхронизации адаптивной системы связи по авт, св. № 566372, содержащее распределитель импульсов, один из входов которого подключен к выходу фильтра тактовой часто- ты, а другой - к генер)атору опорной чдстоты, а также деигнфр-чтор команд, дог.оп ительный распределитель, первый м .

второй ключевые блоки, первый и второй блоки сравнения, формироватеть этапонИог р напряжения, триггер, реле времени, блок задержки и элемент ИЛИ, введены блок коррекции, блок управления и блок j преобразования. При этом выкод элемента ИЛИ через блок коррекции подключен ко второму В5СОДУ распределителя импульсов, дополнительный выход генератора. опорной частоты - к дополнительному10

входу блока высокой и промежуточной частоты, а через блок управления - к дополнительным входам фильтра тактовой часто ты, первого и второго ключевых блоков, блока коррекции и ко входу блока преоб- 15 разЬЁШйя, выход которого подсоединен к другому д ополнительному входу фильтра тактовой частоты.

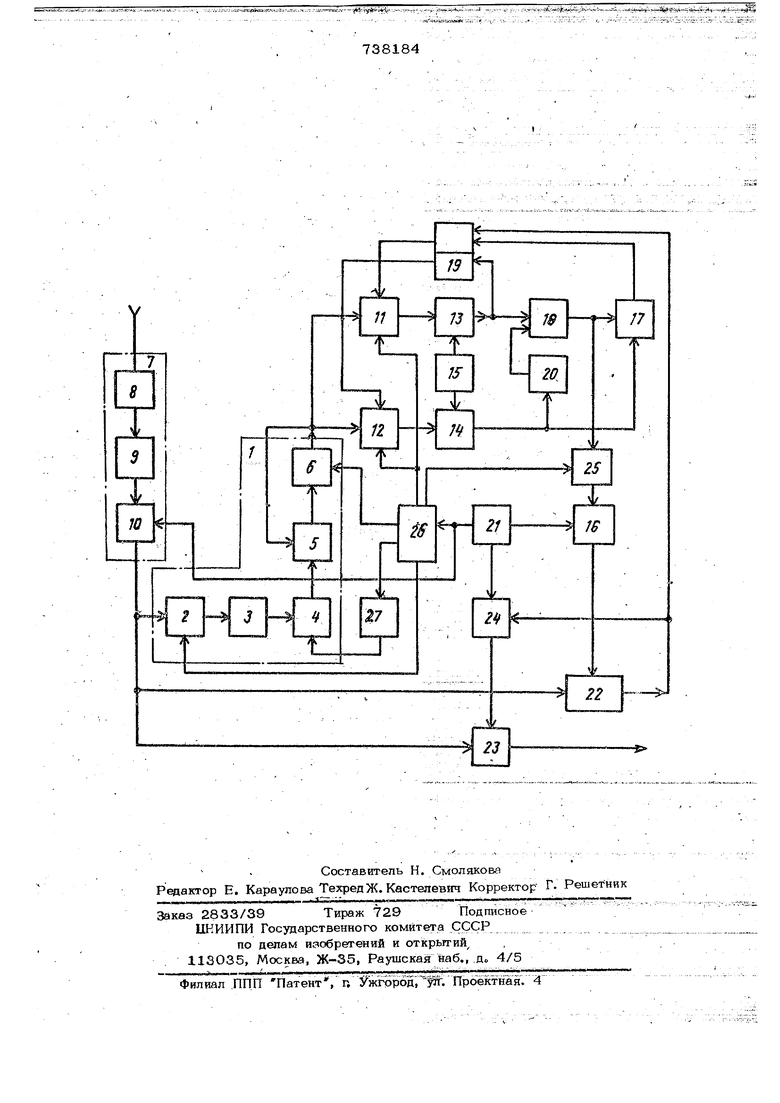

На чертеже представлена структурная электрическа а схема предложенного уст- 20 ройства.

Устройство синхронизации адаптивной системы связи содержит фильтр 1 такго- вой частоты, в состав которого входят

ёлок 2 записи, блок 3 памяти, блок 4 25 счйтыванйя/сумматор 5 и буферный регистр 6 сдвига,, Вход фильтра 1 тактовой частоть подключен к блоку 7 высокой и промежуточной частоты, который образован последовательно включенными линей- 30 ным.. радиотрактом В, блоком канальных фильтров 9 и аналого-цифровым преобразователем 1О. Выход фильтра 1 т.актовой Частйты подключен через первый 11 и второй 12 ключевьш блоки к входам первого 35 13 и второго 14 блоков сравнения, ДРУгие входы которых соединены с формирователем 15 эталонного напряжения. Выход первого блока 13 сравнения подключен к синхронизируемому входу распреде- 40 лиселя 16 импульсьв и к входу реле 17 времени через элемент ИЛИ 18, а к пер вому входу триггера 19 непосредственно. Выход второго блока 14 сравнения 14 подключен к второму Входу элемента ИЛИ 18 через блок 20 задержки и непосредст вёвпб ко второму входу репе 17 времени, выход которого подсоединен ко второму входу триггера 19. Bbixoh этого тригге jSaсбедшен с управляющими входами клю-50 чевых блоков 11 и 12. Распределитель 16 импульсов подключен к выходу генератора 21опорной частоты , а выход расгфеделителя - к дешифратору 22 команд, вход которого соединен с входами фильт- 5, ра 1 тактовой частоты и дешифратора 23 информации. Выход деши эатора 22 команд ШЩйнён со вторым входом триггера 19

.и синхронизируемым входом дополнительного распределителя 24, подключенного к генератору 21 опорной частоты и дешифратору 23 информации. Выход элемента ИЛИ 18 подключен через блок 25 коррекции ко второму входу распределителя 16 импульсов. Дополнительный вь(ход генератора 21 опорной частоты подключен к дополнительному входу блока 7

высокой и промежуточной частоты, а через блок 26 управления - к дополнительным входам фильтра 1 тактовой частоты 1, ключевых блоков 11 и 12, блока 25 коррекции и ко входу блока 27 преобразования, выход которого подключен к другому .дополнительному входу фильтра тактовой частоты.

Устройство работает следующим образом.

Входной сигнал адаптивной системы связи, состоящий И1з совокупности команд и информационных посылок (режиму передачи информации всегда предшествует обмен командами, которые могут быть Перданы с по мощью многочастотного составного сигнала), поступает в блок 7 вь сокой и промежуточной частоты, где проходит обработку в линейном радиотракте .8, кабальных фильтрах .и аналого-цифрово преобразователе 10. В аналого-цифровом преобразователе 10 выполняется квантование огибающей входного сигнала. Ра ,ботрй аналого-цифрового преобразователя 1О управляет генератор 21 опорной частоты, задающий частоту дискретизации входного сигнала. Таким образом, на выходе аналого-цифрового преобразователя 10 формируется последовательность чисел отражающих значения огибающей напря|женИя на выходе кайфого из канальных .1фильтров 9 в момент.ы .дискретизации.

Значения огибающей с выхода аналогоцифрового преобразователя 10 поступают через блок,2 записи в блок 3 памяти. Записью значений огибающей управляет блок 26.. Емкость блока 3 памяти определяется ДПИТёЛьностью Существования сйгнаЛй, используемого для синхронизации. Например, если для синхронизации адаптивной системы связи используют комбинацию из п информационных символов, то блок 3 памяти должен вместить значения отсчетов огибающей входного сигнала, следующих с частотой дискретизаций, на протяжении п символов. Перед началом интервала времени, соответст1вующёго приходу первого зна. чения огибающей сигнала, относящегося к п + 1 символу, первое значение . символа стирается из блока 3 памяти. Интервал существования сигнала Т, соответствующий передаче одного информационного символа (нуля или единицы), в процессе дискретизации оказьь. вается разбитым на к подынтервалов. Величина к определяется принятой часдотой дискретизации которая должна быть выбрана с учетом возможности во становления сигнала, подвергнутого дискретизации (частота дискретизации превышает 2F , где F - наивысшая спектра ная составляющая сигнала) и с учетом требуемой точности синхронизапий, так как положение интервала существования сигнала после его дискретизации мокет быть ойределено с точностью Т/2к Структура сигнала, используемого для синхронизации, выбирается таким образом чтобы сложение значений огибающей сиг нала в соответствии со структурой сигйа ла давало ярко выраженный максимум в соверщенно определенный момент-времен на интервале существования информационного символа. Вьщвление такого максимума на протяжении п символов, из которык состоит сийхронизирующая комбинация, повыщает вероятность правильного определения положения максимума, а следовательно, положение начала и конца интервала Т , которые заранее не избестны, известны лишь величина интервала Т и структура сигнала синхронизации. В конце каждого интервала Т значения огибающей, хранящиеся в блоке 3 памяти, считываются с помощью блока 4 считывания 4, работой которого управляет блок 26 управления через блок 27 преобразования. Счетывание производится К раз в соответствии с выбранной на данный период времени структурой сигнал синхронизации. Каждый раз меняется предполагаемое начало отсчета: сначала предполагают началом интервала подынтервал, затем 2-й, 3-й ... и к -и. ПриКаждом из к считываний последовательность значений огибающей из блока 3 памяти поступает на сумматор 5 и затем в буферный регистр 6 сдвига. Каждое последующее значение огибающей поступает на первый вход сумматора 5 и и нем складывается с суммой пре- дьщущих значений, которая хранится в .буферном регистре 6 и поступает на вто рой вход сумматора 5. После того, как

738184 Г5)осуммированы значения огибающих, .относяшиеся к исследуемому интервалу длительностью п-Т , peaynefaT у мирования;, оказавшийся в буферном регистре 6 сдвига 8, сравнивается с установленным порогом. Определение момента сравнения происходит по сигналам от бло:ка 26 управления, который управляет тактовым входом буферного регистра 6 сдвига и воздействует в нужные момент: времени на вторые управляющие входы первого и второго ключевых блоков Ц и 12. Ключевые блоки 11 и 12 открыты, если на обоих управляющих входах этих блоков присутствуют необходимые напряжения. В исходном положении устройства в состоянии готовности находится первый ключевой блок 11, а второй ключевой блок 12 закрыт с помощью одного из управляющих напряжений от триггера 19. Сигналы, поступающие с выхода блока 26 управления ко вторым управляющим входам ключевых блокЬв 11 и 12, открывают первый ключевой блок 11, через который -проходит результат суммирования из буферного регистра 6 сдвига на первый блок 13 сравнения. Операция сравнения выполняется к раз в конце каждого интервала Т . Как только зЬачение числа в буферном регистре 6 сдвига превысит значение минимального порога, вырабатываемого .формирователем 15 эталонного напряжения, сигнал обнаружен. Значение мйнитльного пброга определяется в зависимости от чувствительности приемного стройстйа, разрешающей спо- собности дешифраторов и длины синхронизирующей комбинации ( п ). При превышении значения минимального порога на входе первого блока.13 сравнения формируется импульс напряжения, который, пройдя черезэлемент ИЛИ 18, запускает реле 17 времени и через блок 25 коррекции осуществляет коррекцию 4йзы распределителя 16 импульсоб. Однорременно с этим импульс напряжения с выхода рервогр блока сра&ения ставит триггер 19 в положение, при котором первый ключевой блок 11 оказывается закрытым, а второй ключевой блок 12 подготавливается к открыванию при помощи напряжений, воздействующих на первые входь ключевых блоков. Блок 25 коррекции служит для определения положения импульса коррекции в зависимости от того, на каком из к считываний прюизсяило превышение порога И, следовательно, какой из к подынтервалов Т следует считать первым. Второй вход блока коррекции связан с блоком 26 управления, и нанего поступают сигналы, содержащие сведения о том, какой из подынтервалов анализируется. В случае правильного приема команды на выходе дешифратЬра 22 команд форми руется сигнал команда принята , которы .используется для Коррекции фазы дополнительного распределителя 24, обеспечивающего работу деши4ратора 23 информации. Одновременно с коррекцией фазы дополнительного распределителя 24 им пульсом команда принята триггер 19 ставится в исходное положение, при котором первый ключевой блок 11 подго- тавливается к открыванию, а второй ключевой блок 12 закрывается. ЕСЛИ декодирования кокшнды не произойдет, возвращение .устройства в исходное положение производится с помощью сигнала от реле 17 времени, который ставит триггер 19 в исходное положение по истечении интервала времени, отведен ного на дешифрование команды. .Если в течение времени, когда дешифратор 22 занят анализом сигнала, вызвавшего превышение минимального .порот га срабатывания порл блоке 13 сравнения), на вход устройства проходит другой сигнал, от воздействия которо го формируется суммарное значение огибающей в буферном регистре 6 сдвига, превышающее порогое значение пор2 ( пор ), в этом случае происходит повторная коррекция распределителя 16 прежде, чем закончитсяцикл работы дешифратора 22 команд. Результат суммирования с буферного регистра сдвига открытый второй ключевой блок 12 поступает на второй блок 14 сравнения. При превышении порога 2.пор г на.выходе второго блока сравнения формируется импульс напряжения, который сбрасывает 17 времени в исходное положение . и через блок 20 задержки поступает на элемент ИЛИ 18. Импульс напряжения на выходе лемента ИЛИ 18 через блок 25 коррекии производит новую коррекцию фазы аспределителя 16, Начиная с этого момента, в дешифраторе 22 команд веется анализ нового сигнала, ЕЗлок 20 адержки введен в устройство для обеспечеия надежной установки реле времени в наальное положение. Величина задержки выбиается меньше длительности интервала меж.у операциями сравнения, Все устройство возвращается в исход- нов положение либо после появления сиг нала команда принята, которым одновре- Менно осуществляются коррекция фазы дополнительного распределителя 24 и установк,а триггера 19 в исходное поло.жение, либо по истечении интервала времени, отводимого на отбраковку ложного сигнала, по команде от реле времени. Формула изобретения Устройство синхронизации адаптивной системы связи по авт. св. № 566372, отл VI ч а ющееся тем, что, с целью повьпиения помехоустойчивости и точности синхронизации, введены блок коррекции, блок управления и блок преобразования, причем выход элемента ИЛИ через блок коррекции подключен ко второму входу распределителя импульсов, а дополнительный выход генератора опорной частоты подключен к дополнительному ВХОДУ блока высокой и промежуточной частоты, а через блок управления - к дополнительным входам фильтра тактовой частоты, первого и второго ключевых блоков, блока коррекции и ко входу бло- ка преобразования, выход которого подключен к другому дополнительному входу фильтра тактовой частоты. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 566372, м. Н 04 Т 3/06, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации адаптивной системы связи | 1975 |

|

SU566372A2 |

| Устройство приема телеметрической информации | 1989 |

|

SU1735883A1 |

| Приемник многочастотных сигналов | 1991 |

|

SU1775874A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СИГНАЛОВ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 1997 |

|

RU2110890C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА КОМАНД ТЕЛЕУПРАВЛЕНИЯ | 1991 |

|

RU2023309C1 |

| ЦИФРОВАЯ СИСТЕМА ТЕЛЕВИДЕНИЯ | 1999 |

|

RU2173030C2 |

| Многоканальное устройство для сбора данных | 1983 |

|

SU1095163A1 |

| Устройство для сигнализации с индикацией местоположения аварийного объекта | 1982 |

|

SU1121689A1 |

| Адаптивная телеметрическая система | 1979 |

|

SU783825A1 |

| Адаптивный цифровой корректор | 1979 |

|

SU794734A1 |

Авторы

Даты

1980-05-30—Публикация

1977-05-23—Подача