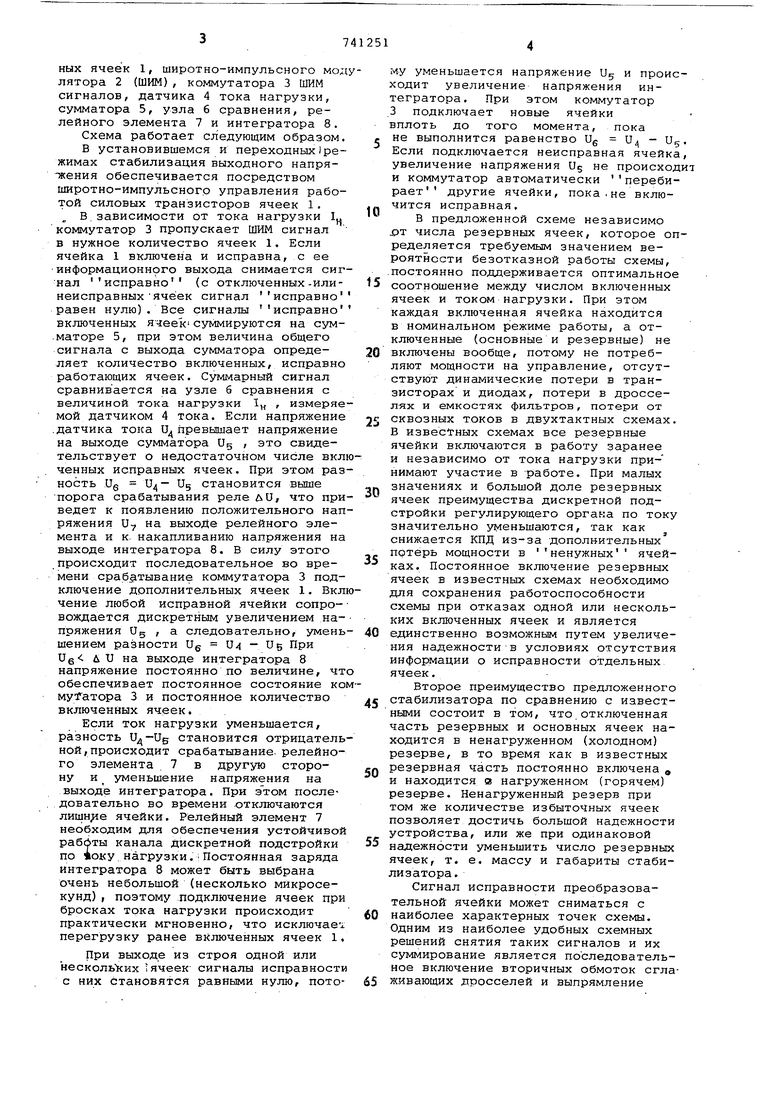

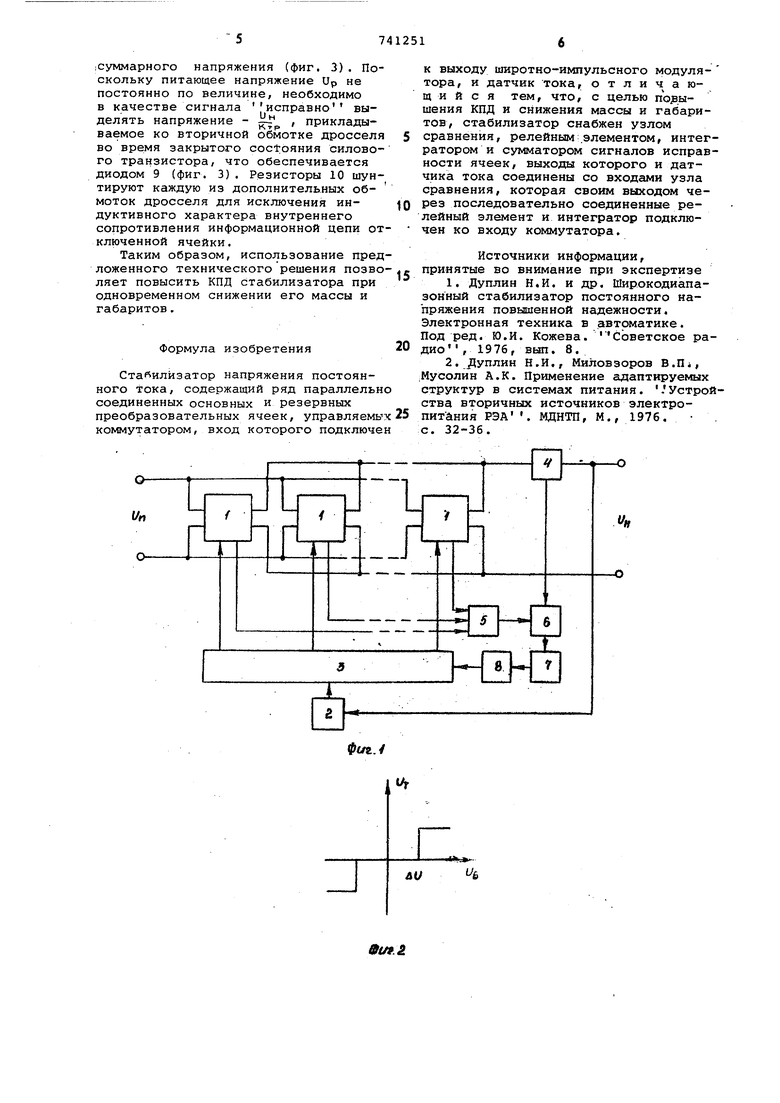

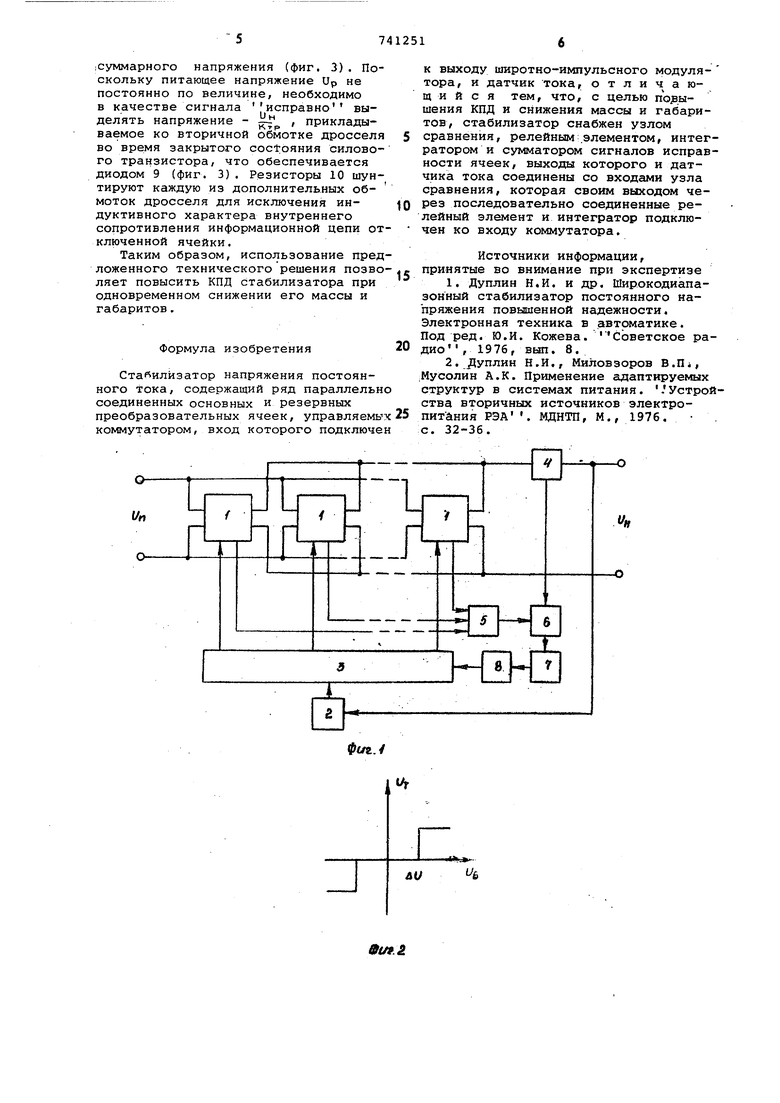

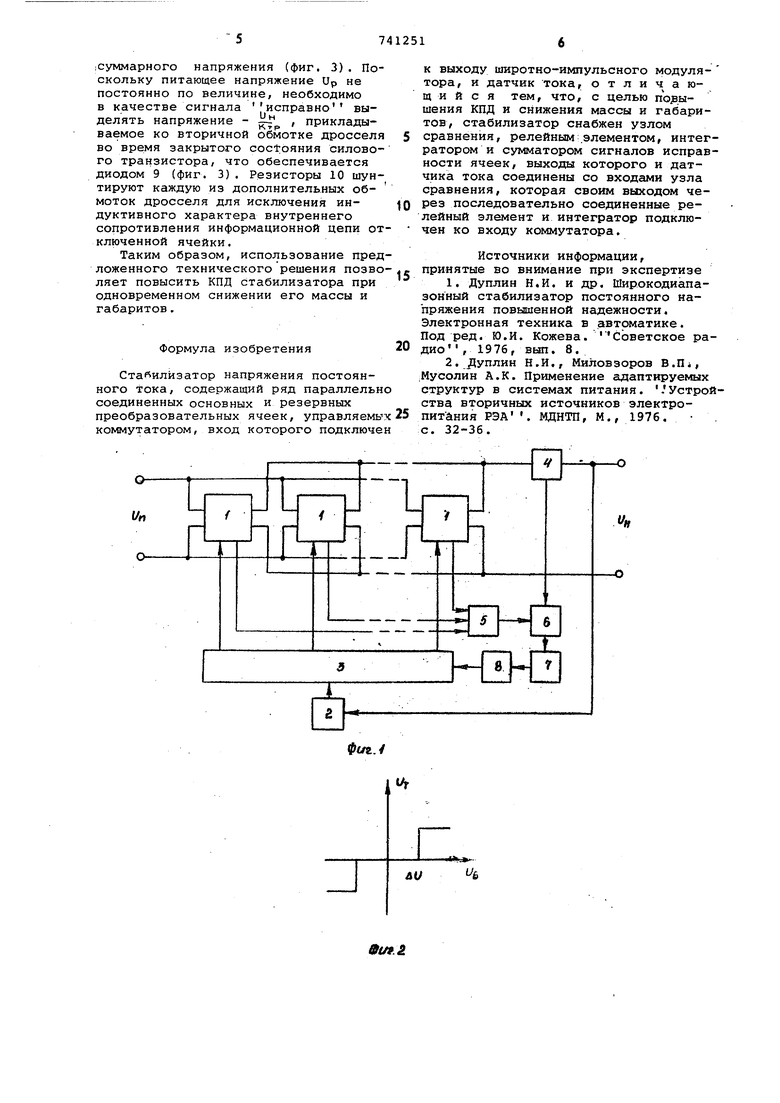

Изобретение относится к электротехнике, в частности к устройствам питания аппаратуры постоянным током и может быть использовано при разработке вторичных источников питания. Известны импульсные стабилизаторы постоянного напряжения, регулиру ющий орган которых состоит из мощной преобразовательной ячейки, схемы сравнения и широтно-импульсного модулятора 1. . Недостатками таких схем являются снижение КПД при работе на малых нагрузках по отношению к номинальному значению и низкая надежность. Наиболее близким техническим .решением является стабилизатор напряжения постоянного тока, содержащий ряд параллельно соединенных основных и резервных преобразовательных ячеек управляемых коммутатором, вход которого подключен к выходу широтно-импульсного модулятора, и датчик тока 2 . Недостатком таких стабилизаторов является малоэффективное использование резервных ячеек, что приводит к ухудшению массогабаритных и Ьнергетических показателей устройства в целом. Это объясняется тем, что в таких схемах резервная часть ячеек включается в работу полностью, независимо от уровня потребляемой мощности. Цель изобретения - повышение КПД стабилизатора и у1чечьшение веса и габаритов. Поставленная цель достигается тем, что стабилизатор напряжения постоянного тока, содержащий ряд йараллельно соединенных основных и резервных преобразовательных ячеек, управляемых коммутатором, вход которого подключен к выходу широтно-импульсного модулятора, и датчик тока, снабжен узлом сравнения, релейным элементом, интегратором и сумматором сигнала исправности ячеек, выходы которого и датчика тока соединены со входами узла сравнения, которая своим выходо через последовательно соединенные релейный элемент и интегратор подключена ко входу коммутатора. На фиг. 1 показана структурная схема стабилизатора; на фиг, 2 и 3 график и схема, поясняющие работу устройства. Стабилизатор напряжения постоянно го тока состоит из основных и резярв ных ячеек 1, широтно-импульсного мод лятора 2 (ШИМ), коммутатора 3 ШИМ сигналов, датчика 4 тока нагрузки, сумматора 5, узла 6 сравнения, релейного элемента 7 и интегратора 8. Схема работает следующим образом. В установившемся и переходных 1режимах стабилизация выходного напря жения обеспечивается посредством широтно-импульсного управления работой силовых транзисторов ячеек 1. В.зависимости от тока нагрузки 1 коммутатор 3 пропускает ШИМ сигнал в нужное количество ячеек 1. Если ячейка 1 включена и исправна, с ее информационного выхода снимается сиг нал исправно (с отключенных-илинеисправныхячеек сигнал исправно равен нулю). Все сигналы исправно включенных я-ч:еек суммируются на сумматоре 5, при этом величина общего сигнала с выхода сумматора определяет количество включенных, исправно работающих ячеек. Суммарный сигнал сравнивается на узле б сравнения с величиной тока нагрузки 1 , измеряе мой датчиком 4 тока. Если напряжение .датчика тока U превьлиает напряжение на выходе сумматора Ug , это свидетельствует о недостаточном числе вкл ченных исправных ячеек. При этом раз ность Ug и - Ug становится выше порога срабатывания реле ли, что при ведет к появлению положительного нап ряжения U-7 на выходе релейного элемента и к накапливанию напряжения на выходе интегратора 8. В силу этого происходит последовательное во времени срабатывание коммутатора 3 подключение дополнительных ячеек 1. Вкл чение любой исправной ячейки сопровождается дискретным увеличением напряжения Ug , а следовательно, умень шением разности Ug U Ug При U6 ли на выходе интегратора 8 напряжение постоянно по величине, чт обеспечивает постоянное состояние ко муТатора 3 и постоянное количество включенных ячеек. Если ток нагрузки уменьшается, разность становится отрицатель ной, происходит срабатывание, релейного элемента 7 в другую сторону и уменьшение напряжения на выходе интегратора. При эЪом последовательно во времени отключаются лишн;1е ячейки. Релейный элемент 7 необходим для обеспечения устойчивой рабЛты канала Дискретной подстройки по «оку нагрузки.Постоянная заряда интегратора 8 может быть выбрана очень небольшой (несколько микросекунд) , поэтому подключение ячеек при бросках тока нагрузки происходит практически мгновенно, что исключаем перегрузку ранее включенных ячеек 1 При выходе из строя одной или нескольких Г ячеек сигналы исправност с них становятся равными нулю, пото му уменьшается напряжение U5 и происодит увеличение напряжения интегратора. При этом коммутатор 3 подключает новые ячейки плоть до того момента, пока не выполнится равенство Ug U - Ug. Если подключается неисправная ячейка, увеличение напряжения Ug не происходит и коммутатор автоматически перебирает другие ячейки, пока.не включится исправная. В предложенной схеме независимо .рт числа резервных ячеек, которое определяется требуемым значением вероятности безотказной работы схемы, постоянно поддерживается оптимальное соотношение между числом включенных ячеек и током нагрузки. При этом каждая включенная ячейка находится в номинальном режиме работы, а отключенные (основные и резервные) не включены вообще, потому не потребляют мощности на управление, отсутствуют динамические потери в транзисторах и диодах, потери в дросселях и емкостях фильтров, потери от сквозных токов в двухтактных схемах. В извес гннх схемах все резервные ячейки включаются в работу заранее и независимо от тока нагрузки принимают участие в работе. При малых значениях и большой доле резервных ячеек преимущества дискретной подстройки регулирующего органа по току значительно уменьшаются, так как снижается КПД из-за дополнительных потерь мощности в ненужных ячейках. Постоянное включение резервных ячеек в известных схемах необходимо для сохранения работоспособности схемы при отказах одной или нескольких включенных ячеек и является единственно возможным путем увеличения надежности в условиях отсутствия инфогмации о исправности отдельных ячеек. Второе преимущество предложенного стабилизатора по сравнению с иавестными состоит в том, что.отключенная часть резервных и основных ячеек находится в ненагруженном (холодном) резерве, в то время как в известных резервная часть постоянно включена и находится а нагруженном (горячем) резерве. Ненагруженный резерв при том же количестве избыточных ячеек позволяет достичь большой надежности устройства, или же при одинаковой надежности уменьшить число резервных ячеек, т. е. массу и габариты стабилизатора. Сигнал исправности преобразовательной ячейки может сниматься с наиболее характерных точек схемы. Одним из наиболее удобных схемных решений снятия таких сигналов и их суммирование является последовательное включение вторичных обмоток сглаживающих дросселей и выпрямление |Суммарного напряжения (фиг. 3). Поскольку питающее напряжение Up не постоянно по величине, необходимо в качестве сигнала исправно , прикладыделять напряжение ваемое ко вторичной обмотке дросселя во время закрытого состояния силового транзистора, что обеспечивается диодом 9 (фиг. 3). Резисторы 10 шунтируют каждую из дополнительных обмоток дросселя для исключения индуктивного характера внутреннего сопротивления информационной цепи от ключенной ячейки. Таким образом, использование пред ложенного технического решения позво ляет повысить КПД стабилизатора при одновременном снижении его массы и габаритов. Формула изобретения Стабилизатор напряжения постоянного тока, содержащий ряд параллельн соединенных основных и резервных преобразовательных ячеек, управляемы коммутатором, вход которого подключе к выходу широтно-импульсного модулятора, и датчик тока, отличающийся тем, что, с целью порышения КПД и снижения массы и габаритов, стабилизатор снабжен узлом сравнения, релейным .элементом, интегратором и сумматором сигналов исправности ячеек, выходы которого и датчика тока соединены со входами узла сравнения, которая своим выходом через последовательно соединенные релейный элемент и интегратор подключен ко входу коммутатора. Источники информации, принятые во внимание при экспертизе 1.Дуплин Н.И. и др. Широкодиапазонный стабилизатор постоянного напряжения повышенной надежности. Электронная техника в автоматике. Под ред. Ю.И. Кожева. Советское радио , 1976, вып. 8. 2./{уплин Н.И., Миловзоров В.П, .Мусолин А.К. Применение адаптируемых структур в системах питания. . Устройства вторичных источников электроПИТйння РЭА. МДНТП, М., 1976. . с. 32-36.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофазный импульсный стабилизатор постоянного напряжения | 1983 |

|

SU1111140A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1986 |

|

SU1386978A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1986 |

|

SU1396134A1 |

| Многофазный импульсный стабилизатор напряжения | 1986 |

|

SU1390605A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1988 |

|

SU1561068A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1985 |

|

SU1348801A1 |

| Многофазный импульсный стабилизатор постоянного напряжения (его варианты) | 1984 |

|

SU1157532A1 |

| Импульсный стабилизатор переменного напряжения | 1987 |

|

SU1493987A1 |

| Преобразователь напряжения с многозонной импульсной модуляцией | 1980 |

|

SU985772A1 |

| Многофазный импульсный стабилизаторпОСТОяННОгО НАпРяжЕНия | 1979 |

|

SU824161A1 |

ь

ли

Авторы

Даты

1980-06-15—Публикация

1978-01-23—Подача