элементов ИЛИ и третий вход третьего элемента И образуют второй управляющий вход-выход блока, вторые входы четвертого и пятого элементов И соединены с выходом второго элемента И, информационный выход первого регистра и вход второго регистра соединены с первым информационным входом-выходом блока, а информационные вход первого регистра и выход второго регистра соединены с вторым информационным входом-выходом блока.

2. Устройство по п. 1, отличающееся тем, что блок шифрации информационного слова содержит коммутатор, два регистра и два элемента задержки, причем информационный, адресный и стробирующий входы коммутатора соединены соответственно с адресным, информационным и вторым синхронизирующим входами блока, группа выходов - с соответствующими установочными входами -разрядов первого регистра, стробирующий вход которого соединен через первый элемент задержки с первым синхронизирующим входом блока, а информационный выход - с информационным входом второго регистра, стробирующий вход которого соединен через второй элемент задержки с вторым синхронизирующим входом блока, информационные вход первого регистра и выход второго регистра соединены с информационным входом-выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с абонентом | 1986 |

|

SU1334154A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Устройство для сопряжения ЭВМ с разноскоростными группами внешних устройств | 1989 |

|

SU1683022A1 |

| Устройство для сопряжения ЭВМ с разноскоростными группами внешних устройств | 1990 |

|

SU1837302A1 |

| Устройство для сопряжения ЭВМ с М внешними устройствами | 1986 |

|

SU1374232A1 |

| Устройство для сопряжения ЭВМ с внешней памятью | 1987 |

|

SU1515166A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Устройство для сопряжения электронной вычислительной машины с внешними устройствами | 1983 |

|

SU1267428A1 |

| Устройство для сопряжения ЭВМ с каналами связи | 1987 |

|

SU1532937A1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

УСТРОЙСТВО ДЛЯ ОБМЕНА ИНФОРМАЦИЕЙ, содержащее буферный регистр информации, первый вход-выход которого является информационным входомвыходом устройства, и М каналов, каждьщ из которьгх включает блок сопряжения, причем первые управляющие входы-выходы блоков сопряжения каналов соединены черезуправляющую щину между собой и с управляющим ВХОДОМ.-ВЫХОДОМ устройства, а вторые управляющие входы-выходы образуют группу управляющих входов-выходов устройства, отличающееся тем, что, с целью сокращения аппаратурных затрат, в него введены блок коммутации, а в каждый канал - блок, шифрации информационного слова, причем адресные входьг блока коммутации и блоков сопряжения и шифрации информационного слова каналов через адресную шину .соединены с адресным входом устройства, первые информационные входывыходы блоков сопряжения каналов, информационные входы блоков шифрации информационного слова каналов и блока коммутации через информационную шину соединены между собой и вторым входомвыходом буферного регистра информации, в i-м канале

Изобретение относится к автоматике и вычислительной технике и может быть использовано в различных системах автоматического управления, где рещается задача логического управления технологичес.кими агрегатами и установками по заданной программе или в соответствии со значениями логических функций, характеризующих состояние управляемого объекта.

Известно устройство для обмена, содержащее регистры, блок управления, блок формирования сигналов группового управления, операционные блоки, дещифраторы и коммутаторы 1.

Недостатком устройства является низкая производительность, так как оно допускает обмен только многоразрядными словами.

Наиболее близким к предлагаемому по технической сущности является устройство для обмена информацией между ЦВМ и внешними устройствами, содержащее группу каналов обмена, каждый из которых соде ржит блок подготовки канала, блок обработки запросов, блок управления, блок селекции внещних запросов, счетчик слов и счетчик текущего адреса, регистр информации, вход и выход которого соединены соответственно с первыми информационными входом и выходом устройства, блок синхронизации, входы которого подключены к синхронизирую щим входам устройства, щифратора команд и Каналов обмена, а выход - через щину синхронизации с входами синхронизации каналов обмена, выходы щифратора команд и командные выходы каналов обмена подключены через щину команд к выходу команд устройства, выходы опроса каналов соединены через щйфратор опросов с выходом опроса устройства, а входы запроса

и признака направления передачи - с группами входов запроса и управления устройства. Блок селекции внещних запросов канала обмена содержит два элемента И, элемент

НЕ и элемент задержки. Блок обработки запросов канала обмена содержит четыре триггера три элемента И и элемент НЕ. Блок управления канала обмена содержит четыре элемента И, элемент ИЛИ и элемент НЕ. Блок подготовки канала содержит два триггера и три элемента И. Блок синхронизации устройства содержит группу элементов И, генератор, триггер, счетчик, распределитель импульсов, два элемента И-ИЛИ и элемент ИЛИ 2.

Недостатки данного устройства состоят в больщих аппаратурных затратах и ограниченных функциональных возможностях, снижающих производительность технологической системы при бытовых обменах.

Цель изобретения - сокращение аппа0 ратурных затрат и расширение функциональных возможностей устройства.

Цоставленная цель достигается тем, что в устройство для обмена информацией, содержащее буферный регистр информации, первый вход-выход которого является информационным входом-выходом устройства, и М каналов, каждый-из которых включает блок сопряжения, причем первые управляющие входы-выходы блоков сопряжения каQ налов соединены через управляющую щину между собой и с управляющим входом-выходом устройства, а вторые управляющие входы-выходы образуют группу управляющих входов-выходов устройства, введены блок коммутации, а в каждый канал - блок

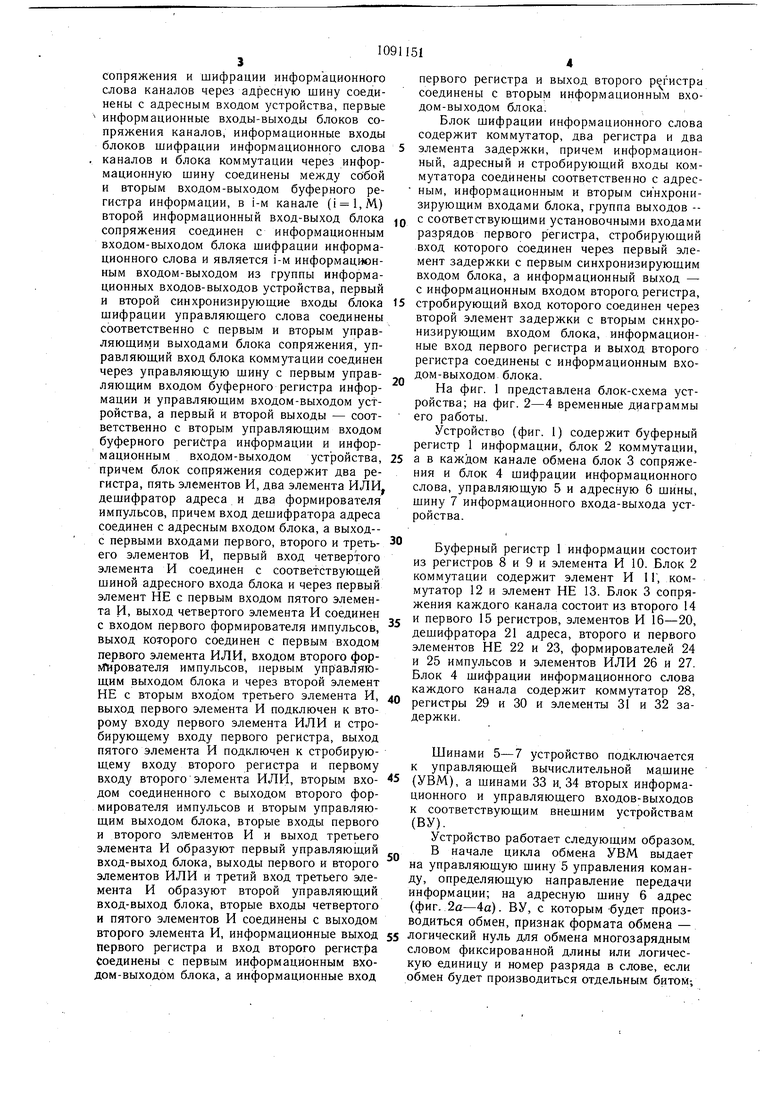

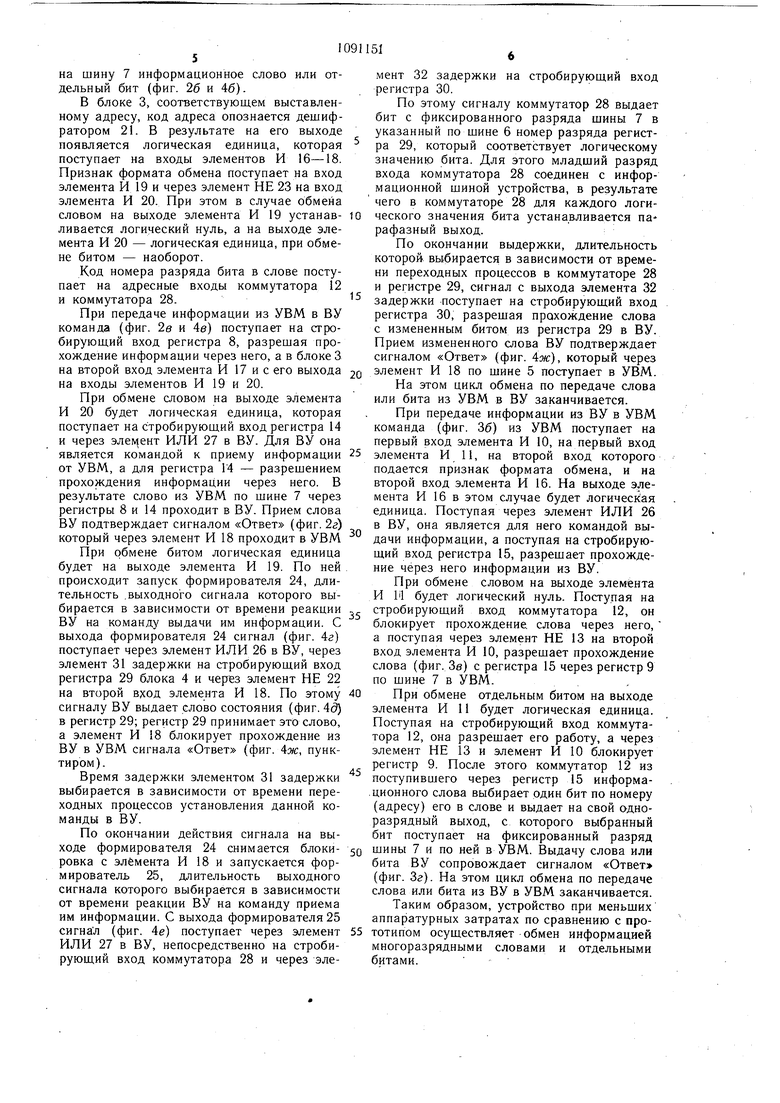

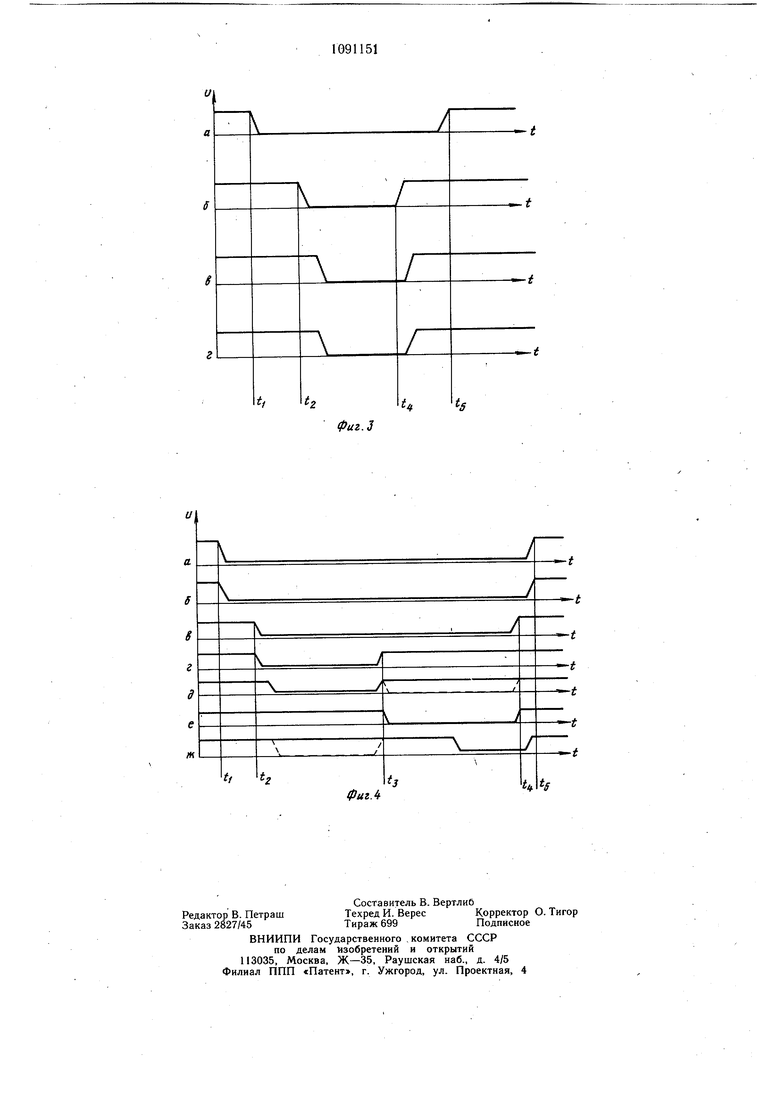

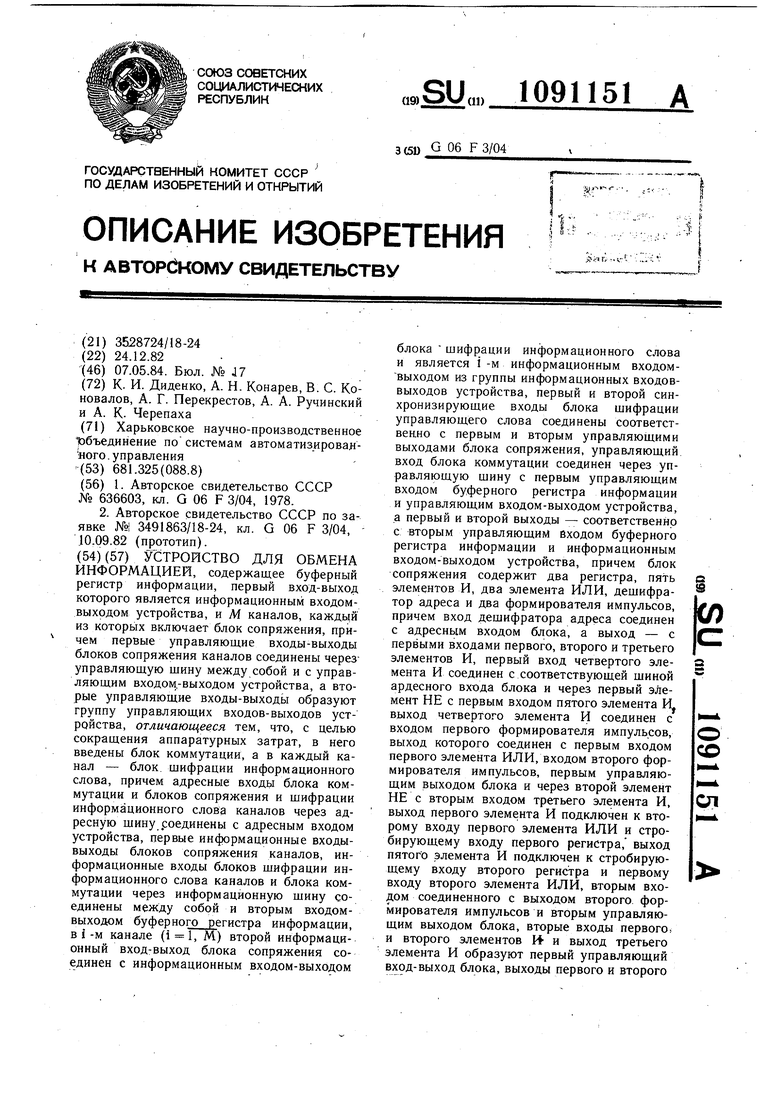

5 щифрации информационного слова, причем адресные входы блока коммутации и блоков сопряжения и шифрации информационного слова каналов через адресную шину соединены с адресным входом устройства, первые информационные входы-выходы блоков сопряжения каналов, информационные входы блоков шифрации информационного слова каналов и блока коммутации через информационную шину соединены между сббой и вторым входом-выходом буферного регистра информации, в i-M канале (,M) второй информационный вход-выход блока сопряжения соединен с информационным входом-выходом блока шифрации информационного слова и является i-м информационным входом-выходом из группы информационных входов-выходов устройства, первый и второй синхронизирующие входы блока шифрации управляющего слова соединены соответственно с первым и вторым управляющими выходами блока сопряжения, управляющий вход блока коммутации соединен через управляющую шину с первым управляющим входом буферного регистра информации и управляющим входом-выходом yctройства, а первый и второй выходы - соответственно с вторым управляющим входом буферного регистра информации и информационным входом-выходом устройства, причем блок сопряжения содержит два регистра, пять элементов И, два элемента ИЛИ дешифратор адреса и два формирователя импульсов, причем вход дещифратора адреса соединен с адресным входом блока, а выход-с первыми входами первого, второго и третьего элементов И, первый вход четвертого элемента И соединен с соответствующей щиной адресного входа блока и через первый элемент НЕ с первым входом пятого элемента И, выход четвертого элемента И соединен с входом первого формирователя импульсов, выход которого соединен с первым входом первого элемента ИЛИ, входом второго фор Гирователя импульсов, первым управляющим выходом блока и через второй элемент НЕ с вторым входом третьего элемента И, выход первого элемента И подключен к второму входу первого элемента ИЛИ и стробирующему входу первого регистра, выход пятого элемента И подключен к стробирующему входу второго регистра и первому входу второго элемента ИЛИ, вторым входом соединенного с выходом второго формирователя импульсов и вторым управляющим выходом блока, вторые входы первого и второго элементов И и выход третьего элемента И образуют первый управляющий вход-выход блока, выходы первого и второго элементов ИЛИ и третий вход третьего элемента И образуют второй управляющий вход-выход блока, вторые входы четвертого и пятого элементов И соединены с выходом второго элемента И, информационные выход Первого регистра и вход второго регистра Соединены с первым информационным входом-выходом блока, а информационные вход первого регистра и выход второго регистра соединены с вторым информационным входом-выходом блока: Блок шифрации информационного слова содержит коммутатор, два регистра и два элемента задержки, причем информационный, адресный и стробирующий входы коммутатора соединены соответственно с адресным, информационным и вторым синхронизирующим входами блока, группа выходов -с соответствующими установочными входами разрядов первого регистра, стробирующий вход которого соединен через первый элемент задержки с первым синхронизирующим входом блока, а информационный выход - с информационным входом второго, регистра, стробирующий вход которого соединен через второй элемент задержки с вторым синхронизирующим входом блока, информационные вход первого регистра и выход второго регистра соединены с информационным входом-выходом блока. На фиг. 1 представлена блок-схема устройства; на фиг. 2-4 временные диаграммы его работы. Устройство (фиг. 1) содержит буферный регистр 1 информации, блок 2 коммутации, а в каждом канале обмена блок 3 сопряжения и блок 4 шифрации информационного слова, управляющую 5 и адресную 6 шины, шину 7 информационного входа-выхода устройства. Буферный регистр 1 информации состоит из регистров 8 и 9 и элемента И 10. Блок 2 коммутации содержит элемент И 1 Г, коммутатор 12 и элемент НЕ 13. Блок 3 сопряжения каждого канала состоит из второго 14 и первого 15 регистров, элементов И 16-20, дешифратора 21 адреса, второго и первого элементов НЕ 22 и 23, формирователей 24 и 25 импульсов и элементов ИЛИ 26 и 27. Блок 4 щифрации информационного слова каждого канала содержит коммутатор 28, регистры 29 и 30 и элементы 31 и 32 задержки. Шинами 5-7 устройство подключается к управляющей вычислительной мащине (УВМ), а шинами 33 и. 34 вторых информационного и управляющего входов-выходов к соответствующим внешним устройствам (ВУ). Устройство работает следующим образом. В начале цикла обмена УВМ выдает на управляющую щину 5 управления команду, определяющую направление передачи информации; на адресную щину 6 адрес (фиг. 2а-4а). ВУ, с которым -будет производиться обмен, признак формата обмена - логический нуль для обмена многозарядным словом фиксированной длины или логическую единицу и номер разряда в слове, если обмен будет производиться отдельным битом-. на шину 7 информационное слово или отдельный бит (фиг. 26 и 46). В блоке 3, соответствующем выставленному адресу, код адреса опознается дешифратором 21. В результате на его выходе появляется логическая единица, которая поступает на входы элементов И 16-18. Признак формата обмена поступает на вход элемента И 19 и через элемент НЕ 23 на вход элемента И 20. При этом в случае обмена словом на выходе элемента И 19 устанавливается логический нуль, а на выходе элемента И 20 - логическая единица, при обмене битом - наоборот. Код номера разряда бита в слове поступает на адресные входы коммутатора 12 и коммутатора 28. При передаче информации из УВМ в ВУ команда (фиг. 2в и 40) поступает на стробирующий вход регистра 8, разрешая прохождение информации через него, а в блоке 3 на второй вход элемента И 17 и с его выхода на входы элементов И 19 и 20. При обмене словом на выходе элемента И 20 будет логическая единица, которая поступает на стробирующий вход регистра 14 и через ИЛИ 27 в ВУ. Для ВУ она является командой к приему информации от УВМ, а для регистра Г4 - разрешением прохождения информации через него. В результате слово из УВМ по шине 7 через регистры 8 и 14 проходит в ВУ. Прием слова ВУ подтверждает сигналом «Ответ (фиг. 2г) который через элемент И 18 проходит в УВМ При обмене битом логическая единица будет на выходе элемента И 19. По ней происходит запуск формирователя 24, длительность .выходного сигнала которого выбирается в зависимости от времени реакции ВУ на команду выдачи им информации. С выхода формирователя 24 сигнал (фиг. 4г) поступает через элемент ИЛИ 26 в ВУ, через элемент 31 задержки на стробирующий вход регистра 29 блока 4 и через элемент НЕ 22 на второй вход элемента И 18. По этому сигналу ВУ выдает слово состояния (фиг. 4д} в регистр 29; регистр 29 принимает это слово, а элемент И 18 блокирует прохождение из ВУ в УВМ сигнала «Ответ (фиг. ж, пунктиром). Время задержки элементом 31 задержки выбирается в зависимости от времени переходных процессов установления данной команды в ВУ. По окончании действия сигнала на выходе формирователя 24 снимается блокировка с элемента И 18 и запускается формирователь 25, длительность выходного сигнала которого выбирается в зависимости от времени реакции ВУ на команду приема им информации. С выхода формирователя 25 сигнал (фиг. 4е) поступает через элемент ИЛИ 27 в ВУ, непосредственно на стробирующий вход коммутатора 28 и через элемент 32 задержки на стробирующий вход регистра 30. По этому сигналу коммутатор 28 выдает бит с фиксированного разряда шины 7 в указанный по шине 6 номер разряда регистра 29, который соответствует логическому значению бита. Для этого младший разряд входа коммутатора 28 соединен с информационной шиной устройства, в результате чего в коммутаторе 28 для каждого логического значения бита устанавливается па- рафазный выход. По окончании выдержки, длительность которой выбирается в зависимости от времени переходных процессов в коммутаторе 28 и регистре 29, сигнал с выхода элемента 32 задержки поступает на стробирующий вход регистра 30, разрешая прохождение слова с измененным битом из регистра 29 в ВУ. Прием измененного слова ВУ подтверждает сигналом «Ответ (фиг. 4ж), который через элемент И 18 по шине 5 поступает в УВМ. На этом цикл обмена по передаче слова или бита из УВМ в ВУ заканчивается. При передаче информации из ВУ в УВМ команда (фиг. 36) из УВМ поступает на первый вход элемента И 10, на первый вход элемента И 11, на второй вход которого подается признак формата обмена, и на второй вход элемента И 16. На выходе элемента И 16 в этом случае будет логическая единица. Поступая через элемент ИЛИ 26 в ВУ, она является для него командой выдачи информации, а поступая на стробирующий вход регистра 15, разрещает прохождение через него информации из ВУ. При обмене словом на выходе элемента И М будет логический нуль. Поступая на стробирующий вход коммутатора 12, он блокирует прохождение слова через него, а поступая через элемент НЕ 13 на второй вход элемента И 10, разрещает прохождение слова (фиг. Зе) с регистра 15 через регистр 9 по шине 7 в УВМ. При обмене отдельным битом на выходе элемента И 11 будет логическая единица. Поступая на стробирующий вход коммутатора 12, она разрещает его работу, а через элемент НЕ 13 и элемент И 10 блокирует регистр 9. После этого коммутатор 12 из поступившего через регистр 15 информа.ционного слова выбирает один бит по номеру (адресу) его в слове и выдает на свой одноразрядный выход, с которого выбранный бит поступает на фиксированный разряд шины 7 и по ней в УВМ. Выдачу слова или бита ВУ сопровождает сигналом «Ответ (фиг. Зг). На этом цикл обмена по передаче слова или бита из ВУ в УВМ заканчивается. Таким образом, устройство при меньших аппаратурных затратах по сравнению с прототипом осуществляет обмен информацией многоразрядными словами и отдельными битами.

I ySM :

L -.f-.

r

фиг.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для обмена | 1976 |

|

SU636603A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-05-07—Публикация

1982-12-24—Подача