Изобретение отн.осится к импульсной технике и может быть использовано в измерительных радиотехнических устройствах преобразования амплитуды коротких одиночных импульсов.

Известен преобразователь, са|держащий N (число уровней квантования) пороговых устройств, выходы которых подключены к входам шифратора 1.

Недостатком данного преобразователя является низкая надежность особенно при большом числе разрядов в выходном коде

- Целью изобрез;ения является повыгаение надежности преобразователя.

Это достигается тем, что в преобразователь-напряжение - код одиночных импульсов, содержащий пороговые блоки и шифратор, введены ли ния задержки, блок управления, ре:.гистр памяти, источник эталонного напряжения, последовательная цепь вычитающих блоков, управляющие входы которых подключены к выходу источника эталонного напряжения. Причем выход последнего вычитающего блока в последовательной цепи вычитающих блоков подключен к входам линии задержки и блока управления, к сигнальному входу каждого вычитающего блока подкл5очен сигнальный вход соответствующего порогового блока, управляющие входы которых соединены с выходом источника эталонного напряжения, а к сигнальному входу первого вычитающего блока, кроме того, подк.шочен выход

to линии задержки, при этом выход бло ка управления подключен к управляющему входу регистра памяти, сигнальный вход которого через шифратор подключен к выходам пороговых бло15ков .

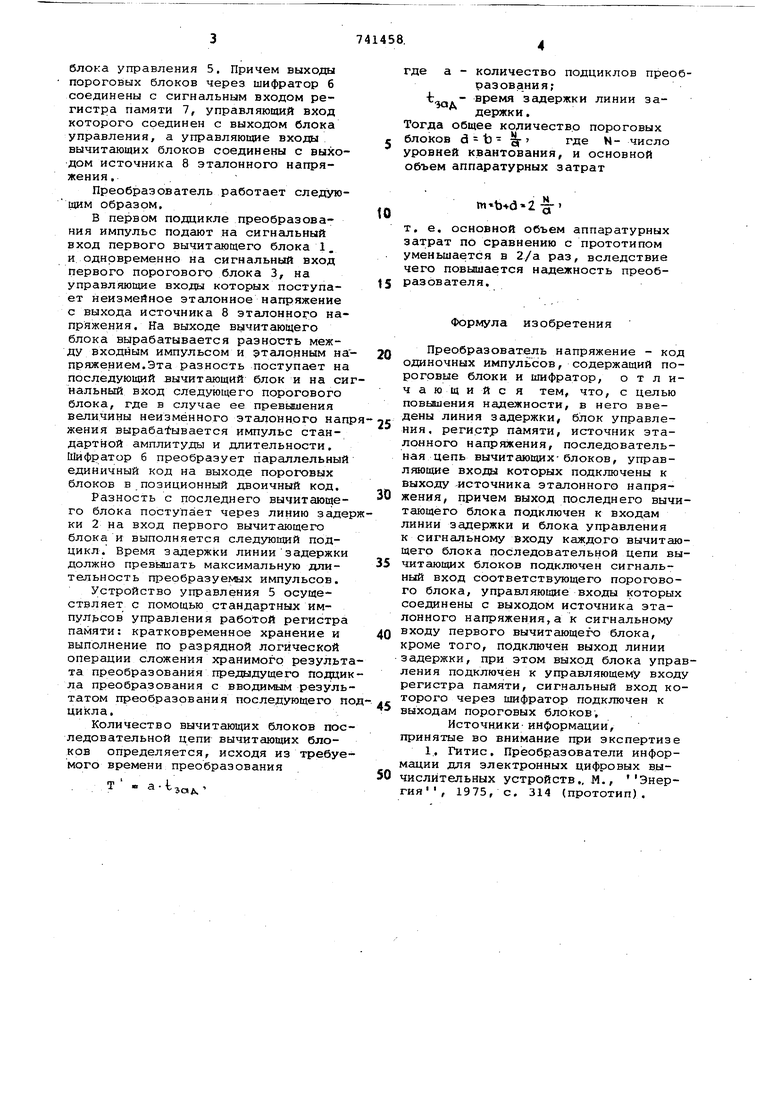

На чертеже приведена функциональная схема лреобразователя напряжение - код одиночных импульсов.

Сигнальный вход первого вычитаю20щего блока 1 являющийся входом преобразователя, соединен с выходом линии задержки 2 и с сигнальным входом первого порогового -блока 3, а выход - с сигнальным входом вто25рого порогового блока и с сигнальным входом второго вычитающего блока и т. д. последовательной цепи 4 вычитающих блоков, выход которой соединен с входами линии задержки и

блока управления 5. Причем выходы пороговых блоков через шифратор б соединены с сигнальным входом регистра памяти 7, управляющий вход которого соединен с выходом блока управления, а управляющие входы вычитающих блоков соединены с выходом источника 8 эталонного напряжения.

Преобразователь работает следующим образом.

В первом подцикле преобразования импульс подают на сигнальный вход первого вычитающего блока 1. и одновременно на сигнальный вход первого порогового блока 3, на управляющие входы которых поступает неизмейное эталонное напряжение с выхода источника 8 эталонного напряжения. На выходе вычитающего блока вырабатывается разность между входным импульсом и эталонным напряжением.Эта разность поступает на последующий вычитающий блок и на синальный вход следующего порогового блока, где в случае ее превьииения величины неизменного эталонного напжения выраба ывается импульс стандартной амплитуды и длительности. Шифратор б преобразует параллельный единичный код на выходе пороговых блоков в позиционный двоичный код.

Разность с последнего вычитающего блока поступает через линию задеки 2 на вход первого вычитающего блока и выполняется следующий поДцикл. Время задержки линиизадержки должно превышать максимальную длительность преобразуемых импульсов. Устройство управления 5 осуществляет с помощью стандартных импульсов управления работой регистра памяти: кратковременное хранение и выполнение по разрядной логической операции сложения хранимого результта преобразования предыдущего подцила преобразования с вводимым результатом преобразования последующего пцикла.

Количество вычитающих блоков последовательной цепи вычитающих блоков определяется, исходя из требуемого времени преобразования

ч . аЧэад

где а - количество подциклов преобразования;t. - время задержки линии за держки.

Тогда общее количество пороговых блоков d b - где N- число уровней квантования, и основной объем аппаратурных затрат

m bd-Z- т. е. основной объем аппаратурных затрат по сравнению с прототипом уменьшается в 2/а раз, вследствие чего повышается надежность преобразователя.

Формула изобретения

Q Преобразователь напряжение - код одиночных импульсов, содержащий пороговые блоки и шифратор, о т л ич а ю щ и и с я тем, что, с целью повьваения надежности, в него введены линия задержки, блок управления, регистр памяти, источник эталонного напряжения, последовательная цепь вычитающих-блоков, управляющие входы которых подключены к выходу источника эталонного напряжения, причем выход последнего вычитающего блока подключен к входам линии задержки и блока управления к сигнальному входу каждого вычитающего блока последовательной цепи вычитающих блоков подключен сигнальный вход соответствующего порогового блока, управляющие входы которых соединены с выходом источника эталонного напряжения,а к сигнальному

Q входу первого вычитающего блока, кроме того, подключен выход линии задержки, при этом выход блока управления подключен к управляющему входу регистра памяти, сигнальный вход которого через шифратор подключен к выходам пороговых блоков.

Источники-информации, принятые во внимание при экспертизе 1.. Гитис. Преобразователи информации для электронных цифровых вычислительных устройств., М., Энергия, 1975, с. 314 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| ПРЕОБРАЗОВАТЕЛЬ ВРЕМЯ-КОД | 2005 |

|

RU2303803C2 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 2011 |

|

RU2450447C1 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 2014 |

|

RU2563145C1 |

| АВТОМАТИЗИРОВАННОЕ УСТРОЙСТВО КОНТРОЛЯ И ДИАГНОСТИРОВАНИЯ РАДИОЭЛЕКТРОННЫХ ИЗДЕЛИЙ | 1998 |

|

RU2174699C2 |

| Логарифмический преобразователь амплитуды одиночных импульсов | 1980 |

|

SU898449A1 |

| ИНТЕРПОЛИРУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ВРЕМЯ-КОД | 2008 |

|

RU2385479C2 |

| Аналого-цифровой преобразователь | 1980 |

|

SU938396A1 |

| Устройство для приема и градиентного декодирования избыточных сигналов | 1983 |

|

SU1152016A1 |

Авторы

Даты

1980-06-15—Публикация

1978-10-24—Подача