(54) ЛОГАРИФМИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ АМПЛИТУДЫ ОДИНОЧНЫХ И: 111УЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь напряжения-код одиночных импульсов | 1978 |

|

SU741458A1 |

| Логарифмический преобразователь амплитуды одиночных импульсов | 1978 |

|

SU694870A1 |

| РЕЦИРКУЛЯЦИОННЫЙ ПРЕОБРАЗОВАТЕЛЬ ВРЕМЯ-КОД | 2008 |

|

RU2393519C1 |

| Устройство для сжатия информации | 1986 |

|

SU1336080A1 |

| Вычислительное устройство для первичной обработки информации | 1978 |

|

SU746604A1 |

| Приемник М-ичных дискретных сигналов | 1987 |

|

SU1497746A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1181144A1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

| Логарифмический аналого-цифровой преобразователь | 1982 |

|

SU1084825A1 |

| СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ ПО РАДИОКАНАЛАМ ИМПУЛЬСНО-ФАЗОВОЙ РАДИОНАВИГАЦИОННОЙ СИСТЕМЫ | 1994 |

|

RU2079855C1 |

I

Изобретение относится к преобразователям импульсных логарифмических сигналов по логарифмическому закону и может быть использовано в аналоговых вычислительных машинах.

Известен функциональный преобразователь напряжения, содержащий делители напряжения, источник опорного напряжения, пороговые блоки, шифратор 1.

Однако устройство характеризуется узкими функциональными возможностями.

Наиболее близким к предлагаемому является логарифмический преобразователь амплитуды одиночных импульсов, содержащий пороговый блок, делители напряжения, блок задержки, источник опорного напряжения, шифратор, регистр памяти 2.

Недостатком этого устройства является низкое быстродействие.

Цель изобретения - повьш1ение быстродействия .

Поставленная цепь достигается тем, что в известный логарифмически преобразователь амплитуды одиночных импульсов, содержащий соединенные последовательно И делителей напряжения, пороговый блок, блок задержки, источник опорного напряжения, соединенные последовательно шифратор и регистр памяти, вход первого из И делителей напряжения является входом логарифмического преобразователя амплитуды одиночных импульсов, к выходу делителя напряжения подключен вход блока задержки, выход которого соединен со входом первого из И делителей напряжения, выход источника опорного напряжения подключен к первому входу порогового блока, выход которого соединен со входом нифратора, введены п-1 дополнительных пороговых блоков, первые входы которых соединены с выходом источника опорного напряжения, второй вход порогового блока подключен к выходу

первого из И делителей напряжения, второй вход каядогс из Y}- дополнительных пороговых блоков соединен с выходом соответствующих П делителей напряжения, кроме первого выходы h-1 дополнительных пороговых блоков подключены к соответствующим входам шифратора.

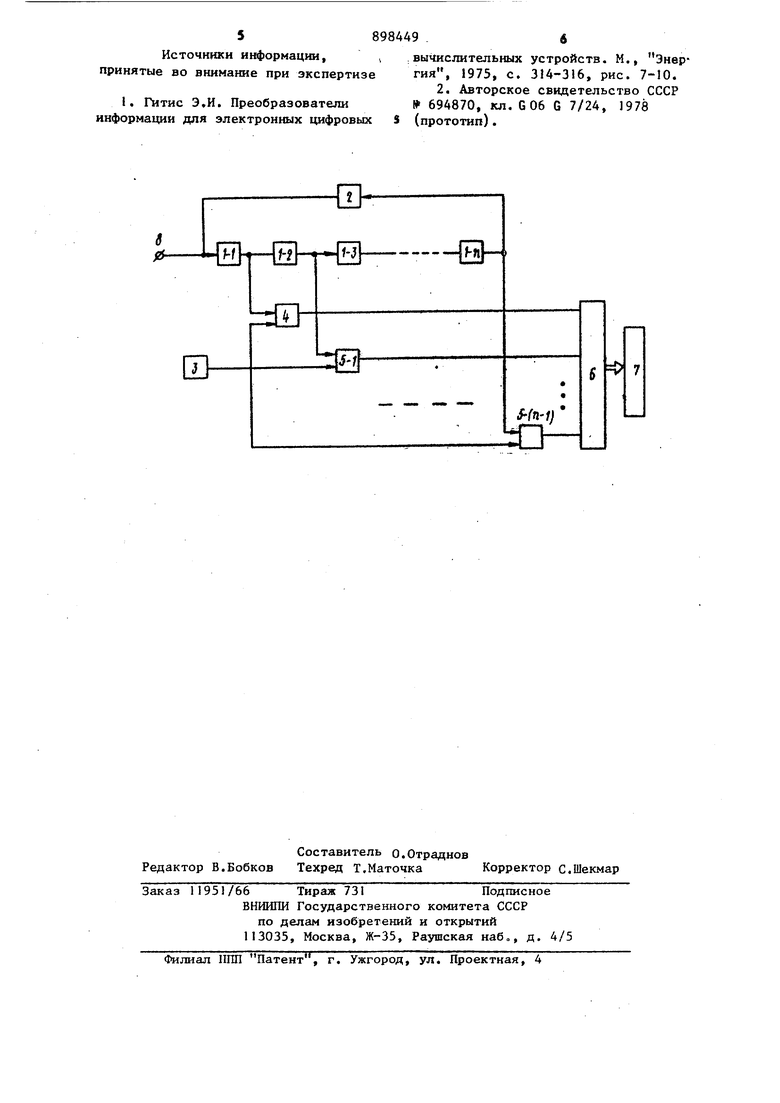

На чертеже изображена функциональная схема логарифмического преобразователя амплитуды одиночных импульсов.

Устройство содержит делители напряжения 1-1, 1-2, 1-3,... 1-У), блок задержки 2, источник 3 опорного напряжения , пороговый блок 4, дополнительные пороговые блоки 5-1.,..5-(п-1), шифратор 6, регистр памяти 7, вход 8 логарифмического преобразователя амплитуды одиночных импульсов. Логарифмический преобразователь амплитуды одиночных импульсов работает следующим образом.

На вход 8 поступает одиночный импульс . На выходах делителей напряжения 1-1, 1-2, 1-3, ... 1-Л фop Q pз oтся импульсы, амшштуда которых пропорциональна соответственно на выходе первого из их коэффициенту передачи, на выхо второго - произведению коэффициента передачи первого и второго делителей напряжения 1-1 и 1-2 и т.д. На выходе последнего делителя напряжения 1-h эта амплитуда пропорциональна произведению коэффициентов передачи предшествукяцих делителей напряжения (в случае равенства этих коэффициентов пропорциональна п-ой степени коэффициента передачи). В случае превышения амплитуды выходного напряжения делителей напряжения 1-1,..,1-Я величины напряжения источника 3 опорного напряжения пороговые блоки 4, 5-1, ...5-(п-1) формируют сигналы. С выхода последнего делителя напрякения 1-П сигнал поступает на вход блока задержки 2. Время задержки должно быть выбрано больше длительности преобразуемых импульсо, а коэффициент затухания минимальным С выхода блока задержки 2 сигнал поступает на вход первого делителя напряжения 1-1. Начинается следующий цикл преобразования. Шифратор 6 преобразует параллельный единичный код с выходов пороговых блоков, 4,5-1...5-(п-1) в позиционный двоичный код. Регистр памяти 7 осуществляет кратковременное хранение и выполнение поразрядной логической операции сложения храннмого результата предьщущего цикла с вводимым результатом последующего цикла.

Результат преобразования равен

Uv

nogr

hn u

где и - величина напряжения источника опорного напряжения 3J

и, величина амплитуды импульса на входе 8;

коэффициент передачи деликтелей напряжения I-1, -2,...1-м.

Предложенный логарифмический преобразователь амплитуды одиночных импульсов характеризуется более высоким быстродействием.

Формула изобретения

Логарифмический преобразователь амплитуды одиночных импульсов, содер - агд1й соединеннь}е последовательно У1 делителей напряжения, пороговый блок, блок задержки, Источник опорного напряжения, соединенные последовательно шифратор и регистр памяти, вход первого из h делителей напряжения является входом логарифмического преобразователя амплитуды одиночных импульсов, к выходу И-го делителя напряжения подключен вход блока задержки, выход которого соединен со входом первого из И делителей напряжения, выход источника

опорного напряжения подключен к первому входу порогового блока, выход которого соединен со входом шифратора, отличающийся тем,

5 что, с целью повышения быстродействия, в него введены h-l дополнительных пороговых блоков, первые входы которых соединены с выходом источника опорного напряжения, втоO рой вход порогового блока подключен к выходу первого из И делителей напряжения, второй вход каждого из П-1 дополнительных пороговых блоков соединен с выходом соответствующих ц делителей напряжения, кроме первого, выходы дополнительных пороговых блоков подключены к соответствующим входам шифратора.

Источники информации, принятые во внимание при экспертизе

I. Гитис Э,И. Преобразователи информации для электронных цифровых

,вычислительных устройств. М., Энергия, 1975, с. 3J4-316, рис. 7-10. 2. Авторское свидетельство СССР 694870, кл. G06 G 7/24, 1978 (прототип).

ИП1)

Авторы

Даты

1982-01-15—Публикация

1980-05-14—Подача