1

Изобретение относится к вычисли.тельной технике и может быть использовано в электронных цифровых вычислительных машинах (ЭЦВМ) при построении регистрового поля процессора.

Известно устройство для обработки информации, обладающее высокой скоростью параллельных пересылок информации между любыми словами регистровой памяти l .

Однако устройство не позволяет пересылать информацию между любьлми частями регистров (байтами).

Известно также устройство для обработки информации, обеспечивающее широкие возможности пересылок между регистрами и другими блоками процессора за счет специальной организации регистровой памяти, коммутирующего . оборудования и системы шин 2.

Недостаток данного устройства - невысокая скорость обработки (пересылок ) информации.

Наиболее близким по технической сущности к предлагаемому является устройство, используемое в качестве регистрового поля процессора передачи данных и содержащее регистры операционного поля, выходы которых соединаны с первой группой входов коммутатора полуслов, выход которого соединен с первым 1выходом устройства, регистровую память., коммутатор записи, выход которого соединен со входами регистров операционного поля, а первый и второй входы являющихся, соответственно, первым и вторым входами устройства, коммутатор опера10тивной памяти, регистр команд,выход которого подключен ко второй группе входов коммутатора полуслов и третьему входу кс 1мутатора записи, блок управления, первый вход которого

15 является пятым входом устройства, а выходы - к управляющим входам регистра команд, коммутаторов записи, памяти, полуслов, и регистров операционного поля з .

20

Недостатками указанного устройства являются необходимость введения дополнительного накопителя для работы в автономном режиме (при отсутствии оперативных запоминающих устройств)р невысокая скорость и ограниченные возможности пересылок между регистрами операционного поля и регистровой памяти вследствие

30 того, что данные пересылки выполняются через специальные промежутбчные регистры адреса памяти и слов

Цель изобретения - повышение сксрости обработки информации.

Поставлецная цель достигается тем что в устройство введен коммутатор слов, первая группа входов которого соединена с первой группой входов регистра полуслов и выходами регистров операционного поля, вторая группа входов соединена с выходами регис(гров регистровой памяти, третий вхор соединен с выходом регистра команд, четвертый вход соединен с выхЬдом блока управления, а выход коммутатора является третьим выходом устройства и соединен с четвертым входом коммутатора оперативной памяти И четвертым и пятым входом коммутатЬра записи, выход которого соединен с третьим входом коммутатора оперативной памяти, выход которого соединен со входами регистров регистровой памяти, того , введен буфер полуслова, первый вход которого соединен с выходой коммутатора полуслов, второй вхс|я - с выходом блока управления, а в|ыход подключен к шестому входу коймутатс а записи.

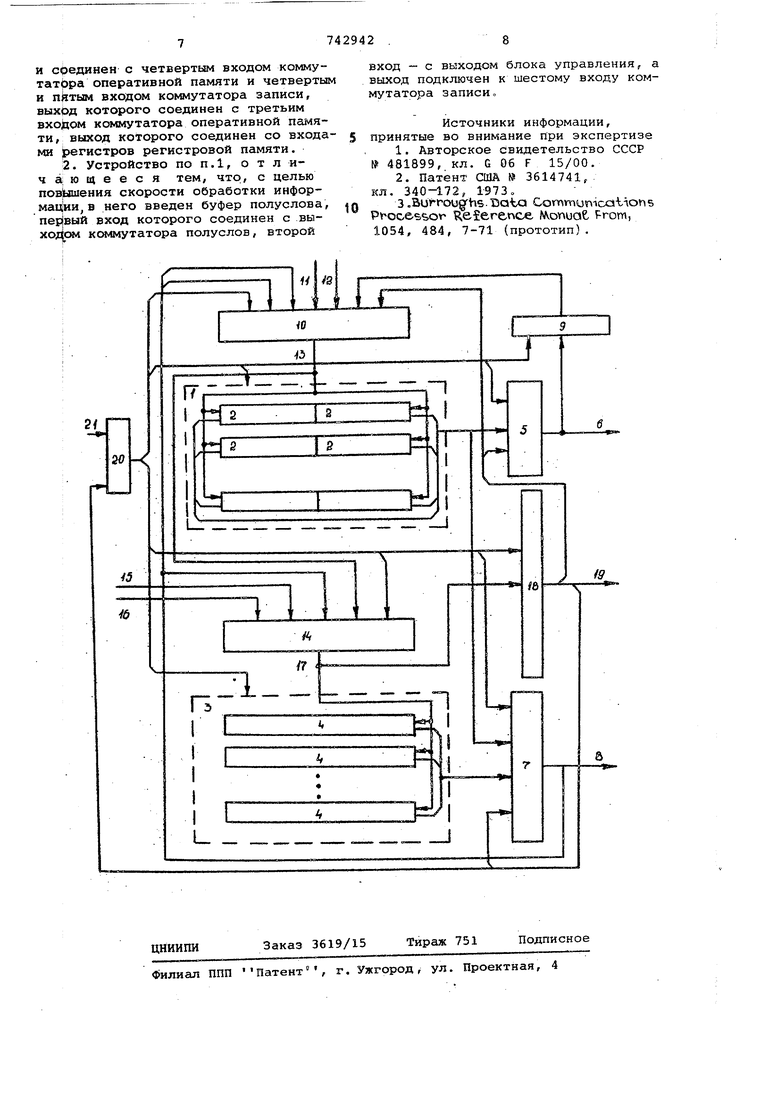

На чертеже представлена структурна} схема предложенного устройства,

Устройство содержит регистры 1 операционного поля, объединенные в m .полуслов 2 и включающие основные программно доступные (адресуемые непосредственно или по умолчанию. командами (ЦВМ) регистры процессора такие, как регистр номера команды, регистр адреса памяти, индексные регистры, регистры косвенных адресов рег-истры управляквдих триггеров и регистровую память 3, объеди немную.в 8 слов 4, предназначенную для кранен5гя операндов и результато к сгодержаэдую, в том числе f регистр обмена с оперативными запоминакнцими устройствами; коммутатор 5 полуслов предназначенный для выборки любого полуслова из регистров операционног поля или буквального операнда из региетра команд в шину б полуслова; коммутатор 7 слов, предназначенный дли выборки любого слова из регистрвой памяти с любого полуслова из регистров операционного поля или буквального операнда из регистра команд в шину 8 слова, буфер 9 полуслбЬа, предназначенный для временHot .хранения полусловаf выбранного в шину б; коммутатор 10 записи, предназначенный для выборки правого или левого полуслова и слова, выбранного в шину 8, содержимого буфера 9 полуслова, буквального операнд из регистра команд, входных шин 11 или 12, по которым приходит информация от исполнительных блоков или внешних устройств ЭЦВМ соответственни в шину 13 записи; коммутатор 14 оперативных запоминающих устройств, предназначенный для выборки слова, выбранного в шину 8, полуслова, выбранного в шину 13 записи слова из входных шин 15 или 16, по которым приходит информация из центрального или местного оперативного запом1 нающего устройства соответственно в шину 17 записи регистровой памяти; регистр 18 команд, предназначенный для хранения команд, обрабатываемк х процессором и выбираемых как из оперативных запоминающих устройств, так и из регистровой памяти,выход которого связан шиной 19 с устройством управления продессора (на чертеже не показано); блок 20 управления, вход которого является пятым входом устройства.и связан шиной 21 с устройством управления процессора и предназначенный управления всеми регистрами и коммутаторами устройства.

Минимальной единицей информации, обрабатываемой устройством, является байт. Каждое полуслово 2 регистров 1 операционного поля содержит К байтов и каждое слово 4 регистровой памяти - 2 К байтов, 8, 15, 16 и 17 имеют разрядность слова, а шины 6,11,12 и 13 - полуслова. Все эти шины могут также нести группу байтов. Под группой байтов понимается произвольное количество (от одног до к) значимых байтов одного полуслова, прижатых к правой границе полуслва,

В шину 6 выбирается группа байтов поступаняцая на исполнительные блоки процессора, в оперативные запоминающие устройства или на буфер 9, В шину 8 выбирается группа байтов, поступаншая в регистры 1 или память 3,слово, поступакяцее в оперативные запоминаквдие устройства, причем группа (полуслово) регистров 1, выбирается в правое полуслово слова шины 8« Шина 13 поступаетна все полуслова 2, Если шины 11 и 12 содержат один байт то он коммутируется во все байтк шины 13, Шина 17 поступает на все слова 4, причем полуслово шины 13 поступает на правое и на левое полуслово слова шины 17. Блок 20 управления в зависимости от управляющих сигналов в шине 21 и адресов операндов, поступакадих из регистра 18 команд, может осуществлять запись в любую группу байтов регистров 1 или регистровой памяти 3, в любое слово регистровой памяти 3, в регистр 18 команд и буфер 9, и позволяет коммутировать любой вход коммутаторов 5,7,10 и 14,

Устройство работает следукидим образом,

В режиме работы с оперативными запоминающими устройствами команды

выбираются на регистр 18 команд по 15 или 16 через коммутатор 14 и ШИК/ 11с Данные из оперативных запомйнаЕ я4их устройств выбираются по тем же информационным путям, но приемником информации является регистр обмена, включенный в организацию регистровой памяти 3.

Для осуществления автономного режима работы устройства, необходимого для отладочных и диагностических работ, происходит начальная загрузка команд в регистровую память 3, а также данных в регистры 1 и память 3 из внешних устройств по шине 12 через коммутаторы 10 и 14. В данном режиме команды выбираются через коммутатор 7 и в шину 8 и далее через коммутатор 14 на регистр 18 команд для последующего выполнения.

Для пересылок между словами 4 используется аналогичный механизм с той разницей, что приемник пересылаемой информации один иjэ регистро памяти 3.

Для пересылок любой группы байтов последняя выбирается из регистров 1 или из памяти 3 через коммутатор 7 в шину 8 слова и далее через коммутатор 10 в шину 13 записи, причем в зависимости,от адресов источника и приемника информации в шину 13 выбирается правое или левое полуслово ИЗ слова, выбранного в шину 8, Скоммутированная в шину 13 группа байтов поступает на все полуслова 2 или через коммутатор 14 на все полуслова слов 4.

Пересылка группы байтов может осуществляться также через буфер полуслова 9, если группа - источник размегцена в регистрах, В этом случае с помощью коммутатора 5 в шину б выбирается любая группа из регистров Д, поступакицая затем в буфер 9. содержимое буфера 9 через коммутаторы 10 и 14 записывается в любой регистр операционного поля 1 или регистровой памяти 3. .

Наличие коммутаторв 5,7,10 и 14 позволяет осуществлять одновременную выборку двух операндов по шинам 6 и 8, одновременную запись результата по шине 11, что повышает скорость выполнения команд процессора.

Введение коммутатора слов и расширение функций коммутатора записи и коммутатора оперативньЕх запоминающих устройств позволяет по сравнению с . известным вдвое сократить количество команд при пересылках между произвольными регистрами устройства,что вдвое повышает скорость обработки информации данным устройством

Действительный выигрыш времени обработки информации зависит от характера программ, выполняемых процессором, а конкретно, от доли команд типа пересылок между регистрами в математическом обеспечении, которая для разрабатываемого процессора составляет в среднем 10%.Кроме того, наличие общего коммутатора для выборки, как команд, так и данных из оперативных запоминающих устройств и регистровой памяти позволяет без . дополнительного оборудования осуществить автономный режим работы.

Введениебуфера полуслова позволяет осуществить временное хранение и последующее восстановление содержимого регистров операционного поля, не занимая программно-доступных регистров.

Формула изобретения

1. Устройство для обработки ин0фррмации, содержащее регистры операционного поля, выходы которых соединены с первой группой входов коммутатора полуслов, выход которого соединен с первым выходом устройства,

5 регистровую память, коммутатор записи, выход которого соединен со входом регистров операционного поля, а первый и второй входы являются, соответственно, первым и вторым вхо0дами устройства, коммутатор оперативной памяти, первый и второй входы которого являются, соответственно, третьим и четвертым входом устройства, регистр команд, выход которого является вторым выходом устройства . и подключен ко второй группе входов коммутатора полуслов и третьему входу коммутатора записи, выход регистра команд соединен с выходом коммутато0ра оперативной памяти, блок управления, первый вход которого является пятым входом устройства, второй вход подключен к выходу регистра команд, а выходы соответственно, к

5 правлякяцим входам регистров операционного поля, коммутатора полуслов, регистровой памяти, коммутатора записи, коммутатора оперативной памяти, регистра команд, отличающееся тем, что, с целью

0 повышения скорости обработки инфор мации,в устройство введен коммутатор слов, первая группа входов которого соединена с первой группой входов регистра полуслов и

5 выходами регистров операционного поля, вторая группа выходов первой группой входов регистра полуслов и выходами регистров операционного поля, вторая группа выходов

р соединена с выходами регистров регистровой памяти, третий вход соединен с выходом регистра команд, четвертый вход соединен с выходом блока управления, а выход коммутатора

5 является третьим выходом устройства

и соединен с четвертым входом коммутатрра оперативной памяти и четвертым и пМтым входом коммутатора записи, выход которого соединен с третьим входом коммутатора оперативной Пс1мяти, выход которого соединен со входами регистров регистровой памяти.

2. Устройство по п.1, отличающееся тем, что, с целью пов ышения скорости обработки информа1ф1и, в него введен буфер полуслова, первый вход которого соединен с выxoj cM коммутатора полуслов, второй

вход - с выходом блока управления, а выход подключен к шестому входу коммутатора записи о

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 481899, кл. G 06 F 15/00.

2.Патент США № 3614741, кл. 340-172, 1973.

З.Ви гоидгЬв.ТЗаЪа CommumcxatiohB P ocesbor Reference f onuat Prom, 1054, 484, 7-71 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки информации | 1981 |

|

SU993262A1 |

| Устройство для обработки данных переменной длины | 1986 |

|

SU1675897A1 |

| Устройство для распаковки команд | 1981 |

|

SU972507A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| СРЕДСТВО РАЗДЕЛЕННОЙ ЗАГРУЗКИ/СОХРАНЕНИЯ И КОМАНДА ДЛЯ НЕГО | 2010 |

|

RU2554546C2 |

| УВЕЛИЧЕНИЕ ЧИСЛА ДОСТУПНЫХ ДЛЯ КОМАНД РЕГИСТРОВ ОБЩЕГО НАЗНАЧЕНИЯ | 2010 |

|

RU2562430C2 |

| Устройство для обработки данных | 1978 |

|

SU736106A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Микропрограммный процессор | 1978 |

|

SU744587A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

Авторы

Даты

1980-06-25—Публикация

1977-09-21—Подача